Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

SSE инструкции

Содержание

- 1. SSE инструкции

- 2. MMX (Multimedia Extensions — мультимедийное расширение) —

- 3. SSE включает в архитектуру процессора восемь 128-битных

- 4. SSE2 использует восемь 128-битных регистров (xmm0 до

- 5. SSE3 (PNI — Prescott New Instruction) —

- 6. SSE4 это набор команд Intel Core микроархитектуры,

- 7. SSE4.1 это расширенный набор команд SSE4 от

- 8. SSSE3 (Supplemental Streaming SIMD Extension 3) —

- 9. 3DNow! — дополнительное расширение MMX для процессоров

- 10. Проверка поддержки 3DNow! процессором. Перед

- 11. AMD64 (также x86-64/Intel64/EM64T/x64) — 64-битная архитектура микропроцессора

- 12. Архитектура x86_64 имеет: - 16 целочисленных

- 13. Проверка поддержки инструкции CPUID процессором:

- 14. Использование CPUID: Инструкция CPUID по

- 15. ASCii-строка HEX-значения EBX:EDX:ECX Название производителя

- 16. EM64T (Extended Memory 64 Technology) - реализация

- 17. Скачать презентанцию

MMX (Multimedia Extensions — мультимедийное расширение) — коммерческое название дополнительного набора инструкций, выполняющих характерные для процессов кодирования/декодирования потоковых аудио/видео данных действия за одну машинную инструкцию. Впервые появился в процессорах Pentium MMX.

Слайды и текст этой презентации

Слайд 1Процессорные инструкции.

В современных процессорах инструкции используются для ускорения работы и

Слайд 2MMX (Multimedia Extensions — мультимедийное расширение) — коммерческое название дополнительного

набора инструкций, выполняющих характерные для процессов кодирования/декодирования потоковых аудио/видео данных

действия за одну машинную инструкцию. Впервые появился в процессорах Pentium MMX. Разработан в лаборатории Intel в Хайфе, Израиль, в первой половине 1990-х.SIMD (англ. Single Instruction, Multiple Data) — принцип компьютерных вычислений, позволяющий обеспечить параллелизм на уровне данных.

SSE (англ. Streaming SIMD Extensions, потоковое SIMD-расширение процессора) — это SIMD (англ. Single Instruction, Multiple Data, Одна инструкция — множество данных) набор инструкций, разработанный Intel, и впервые представленный в процессорах серии Pentium III как ответ на аналогичный набор инструкций 3DNow! от AMD, который был представлен годом раньше. Первоначально названием этих инструкций было KNI что расшифровывалось как Katmai New Instructions (Katmai — название первой версии ядра процессора Pentium III). Технология SSE позволяла преодолеть 2 основных проблемы MMX — при использовании MMX невозможно было одновременно использовать инструкции сопроцессора, так как его регистры использовались для MMX и работы с вещественными числами.

Слайд 3SSE включает в архитектуру процессора восемь 128-битных регистров (xmm0 до

xmm7), каждый из которых трактуется как 4 последовательных значения с

плавающей точкой одинарной точности. SSE включает в себя набор инструкций, который производит операции со скалярными и упакованными типами данных. Преимущество в производительности достигается в том случае, когда необходимо произвести одну и ту же последовательность действий над разными данными. Реализация блоков SIMD осуществляется распараллеливанием вычислительного процесса между данными. То есть когда через один блок проходит поочерёдно множество потоков данных.SSE2 SSE2 (англ. Streaming SIMD Extensions 2, потоковое SIMD-расширение процессора) — это SIMD (англ. Single Instruction, Multiple Data, Одна инструкция — множество данных) набор инструкций, разработанный Intel, и впервые представленный в процессорах серии Pentium 4.

Слайд 4SSE2 использует восемь 128-битных регистров (xmm0 до xmm7), включённых в

архитектуру x86 с вводом расширения SSE, каждый из которых трактуется

как 2 последовательных значения с плавающей точкой двойной точности. SSE2 включает в себя набор инструкций, который производит операции со скалярными и упакованными типами данных. Также SSE2 содержит инструкции для потоковой обработки целочисленных данных в тех же 128-битных xmm регистрах, что делает это расширение более предпочтительным для целочисленных вычислений, нежели использование набора инструкций MMX, появившегося гораздо раньше. Преимущество в производительности достигается в том случае, когда необходимо произвести одну и ту же последовательность действий над большим набором однотипных данных.Слайд 5SSE3 (PNI — Prescott New Instruction) — третья версия SIMD-расширения

Intel, потомок SSE, SSE2 и x87. Впервые представлено 2 февраля

2004 года в ядре Prescott процессора Pentium 4. В 2005 AMD предложила свою реализацию SSE3 для процессоров Athlon 64 (ядра Venice и San Diego). Набор SSE3 содержит 13 инструкций: - FISTTP (x87) - MOVSLDUP (SSE) - MOVSHDUP (SSE) - MOVDDUP (SSE2) - LDDQU (SSE/SSE2) - ADDSUBPD (SSE) - ADDSUBPD (SSE2) - HADDPS (SSE) - HSUBPS (SSE) - HADDPD (SSE2) - HSUBPD (SSE2) - MONITOR (нет аналога в SSE3 для AMD) - MWAIT (нет аналога в SSE3 для AMD).Слайд 6SSE4 это набор команд Intel Core микроархитектуры, впервые реализованный в

процессорах серии Penryn (не следует путать с SSE4A от AMD).

Он был анонсирован 27 Сентября 2006, однако детальное описание стало доступно только весной 2007. SSE4 состоит из 54 инструкций, 47 из них относят к SSE4.1 (они есть только в процессорах Penryn). Ожидается, что полный набор команд (SSE4.1 и SSE4.2, то есть 47 + оставшиеся 7 команд) будет доступен в процессорах Nehalem. Ни одна из SSE4 инструкций не работает с 64-х битными mmx регистрами (только с 128-ми битными xmm0-15). Компилятор языка Си от Intel начиная с версии 10 генерирует инструкции SSE4 при задании опции -QxS. В SSE4 добавлены инструкции, ускоряющие компенсацию движения в видеокодеках, быстрое чтение из WC памяти, множество инструкций для упрощения векторизации программ компиляторами. Впервые в SSE4 регистр xmm0 стал использоваться как неявный аргумент для некоторых инструкций.Слайд 7SSE4.1 это расширенный набор команд SSE4 от Intel. Ниже приведены

инструкции, входящие в SSE4.1: - Ускорение видео (3 инструкции) -

Векторные примитивы (5 инструкций) - Вставки/извлечения (4 инструкции) - Скалярное умножение векторов (2 инструкции) - Смешивания (4 инструкции) - Проверки бит - Округления (2 инструкции) - Чтение WC памятиSSE4.2 состоит из 7 инструкций. - Обработка строк (4 инструкции) - Подсчет CRC32 - Подсчет популяции единичных бит - Векторные примитивы

SSE4A это расширенный набор команд SSE4 от AMD, разработанный скорее не как дополнение, а как альтернатива инструкциям SSE4 от Intel.

Слайд 8SSSE3 (Supplemental Streaming SIMD Extension 3) — это обозначение данное

Intel 4-му расширению системы команд. Предыдущее имело обозначение SSE3 и

Intel добавил ещё один символ 'S' вместо того, чтобы увеличить номер расширения, возможно потому, что они посчитали SSSE3 простым дополнением к SSE3. Часто, до того как стало использоваться официальное обозначение SSSE3, эти новые команды назывались SSE4. Также их называли кодовыми именами Tejas New Instructions (TNI) и Merom New Instructions (MNI) по названию процессоров, где впервые Intel намеревалась поддержать эти новые команды. Появившись в Intel Core Microarchitecture, SSSE3 доступно в сериях процессоров Xeon 5100 (Server и Workstation версии), а также в процессорах Intel Core 2 (Notebook и Desktop версии). Новыми в SSSE3, по сравнению с SSE3, являются 16 уникальных команд, работающих с упакованными целыми. Каждая из них может работать как с 64-х битными (MMX), так и с 128-ми битными (XMM) регистрами, поэтому Intel в своих материалах ссылается на 32 новые команды. Вот некоторые из них: - Работа со знаком (2 инструкции) - Сдвиги - Перемешивание байт - Умножения (2 инструкции) - Горизонтальные сложения/вычитания целых (4 инструкции)Слайд 93DNow! — дополнительное расширение MMX для процессоров AMD, начиная с

AMD K6 3D. Причиной создания 3DNow! послужило стремление завоевать превосходство

над процессорами производства компании Intel в области обработки мультимедийных данных. Хотя это расширение является разработкой AMD, его также интегрировали в свои процессоры IBM, Cyrix и другие. Технология 3DNow! ввела 21 новую команду процессора и возможность оперировать 32-битными вещественными типами в стандартных MMX-регистрах. Также были добавлены специальные инструкции, оптимизирующие переключение в режим MMX/3DNow! (femms, которая заменяла стандартную инструкцию emms) и работу с кешем процессора. Таким образом технология 3DNow! расширяла возможности технологии MMX, не требуя введения новых режимов работы процессора и новых регистров. В 3DNow! компания AMD добавила новый тип данных — 32-битные вещественные числа, инструкции для работы с этим типом, а также некоторые инструкции для манипулирования стандартными типами MMX.Слайд 10Проверка поддержки 3DNow! процессором. Перед началом работы с расширением 3DNow!

следует убедиться, что ЦП их поддерживает. Для этого используется инструкция

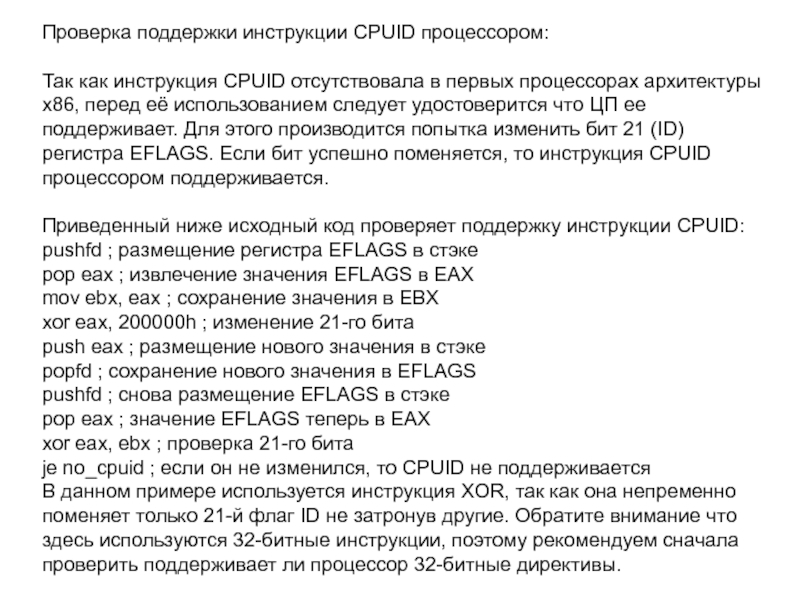

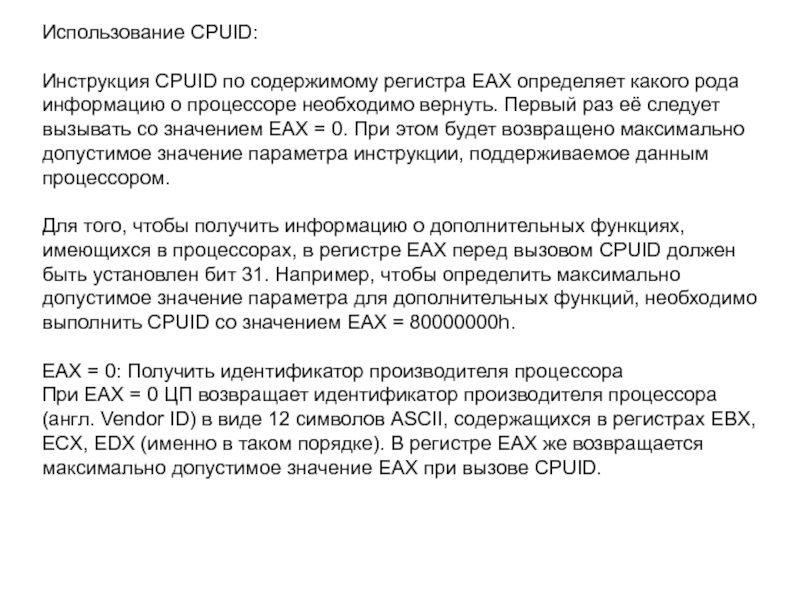

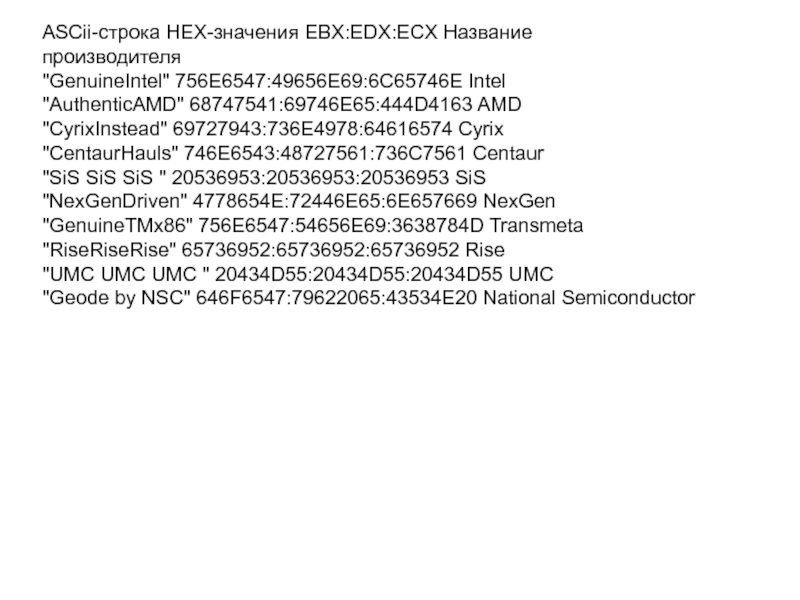

CPUID. Общий порядок действий при проверке выглядит следующим образом: 1. Убедиться, что процессор поддерживает инструкцию CPUID. Если нет, то ЦП не поддерживает и 3DNow!. 2. Выполнить инструкцию cpuid со значением EAX = 0 — это необходимо для следующего шага. 3. Выполнить CPUID со значением EAX = 80000000h. Если после выполнения инструкции в EAX будет значение меньше 1, то 3DNow! не поддерживается. 4. Выполнить CPUID с EAX = 80000001h. Если после выполнения бит 31 регистра EDX будет установлен в 1, то 3DNow! поддерживается. Иначе — нет.Слайд 11AMD64 (также x86-64/Intel64/EM64T/x64) — 64-битная архитектура микропроцессора и соответствующий набор

инструкций, разработанные компанией AMD. Это расширение архитектуры x86 с полной

обратной совместимостью. Набор инструкций x86-64 в настоящее время поддерживается процессорами AMD Athlon 64, Athlon 64 FX, Athlon 64 X2, Turion 64, Opteron, последними моделями Sempron. Интересно, что этот набор инструкций был поддержан основным конкурентом AMD — компанией Intel под названием Intel 64 (ранее известные как EM64T и IA-32e) в поздних моделях процессоров Pentium 4, а также в Pentium D, Pentium Extreme Edition, Celeron D, Core 2 Duo и Xeon. Корпорации Microsoft и Sun Microsystems используют для обозначения этого набора инструкций термин x64.Особенности архитектуры: Разработанный компанией AMD набор инструкций x86-64 (позднее переименованный в AMD64) — расширение архитектуры Intel IA-32 (x86-32). Основной отличительной особенностью AMD64 является поддержка 16-ти 64-битных регистров общего назначения (против 8-и 32-битных в x86-32), 64-битных арифметических и логических операций над целыми числами и 64-битных виртуальных адресов. Для адресации новых регистров для команд введены так называемые «префиксы расширения регистра», для которых был выбран диапзон кодов 40h-4Fh, использующихся для команд INC <регистр> и DEC <регистр> в 32- и 16-битных режимах.