Слайд 1Алгоритм Тамасуло

Разработан в компании IBM в начале 80-ых годов.

Первоначально использовался

в вещественном сопроцессоре IBM 360/92.

Это алгоритм динамического планирования инструкций, позволяет

исполнять инструкции в порядке отличном от программного.

При одновременном исполнении двух и более инструкций позволяет разрешить RAW, и устранить WAR и WAW конфликты

Слайд 2Алгоритм Тамасуло

Разрешение конфликтов RAW происходит за счет запуска инструкции, только

когда готовы ее операнды.

Устранение WAR и WAW конфликтов происходит за

счет переименования регистров с использованием станций резервирования (Reserve Station).

RS используются для хранения операндов инструкции и воссоздания графа зависимостей по данным между инструкциями, которые находятся в исполнении.

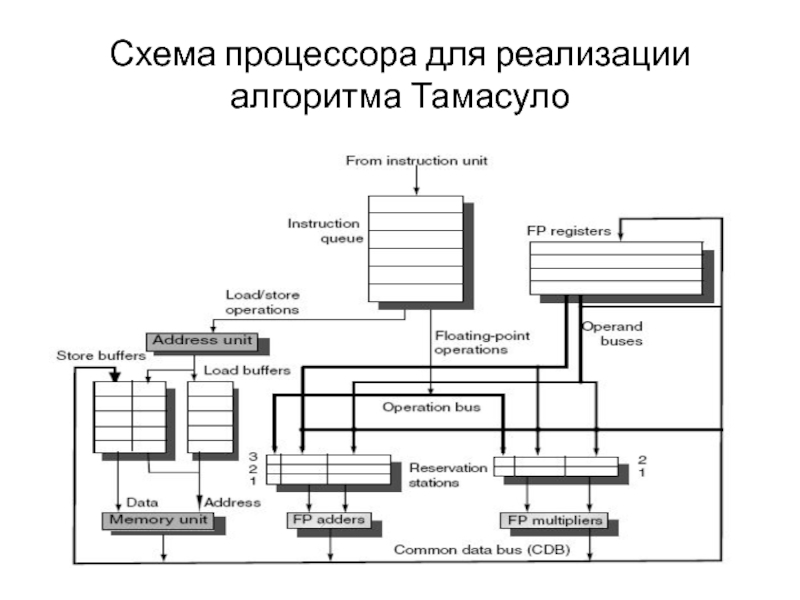

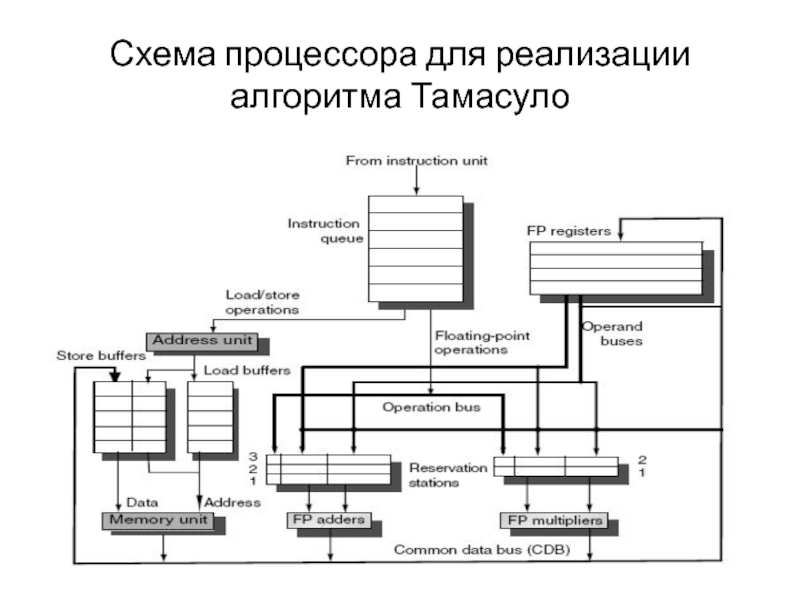

Слайд 3Схема процессора для реализации алгоритма Тамасуло

Слайд 4Состав процессора

Очередь планирования (Instruction queue)[ОП]

Регистровый файл (FP Registers) [РФ]

Станции резервирования

(Reserve Station) [СР]

Простое вещественное устройство (FP adder)

Сложное вещественное устройство (FP

Muliplier)

Общая шина данных (Common Data Bus)[ОШД]

Устройство вычисление адреса (Address Unit)

Буфера загрузки (Load buffer)

Буфера сохранения (Store buffer)

Устройство работы с памятью (Memory Unit).

Слайд 5Схема процессора для реализации алгоритма Тамасуло

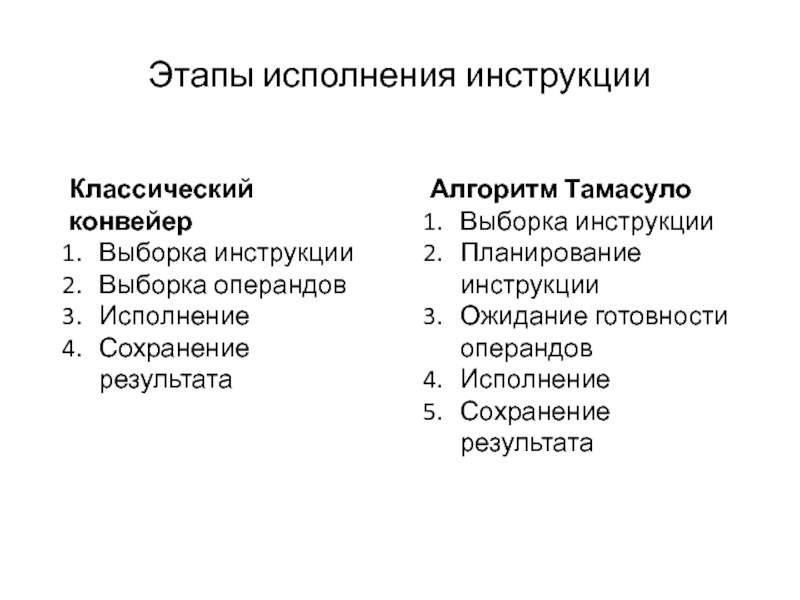

Слайд 6Этапы исполнения инструкции

Классический конвейер

Выборка инструкции

Выборка операндов

Исполнение

Сохранение результата

Алгоритм Тамасуло

Выборка инструкции

Планирование

инструкции

Ожидание готовности операндов

Исполнение

Сохранение результата

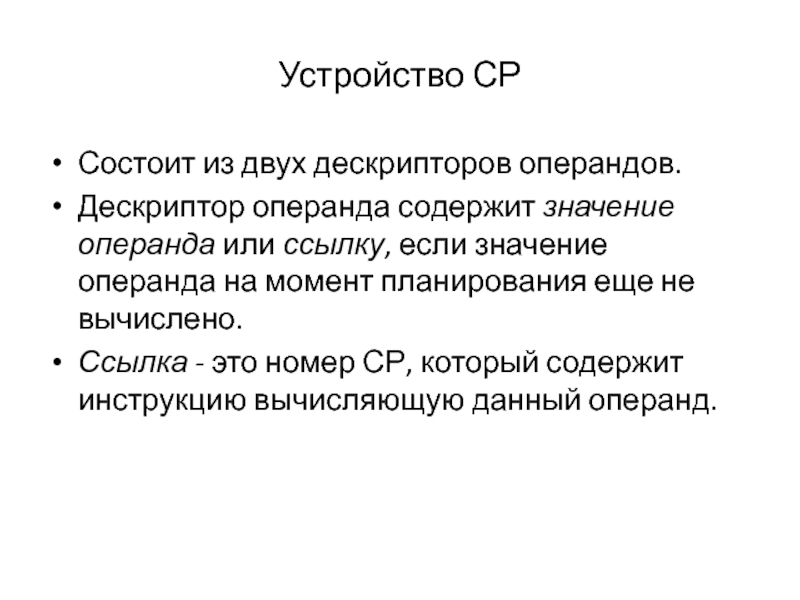

Слайд 7Устройство СР

Состоит из двух дескрипторов операндов.

Дескриптор операнда содержит значение операнда

или ссылку, если значение операнда на момент планирования еще не

вычислено.

Ссылка - это номер СР, который содержит инструкцию вычисляющую данный операнд.

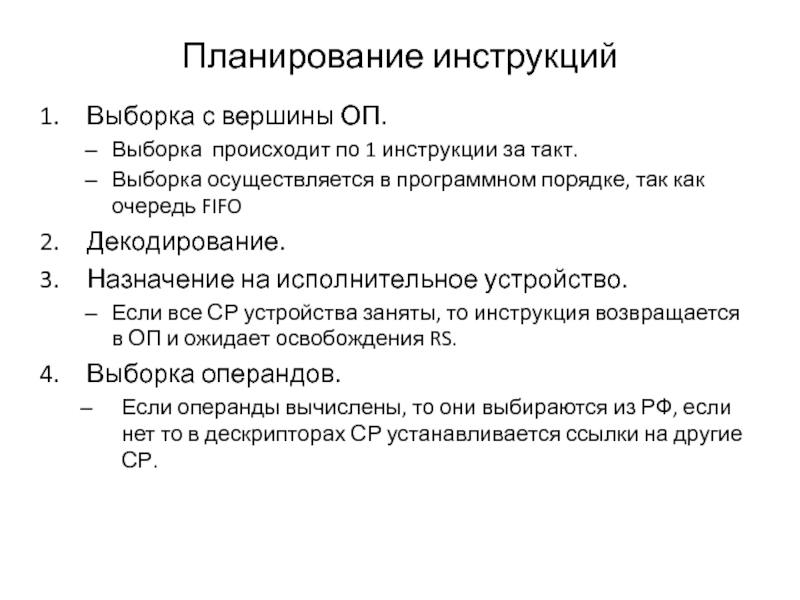

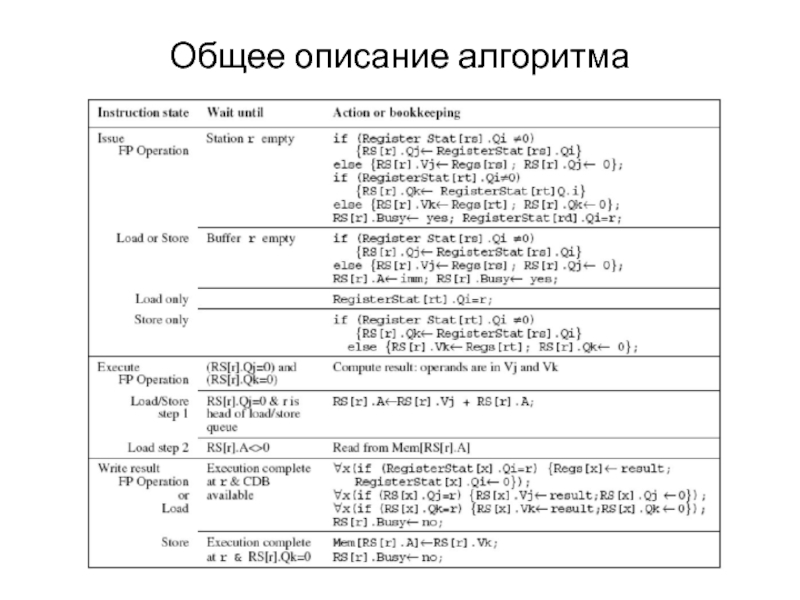

Слайд 8Планирование инструкций

Выборка с вершины ОП.

Выборка происходит по 1 инструкции

за такт.

Выборка осуществляется в программном порядке, так как очередь FIFO

Декодирование.

Назначение

на исполнительное устройство.

Если все СР устройства заняты, то инструкция возвращается в ОП и ожидает освобождения RS.

Выборка операндов.

Если операнды вычислены, то они выбираются из РФ, если нет то в дескрипторах СР устанавливается ссылки на другие СР.

Слайд 9Ожидание готовности операндов, исполнение, сохранение результатов

Инструкция ожидает в СР до

тех пор, пока не будут вычислены все ее операнды и

записаны в соответствующие дескрипторы.

Передача вычисленного операнда происходит по ОШД вместе с номером СР, который его содержал.

Каждая СР слушает ОШД и сравнивает значение номер передаваемого по ней СР с ожидаемым. Если номера совпадает то она забирает значение операнда с ОШД.

Передаваемые по ОШД данные сохраняются в РФ.

Если все операнды находятся СР, то инструкция отправляется на исполнение.

Слайд 10Обработка инструкций загрузки и сохранения.

Инструкция загрузки:

Вычисление адреса

Выполнение загрузки

по адресу

Инструкция сохранения:

Вычисление адреса

Ожидания готовности операнда.

Выполнение сохранения по адресу.

Буфер загрузки:

поле адреса.

Буфер сохранения: поле адреса, СР для операнда.

Слайд 11Порядок исполнения инструкций загрузки и сохранения.

Определяется наличием зависимостей между

инструкциями по ячейкам памяти.

Адреса ячеек вычисляются на первом этапе.

Инструкция

загрузки ожидает завершения всех предшествующих инструкций сохранения по данному адресу.

Инструкция сохранения ожидает завершения всех предшествующих инструкций загрузки и сохранения по данному адресу.

Слайд 12Файл переименования

Находиться в РФ.

Содержит имена переименованных регистров.

Состоит из двух полей:

Если

значение находиться в регистре, то ссылка равна нулю, если нет

то ссылка указывает на СР, которая его вычислит.

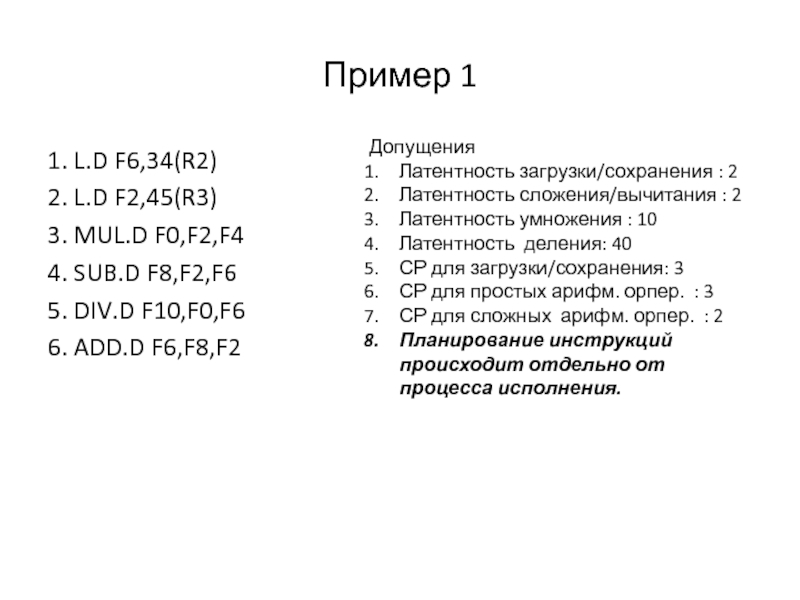

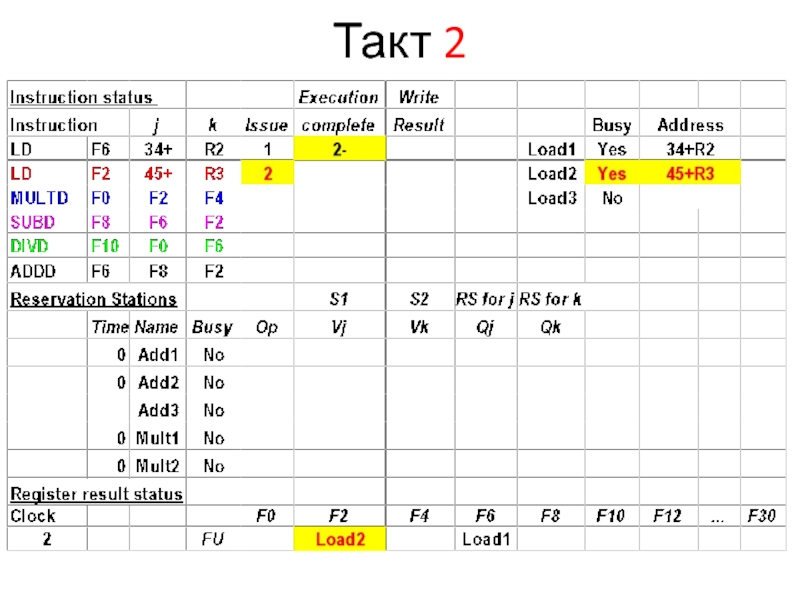

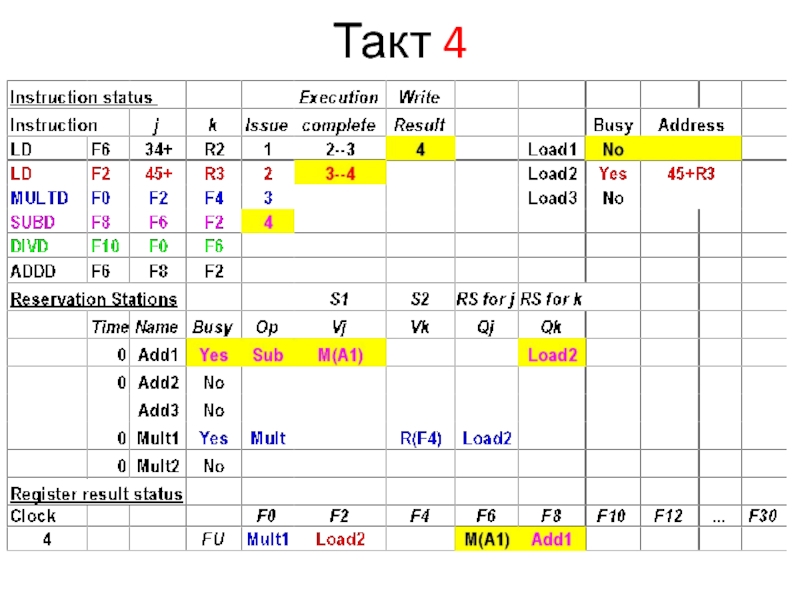

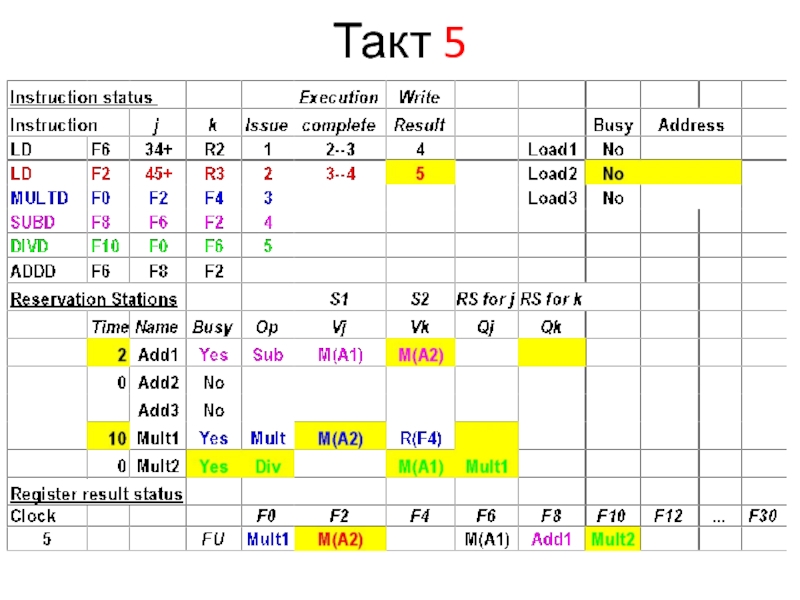

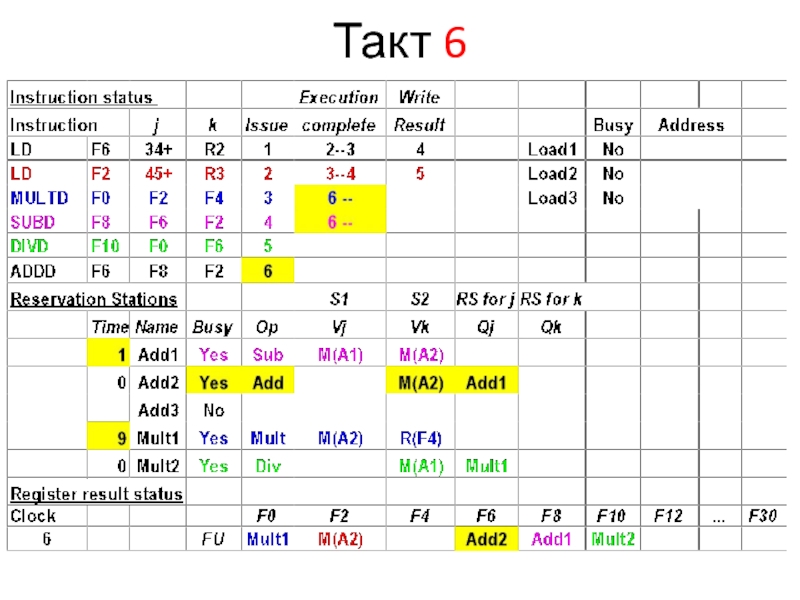

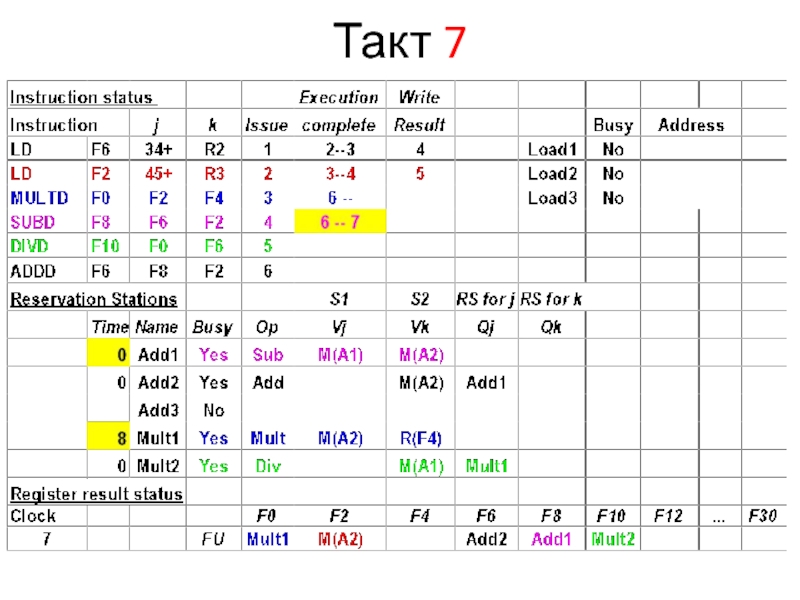

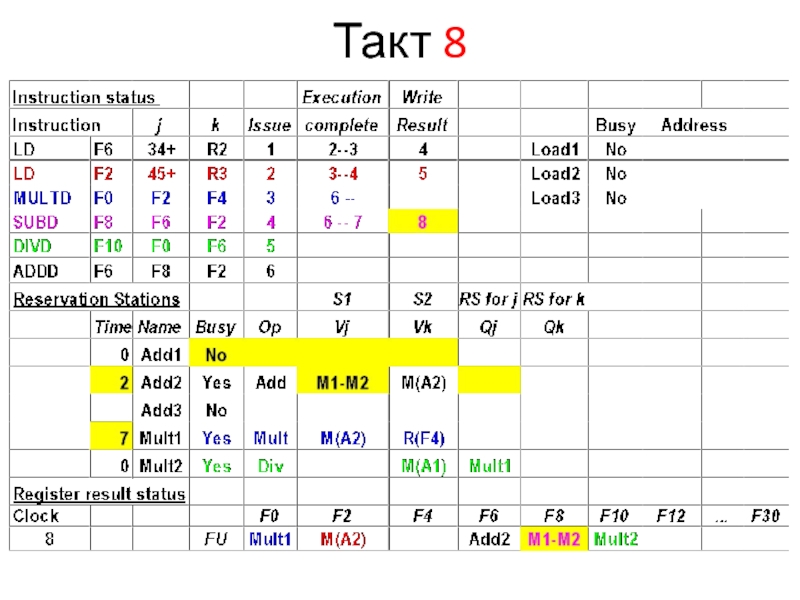

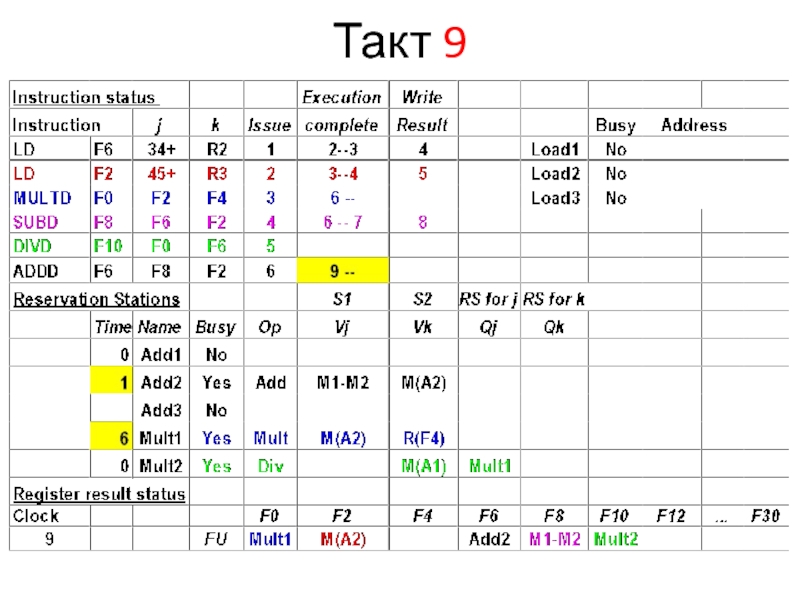

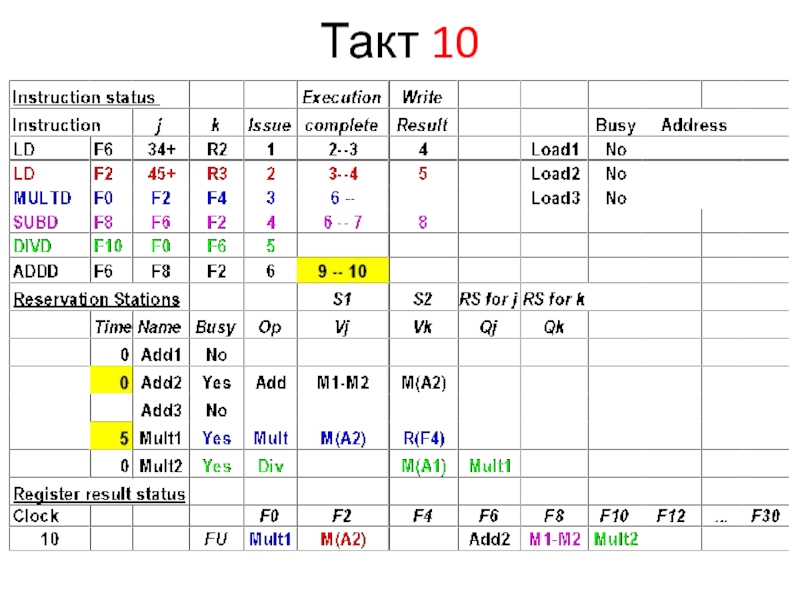

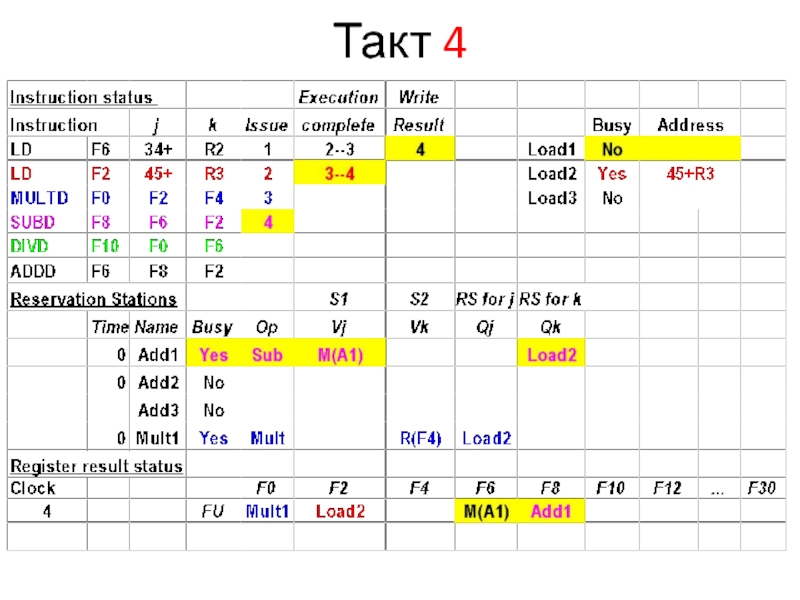

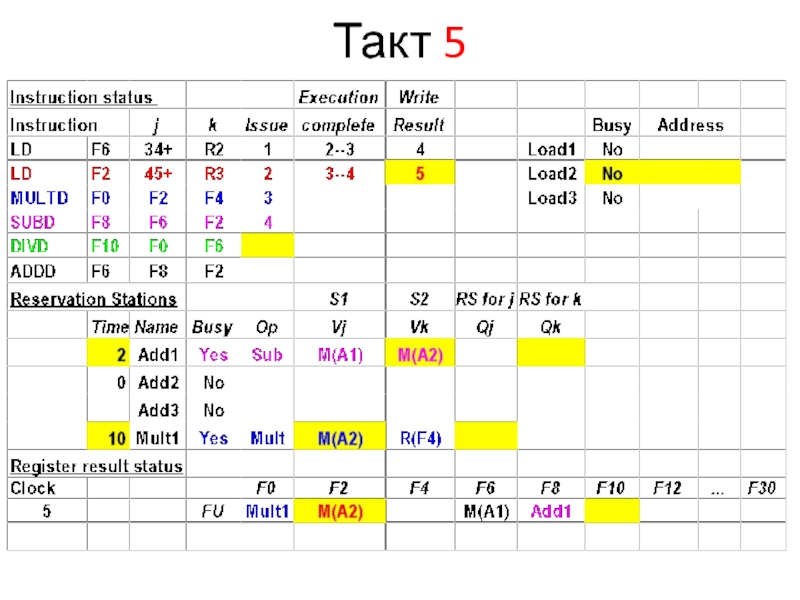

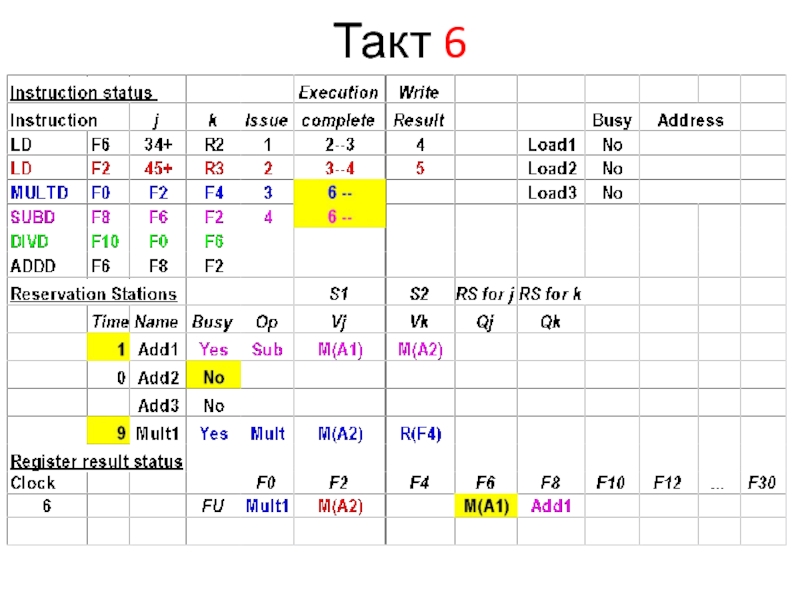

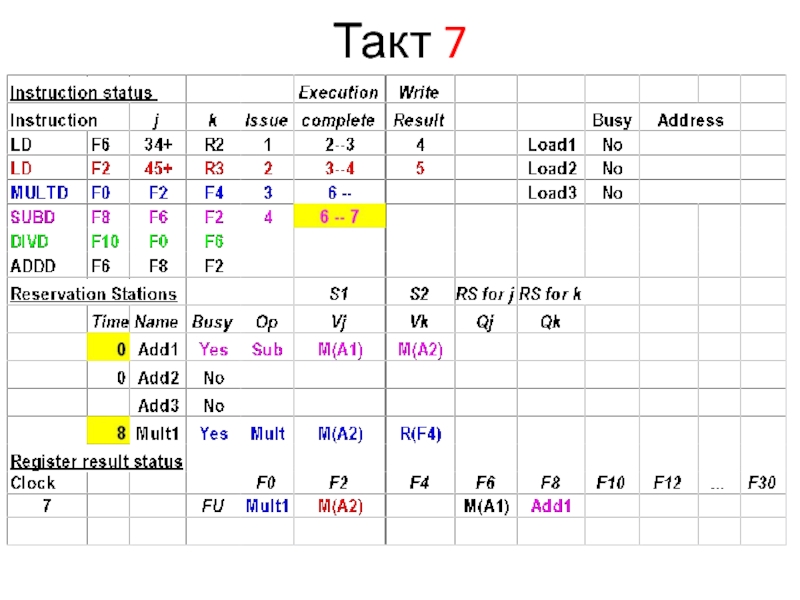

Слайд 13Пример 1

1. L.D F6,34(R2)

2. L.D F2,45(R3)

3. MUL.D F0,F2,F4

4. SUB.D F8,F2,F6

5.

DIV.D F10,F0,F6

6. ADD.D F6,F8,F2

Допущения

Латентность загрузки/сохранения : 2

Латентность сложения/вычитания :

2

Латентность умножения : 10

Латентность деления: 40

СР для загрузки/сохранения: 3

СР для простых арифм. орпер. : 3

СР для сложных арифм. орпер. : 2

Планирование инструкций происходит отдельно от процесса исполнения.

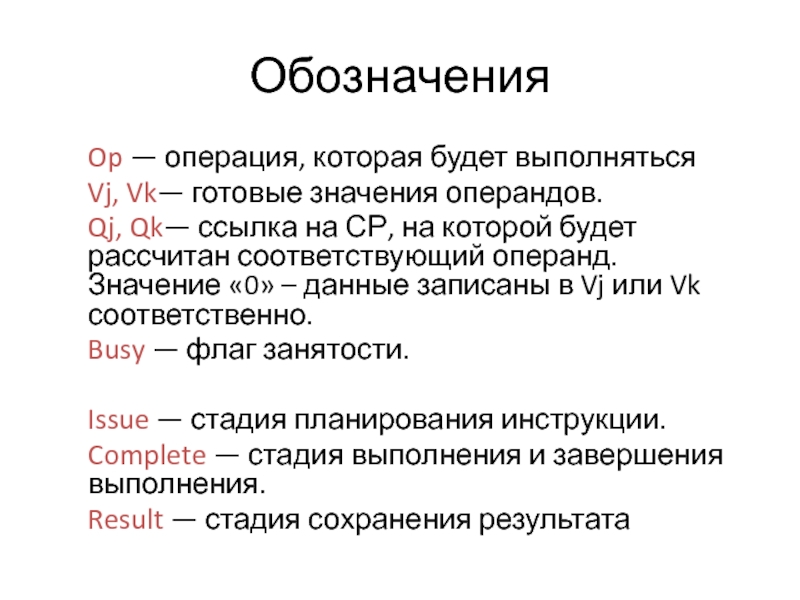

Слайд 14Обозначения

Op — операция, которая будет выполняться

Vj, Vk— готовые значения операндов.

Qj,

Qk— ссылка на СР, на которой будет рассчитан соответствующий операнд.

Значение «0» – данные записаны в Vj или Vk соответственно.

Busy — флаг занятости.

Issue — стадия планирования инструкции.

Complete — стадия выполнения и завершения выполнения.

Result — стадия сохранения результата

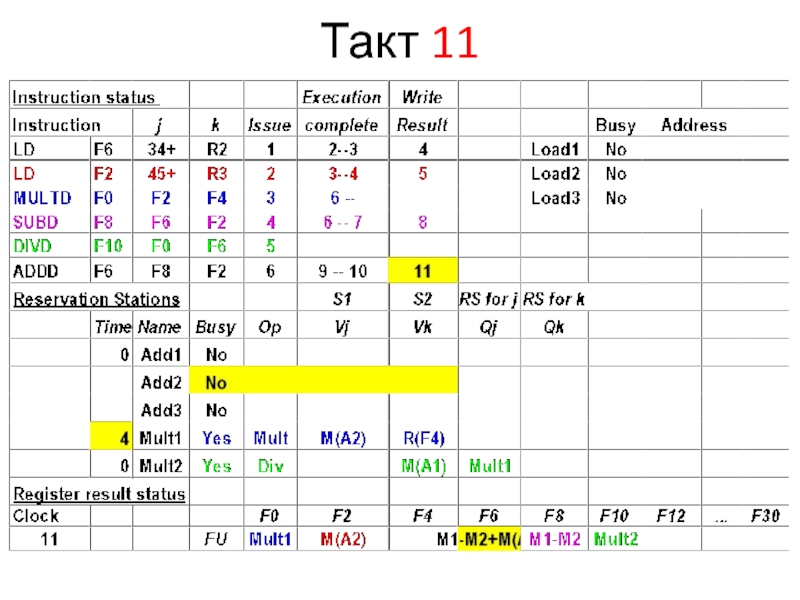

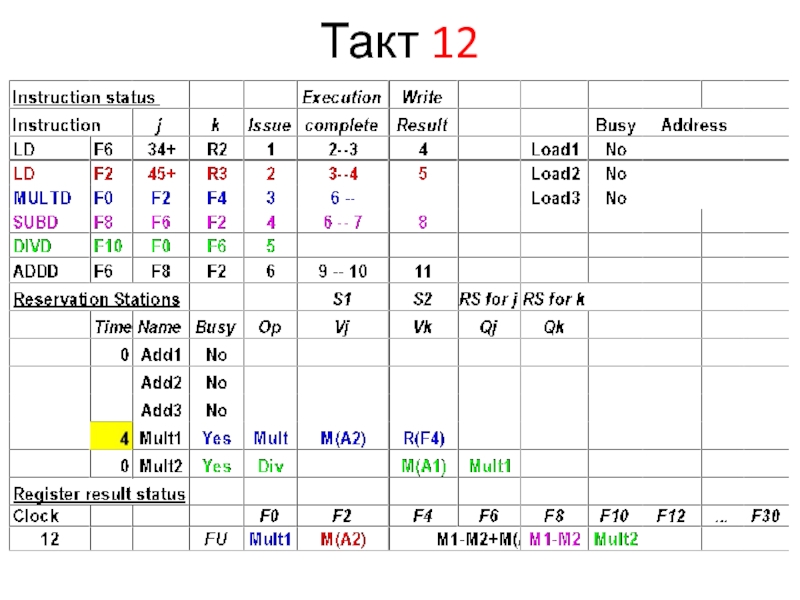

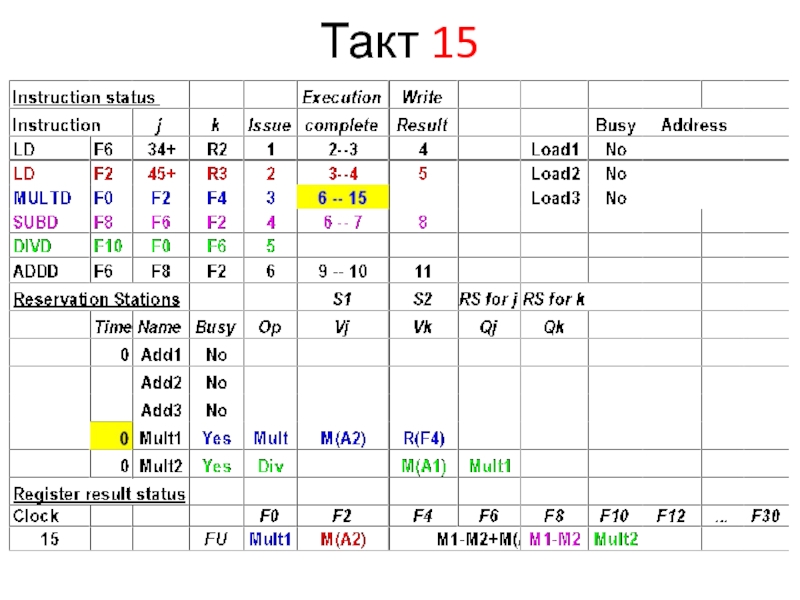

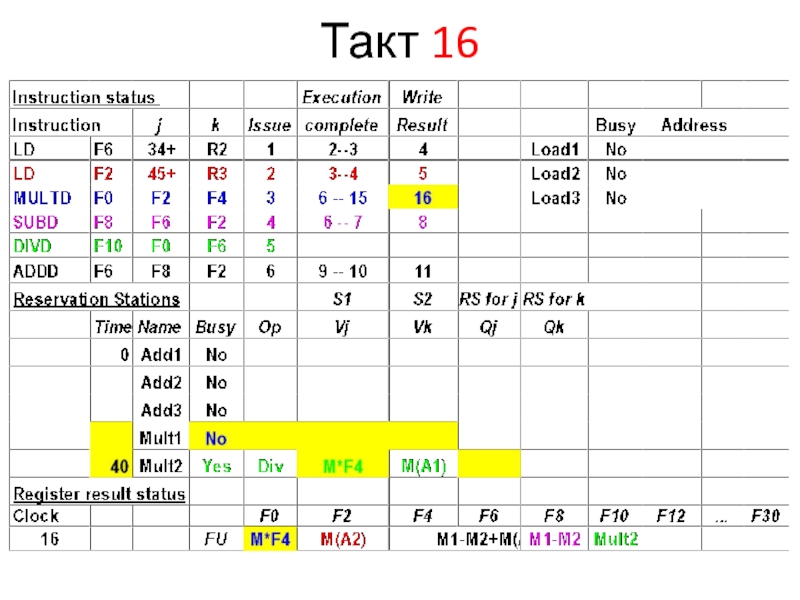

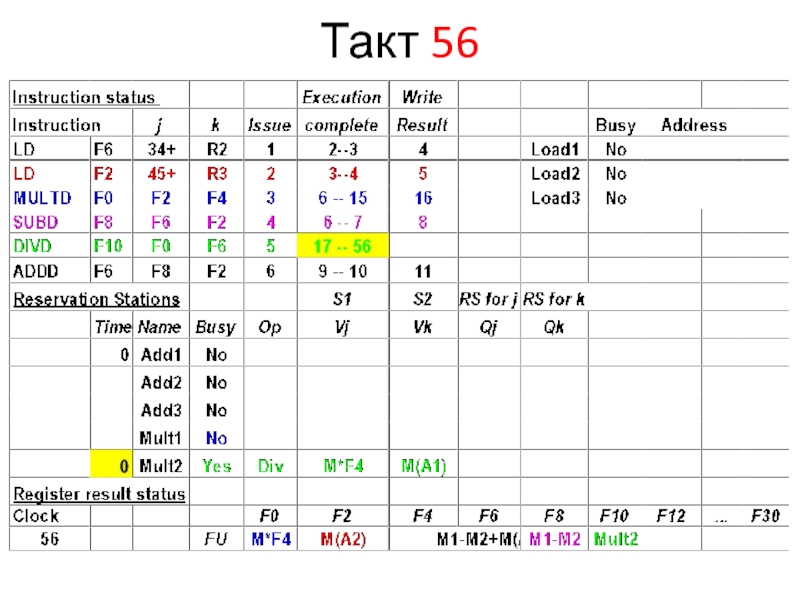

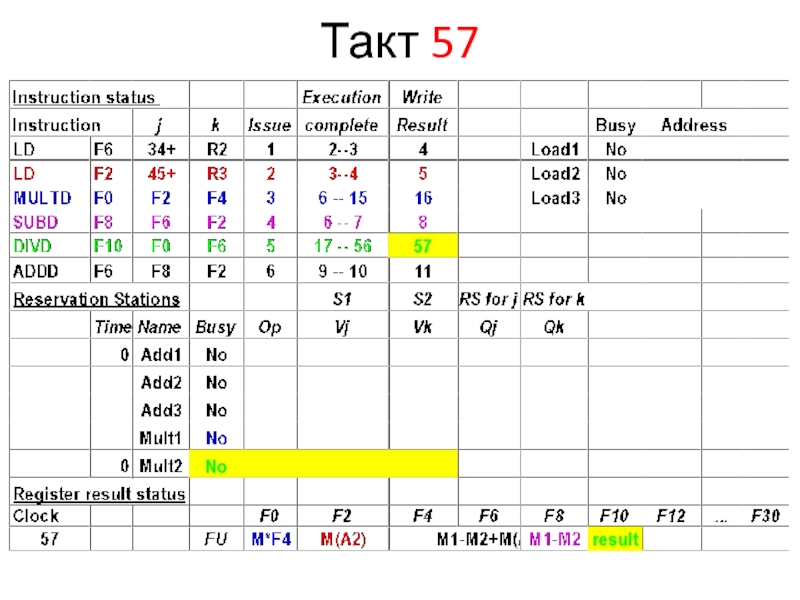

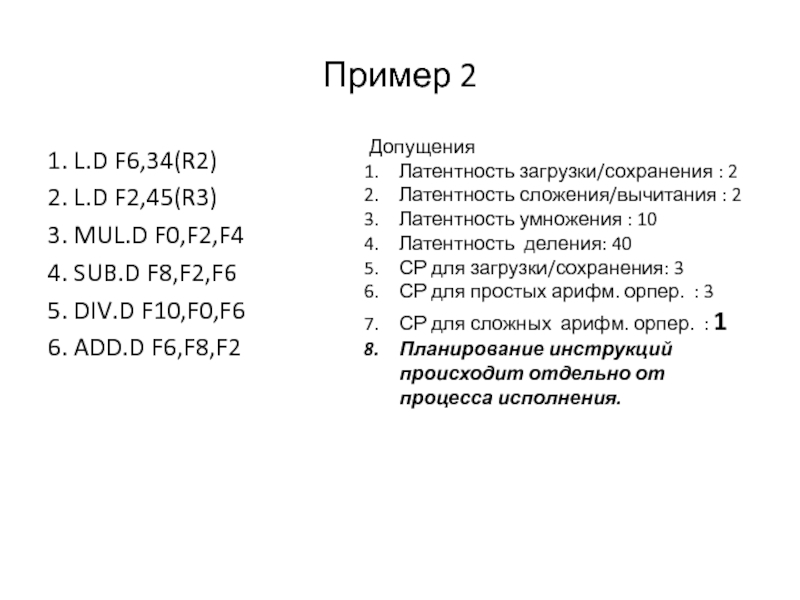

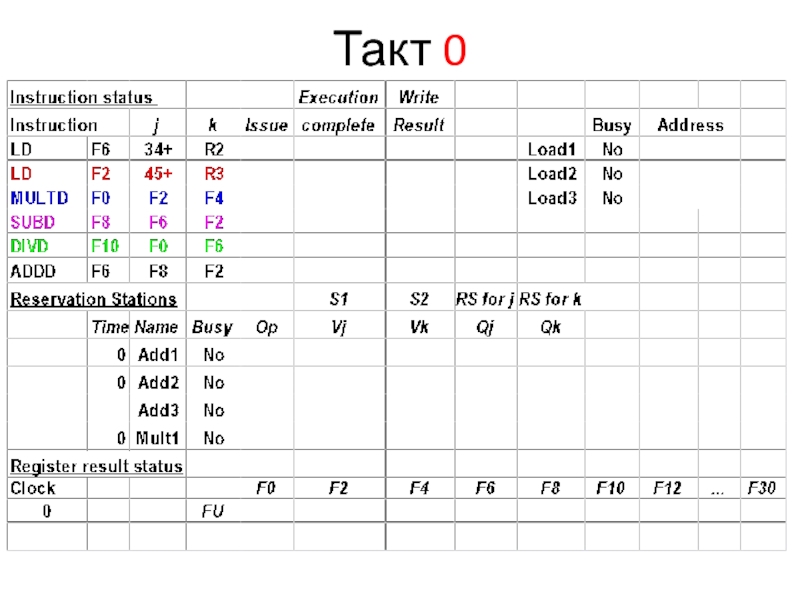

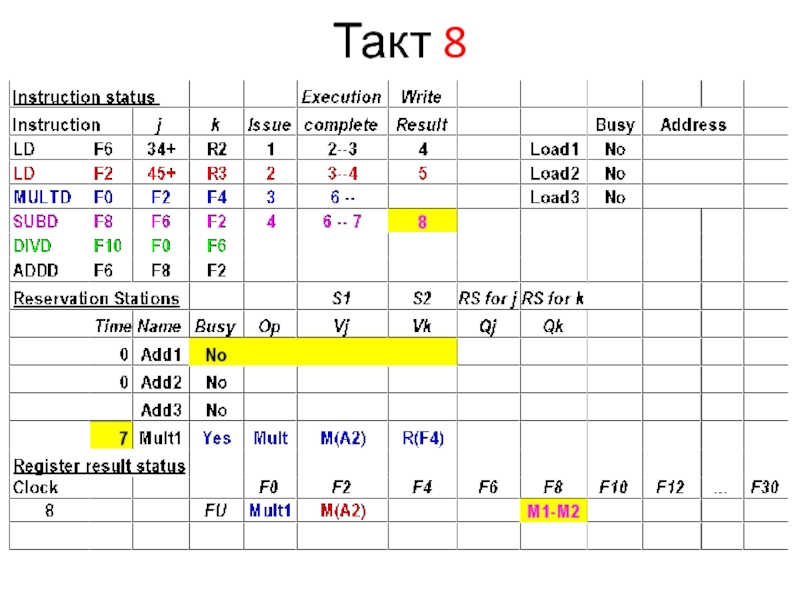

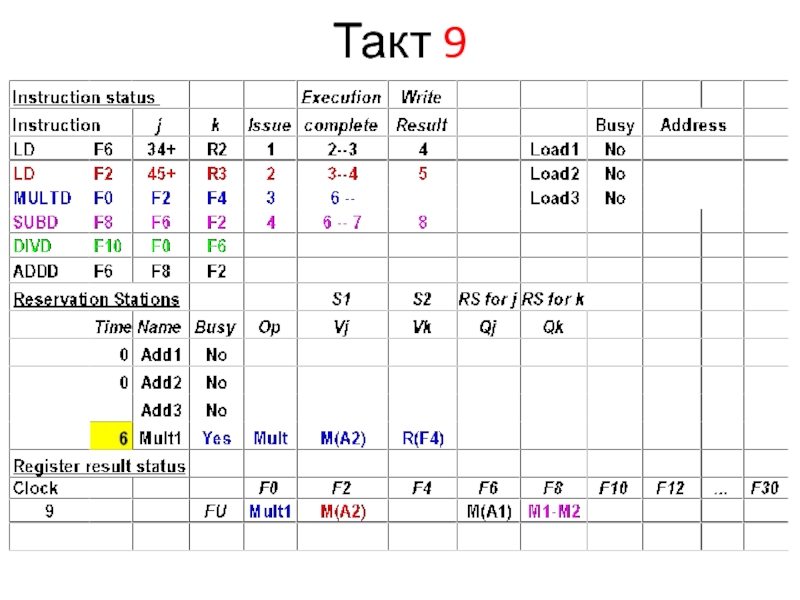

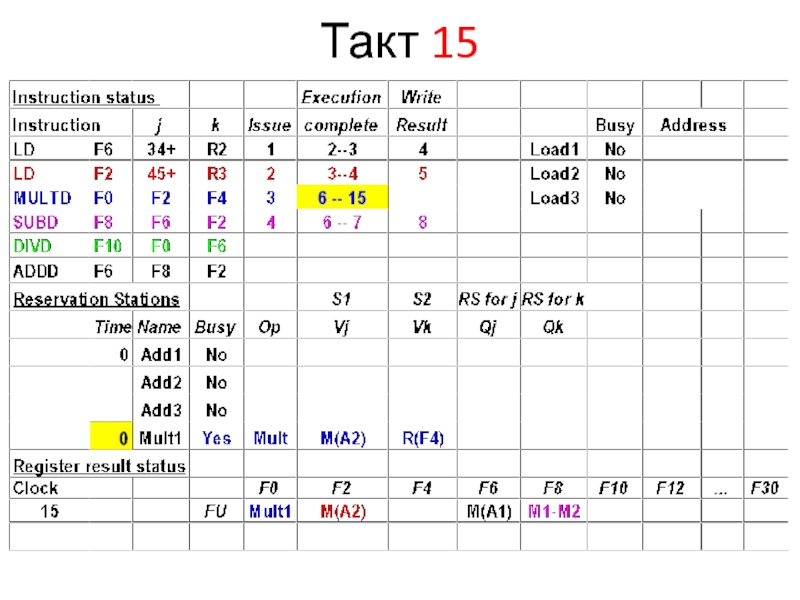

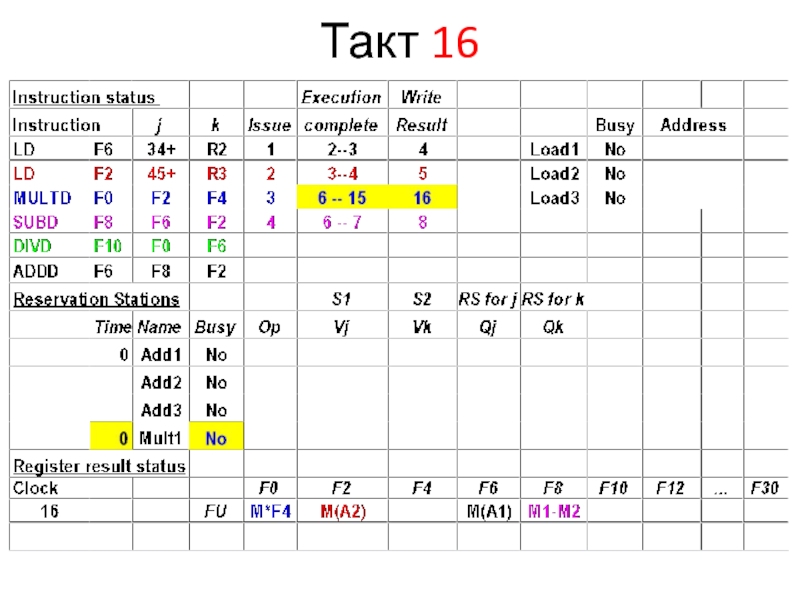

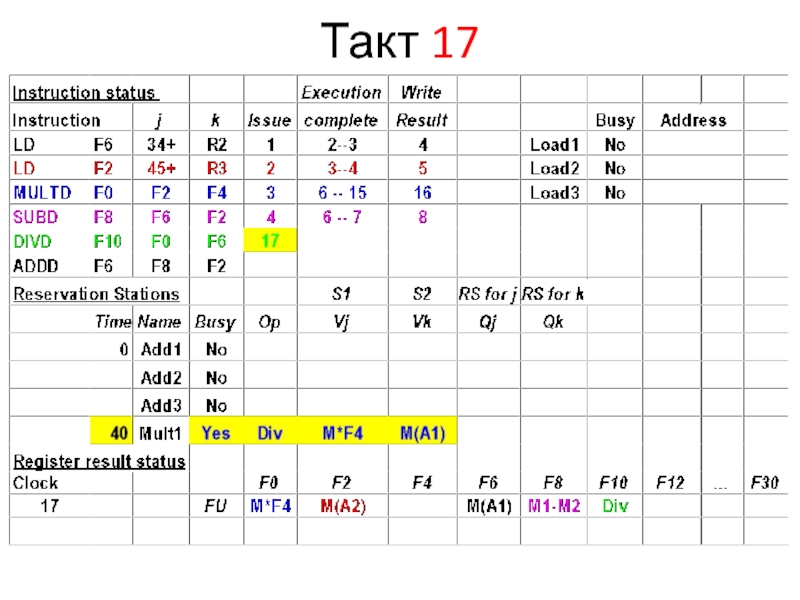

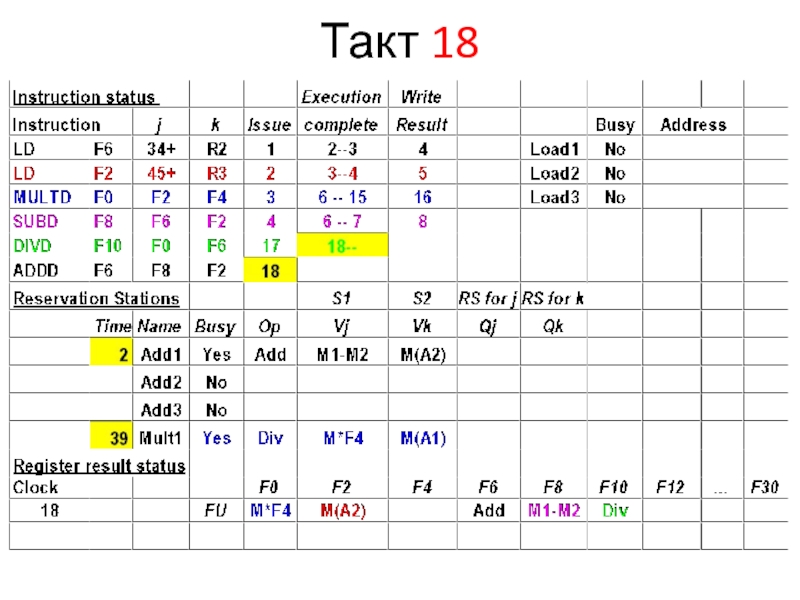

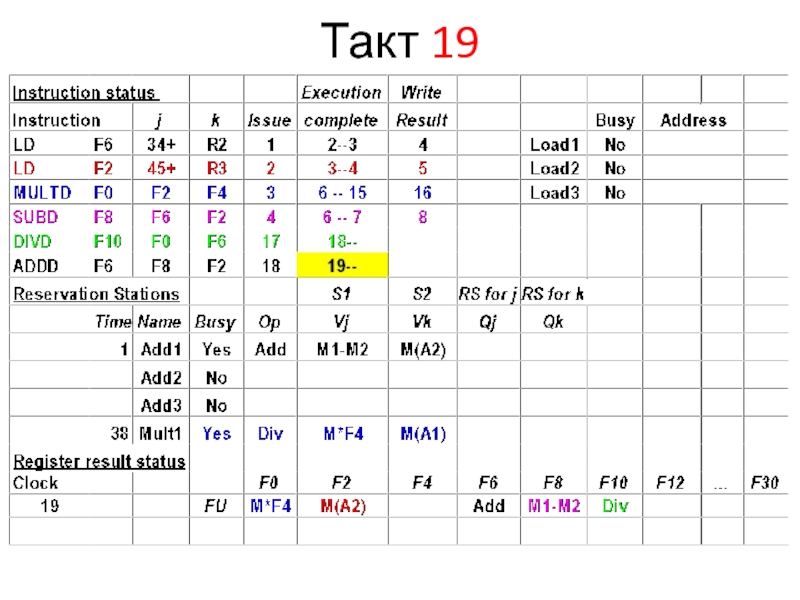

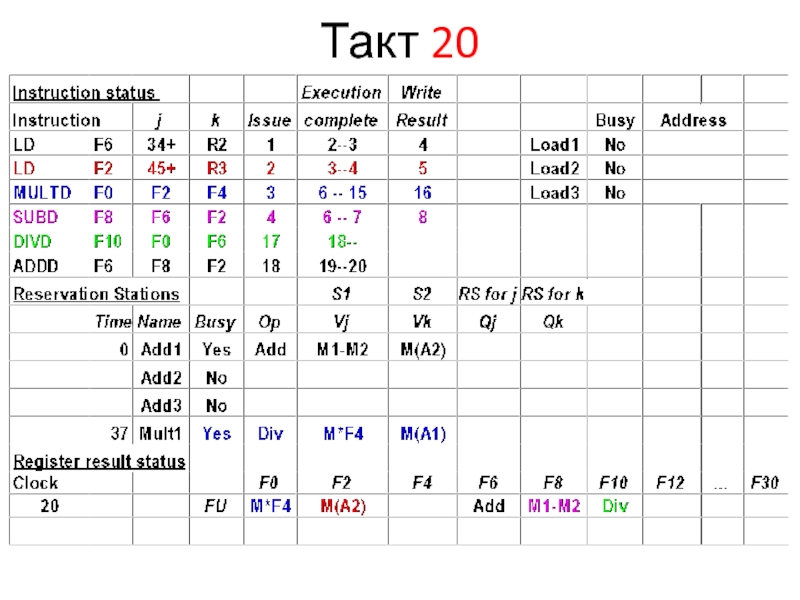

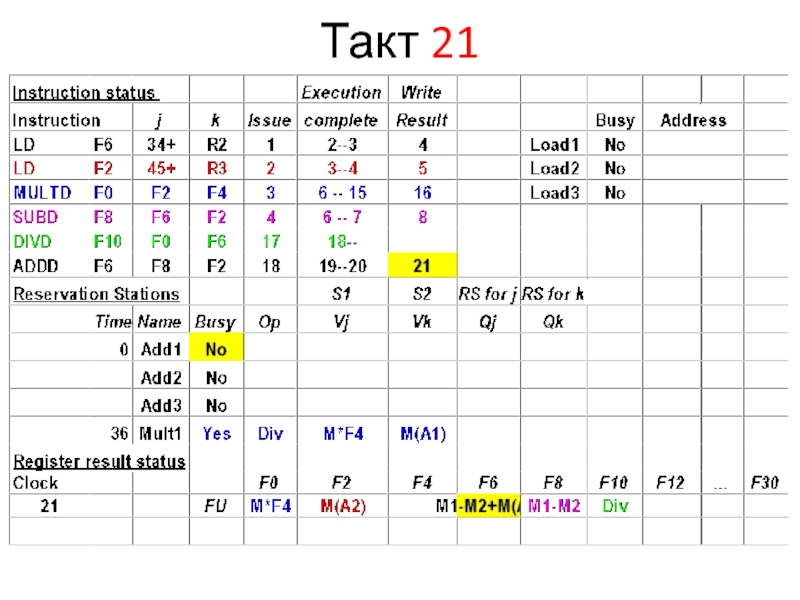

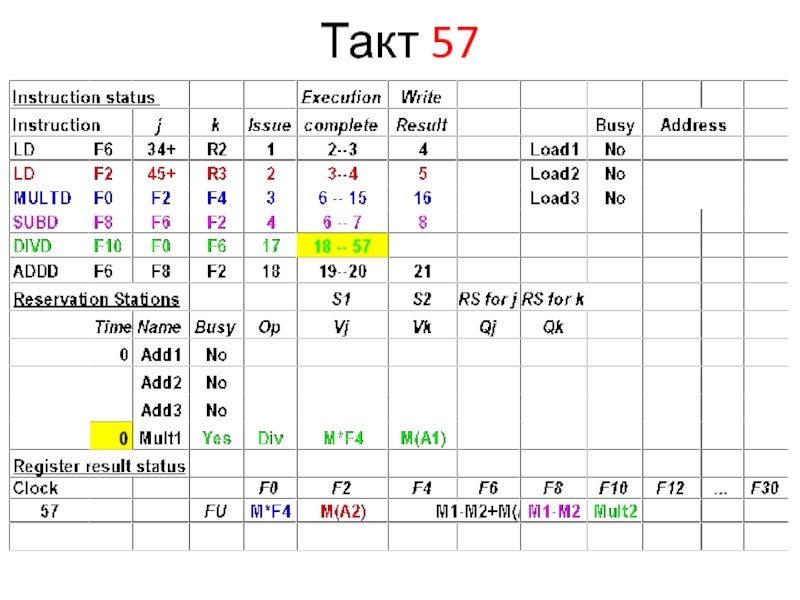

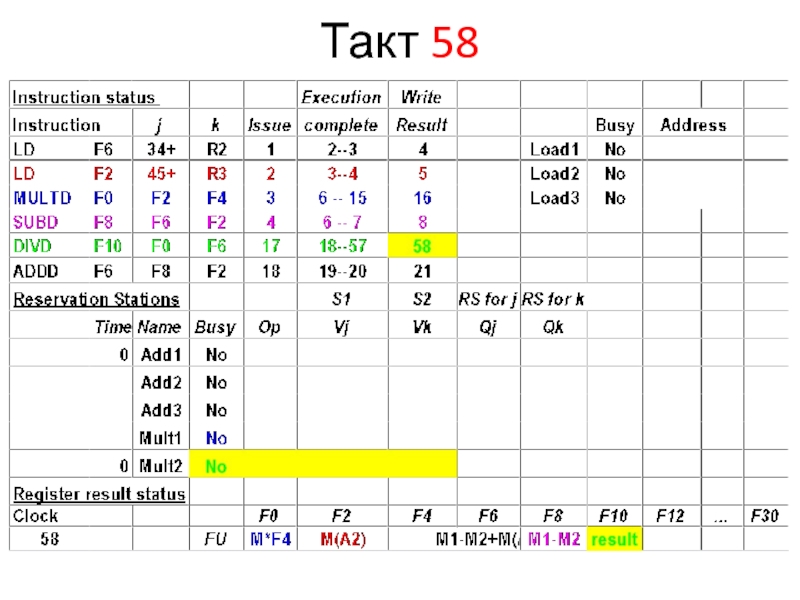

Слайд 32Пример 2

1. L.D F6,34(R2)

2. L.D F2,45(R3)

3. MUL.D F0,F2,F4

4. SUB.D F8,F2,F6

5.

DIV.D F10,F0,F6

6. ADD.D F6,F8,F2

Допущения

Латентность загрузки/сохранения : 2

Латентность сложения/вычитания :

2

Латентность умножения : 10

Латентность деления: 40

СР для загрузки/сохранения: 3

СР для простых арифм. орпер. : 3

СР для сложных арифм. орпер. : 1

Планирование инструкций происходит отдельно от процесса исполнения.

Слайд 50Достоинства и недостатки алгоритма.

Достоинства:

Повышение пропускной способности

Уменьшение времени простоя процессора

Недостатки

Большие

аппаратные затраты на реализацию дополнительных устройств.

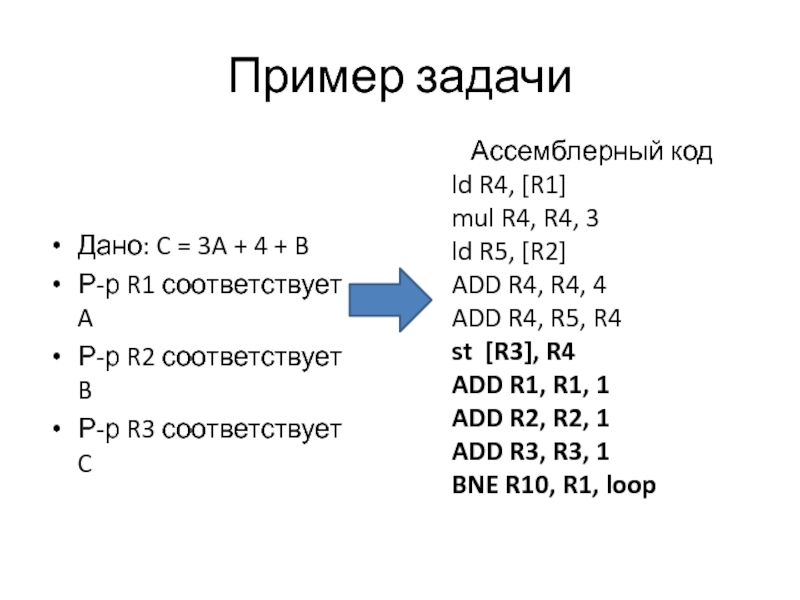

Слайд 51Пример задачи

Дано: C = 3A + 4 + B

Р-р R1

соответствует A

Р-р R2 соответствует B

Р-р R3 соответствует C

Ассемблерный код

ld R4,

[R1]

mul R4, R4, 3

ld R5, [R2]

ADD R4, R4, 4

ADD R4, R5, R4

st [R3], R4

ADD R1, R1, 1

ADD R2, R2, 1

ADD R3, R3, 1

BNE R10, R1, loop

![Алгоритм Томасуло Состав процессораОчередь планирования (Instruction queue)[ОП]Регистровый файл (FP Registers) [РФ]Станции резервирования (Reserve Состав процессораОчередь планирования (Instruction queue)[ОП]Регистровый файл (FP Registers) [РФ]Станции резервирования (Reserve Station) [СР]Простое вещественное устройство (FP adder)Сложное](/img/thumbs/ba018594b9e9f917a996885060a3e6eb-800x.jpg)