Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Информация о видах процессоров и разновидность архитектуры

Содержание

- 1. Информация о видах процессоров и разновидность архитектуры

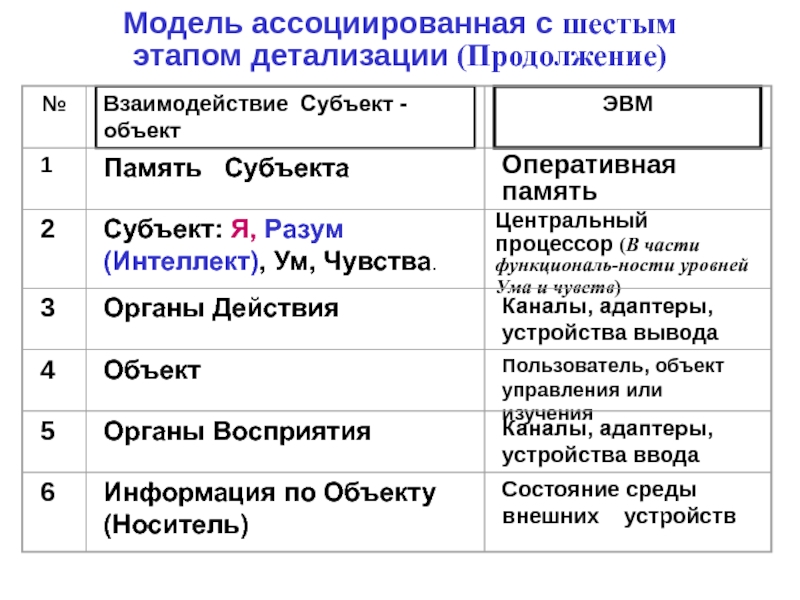

- 2. Модель ассоциированная с шестым этапом детализации (Продолжение)

- 3. ЭВМ - Субъект: Подобия - РазличияЦентральный процессор

- 4. Специфика Ума и Интеллекта Мы действительно

- 5. Мудрецы древности знали, что ум

- 6. СодержаниеИнформация о видах процессоров и разновидность архитектуры.Оперативная память и ее типы.Кэш память и ее особенности.

- 7. ПроцессорЦентра́льный проце́ссор (ЦП; CPU — англ. céntral

- 8. Современные ЦПСовременные ЦП, выполняемые в виде отдельных

- 9. Разновидности Архитектур ЦПАрхитектура фон НейманаКонвейерная архитектураМногоядерные процессорыПараллельная архитектураCISC-процессорыRISC-процессорыMISC-процессоры

- 10. Архитектура фон НейманаБольшинство современных процессоров для персональных

- 11. Конвейерная архитектураКонвейерная архитектура (pipelining) была введена в

- 12. Многоядерные процессорыСодержат несколько процессорных ядер в одном

- 13. Параллельная архитектураАрхитектура фон Неймана обладает тем недостатком,

- 14. CISC-процессорыComplex Instruction Set Computing — вычисления со

- 15. RISC-процессорыReduced Instruction Set Computing (technology) — вычисления

- 16. MISC-процессорыMinimum Instruction Set Computing — вычисления с

- 17. Оперативная памятьОперати́вная па́мять (также ОЗУ — оперативное

- 18. В современных вычислительных устройствах, оперативная память выполнена

- 19. Схема взаимодействия ОП и др. элементов

- 20. Кэш памятьВпервые слово «кэш» в компьютерном контексте

- 21. Кэш — это память с большей скоростью

- 22. РЕГИСТРОВАЯ КЭШ-ПАМЯТЬРегистровая КЭШ-память - высокоскоростная память сравнительно

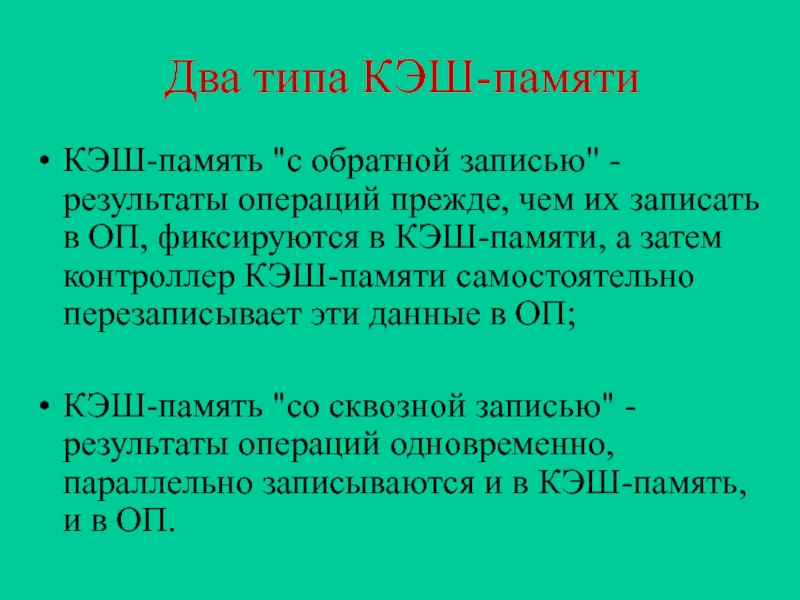

- 23. Два типа КЭШ-памятиКЭШ-память "с обратной записью" -

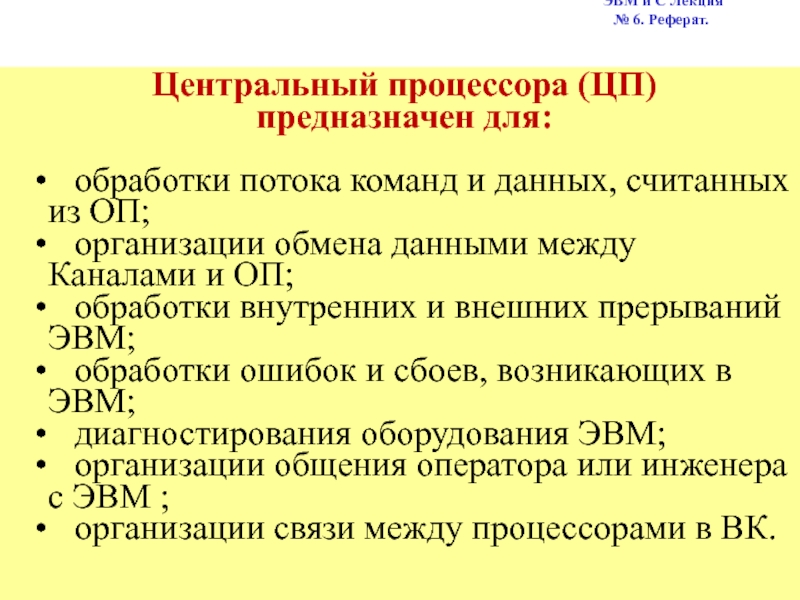

- 24. ЭВМ и С Лекция № 6.

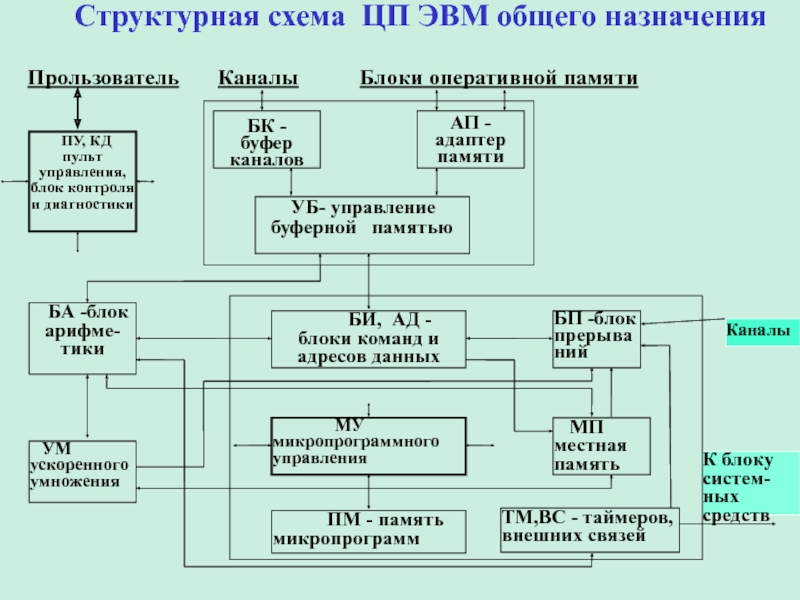

- 25. К блоку систем-ных средствБК -буфер каналовАП -адаптер

- 26. Управление памятью Блоки Управление памятью

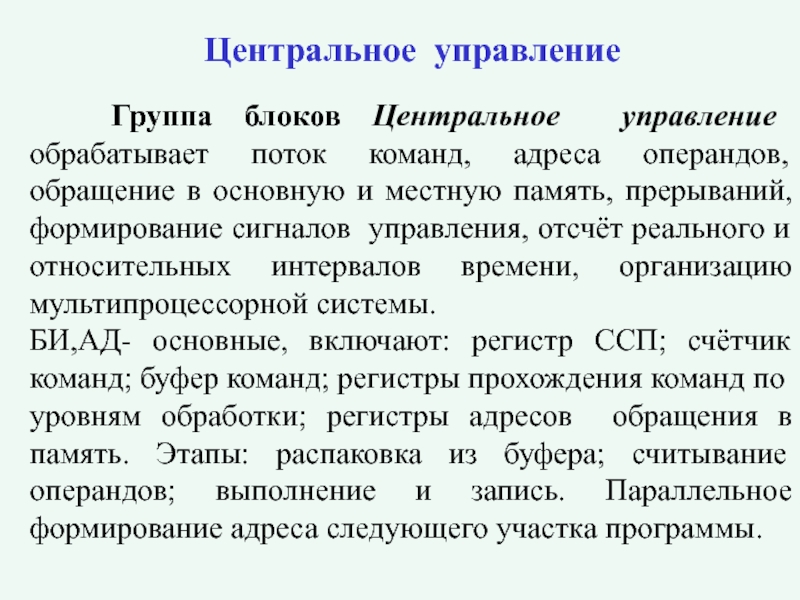

- 27. Центральное управление Группа блоков Центральное управление

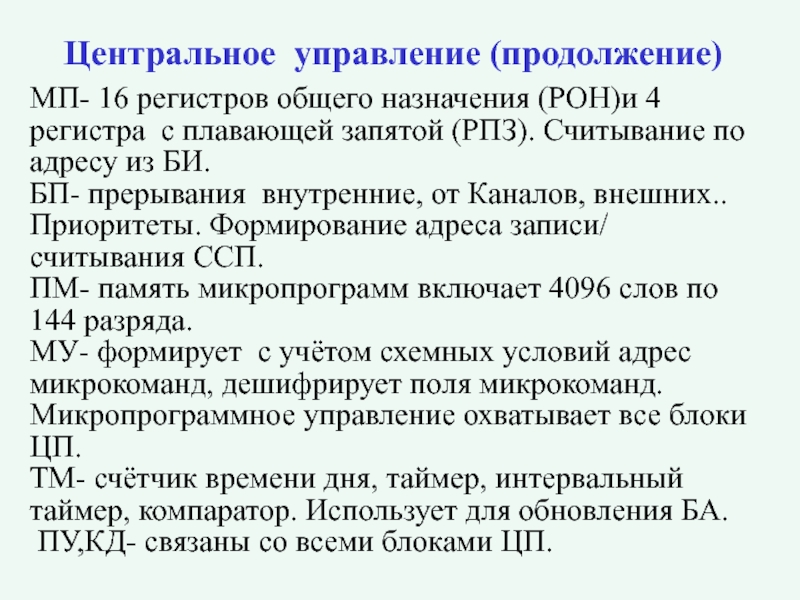

- 28. Центральное управление (продолжение)МП- 16 регистров общего назначения

- 29. Структурная схема процессора ПЭВМ.

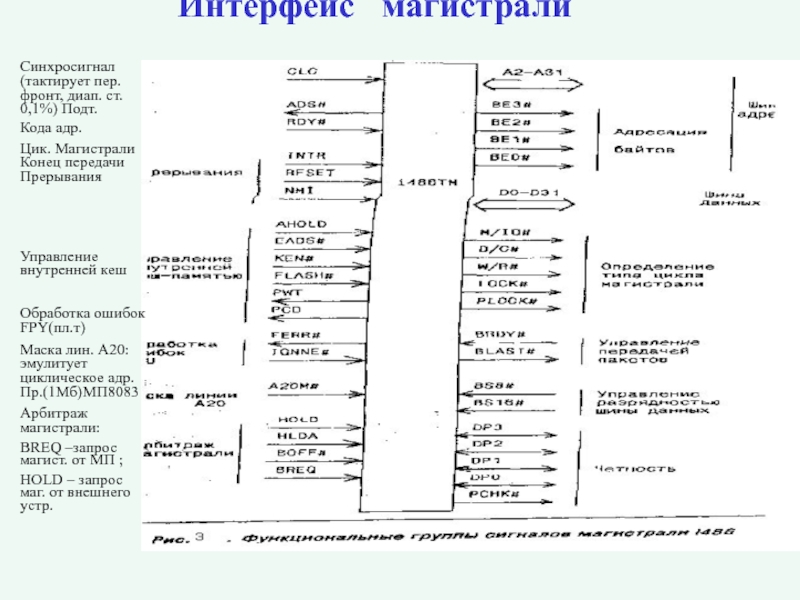

- 30. Интерфейс магистрали Синхросигнал (тактирует

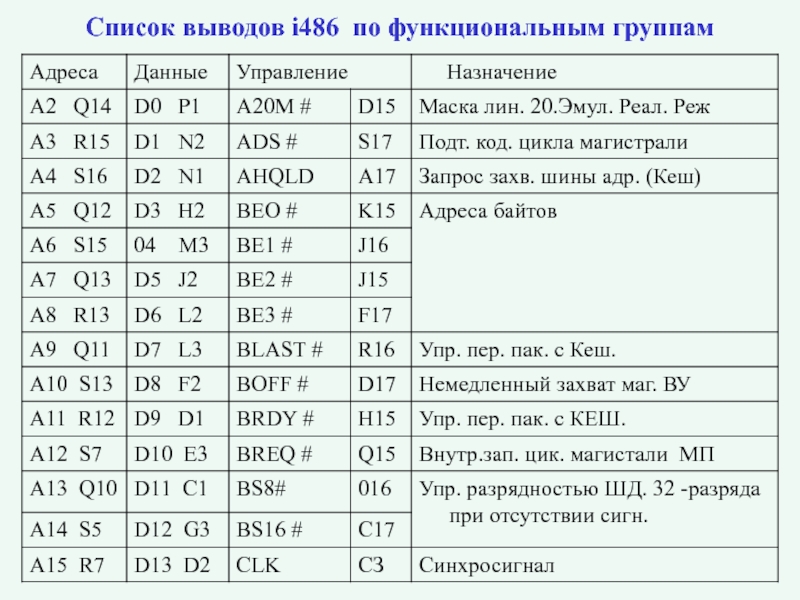

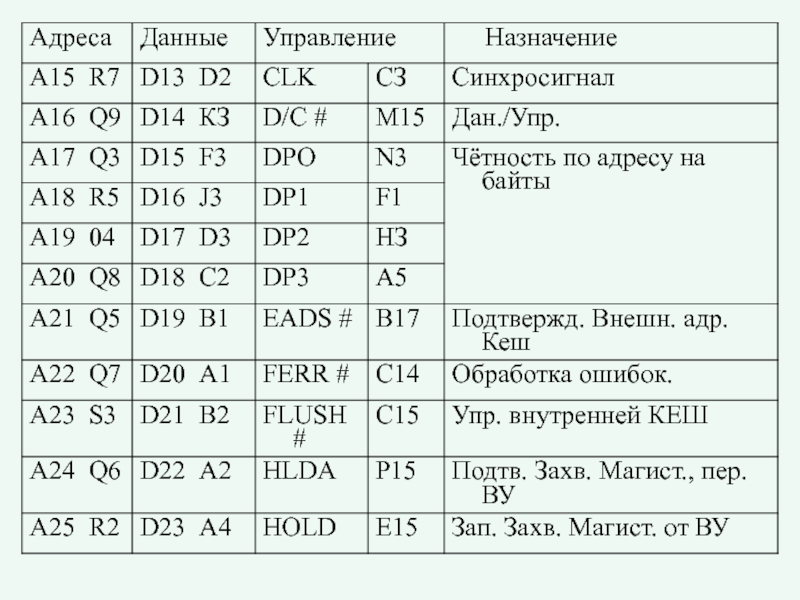

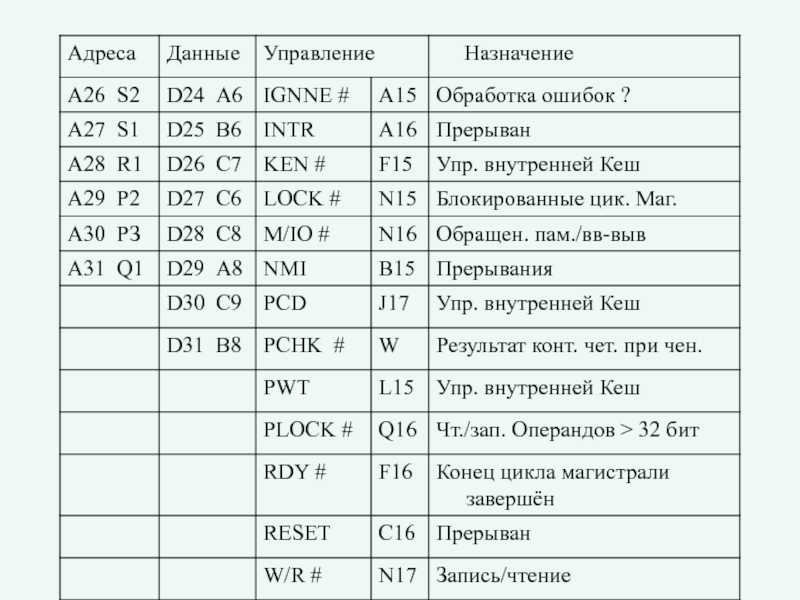

- 31. Список выводов i486 по функциональным группам

- 32. Слайд 32

- 33. Слайд 33

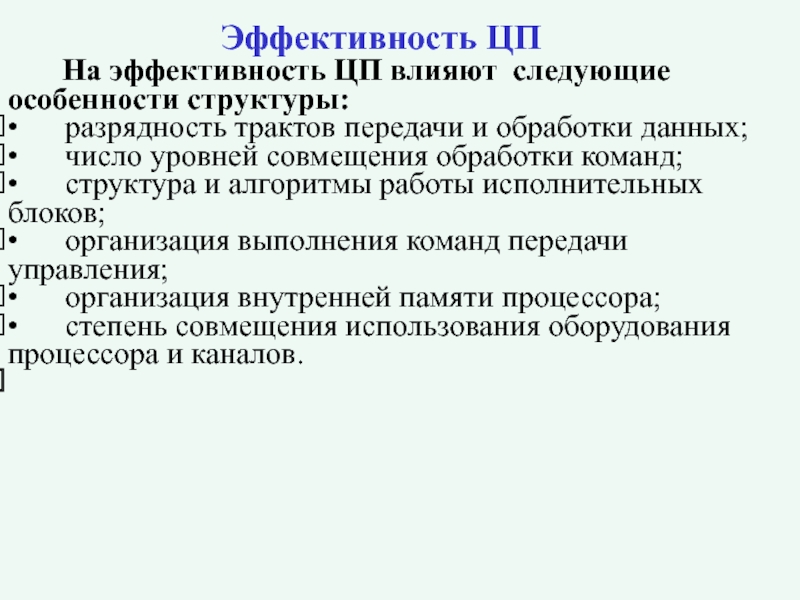

- 34. Эффективность ЦП На эффективность

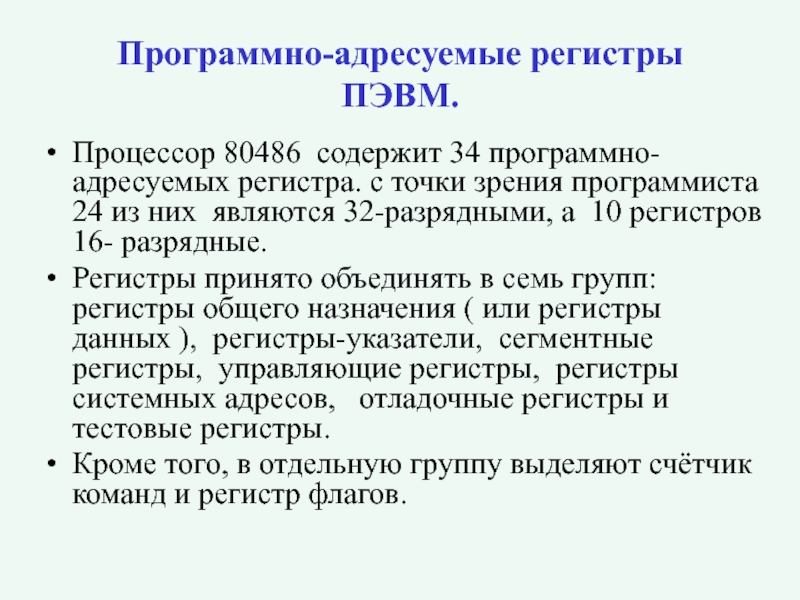

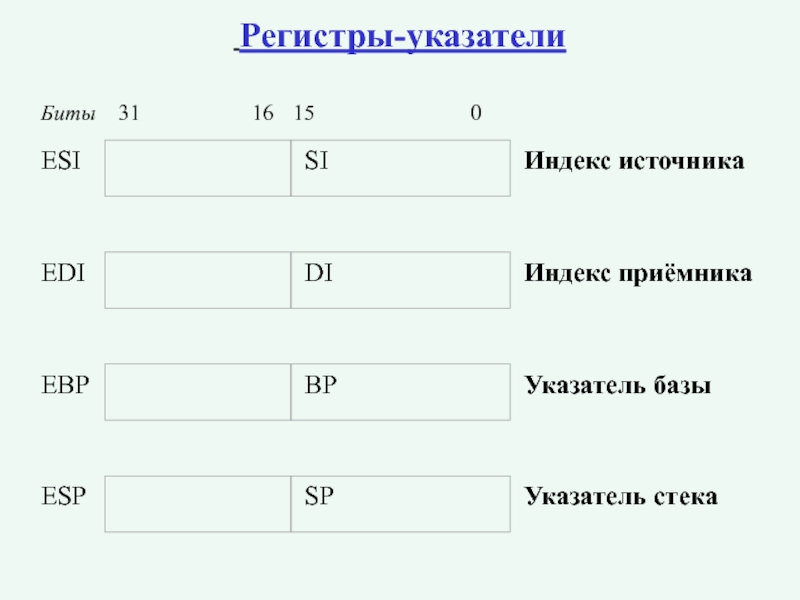

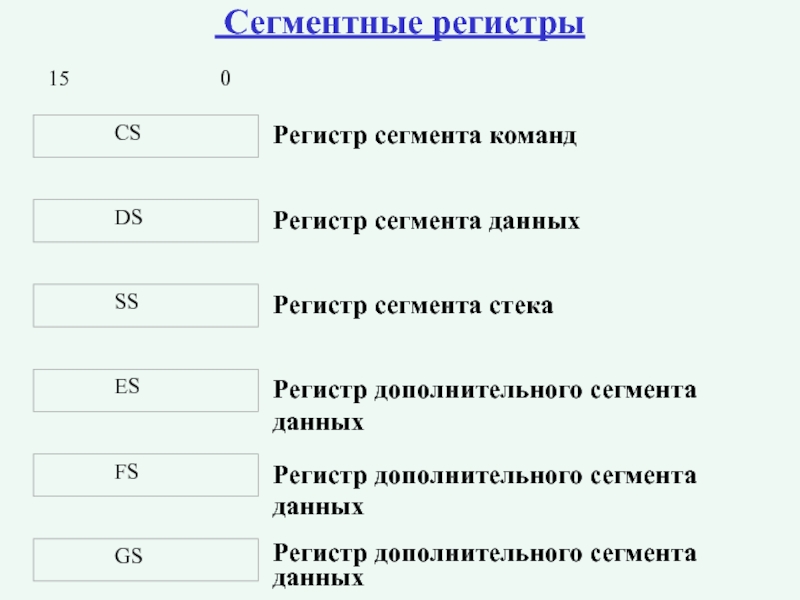

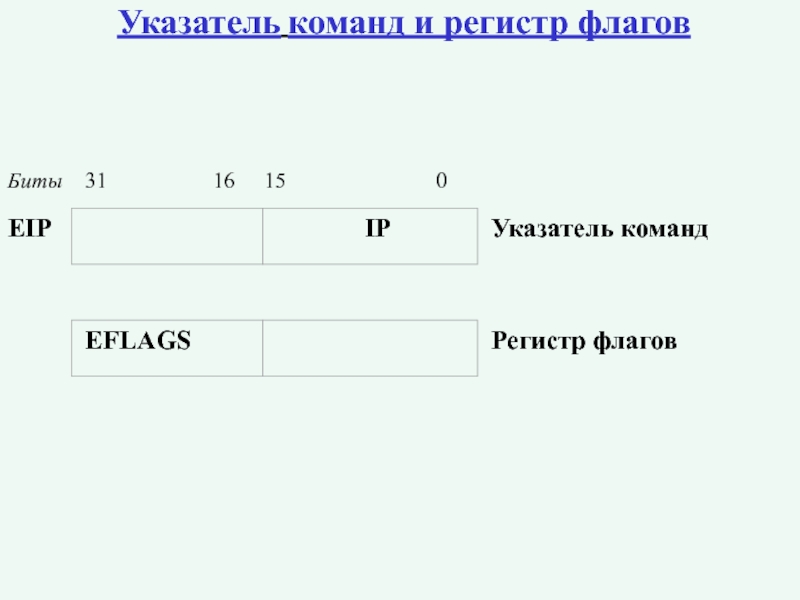

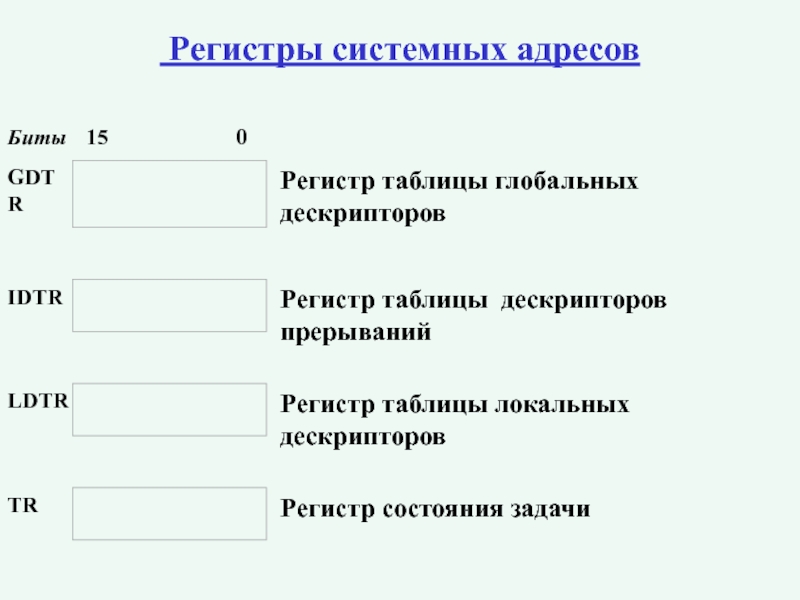

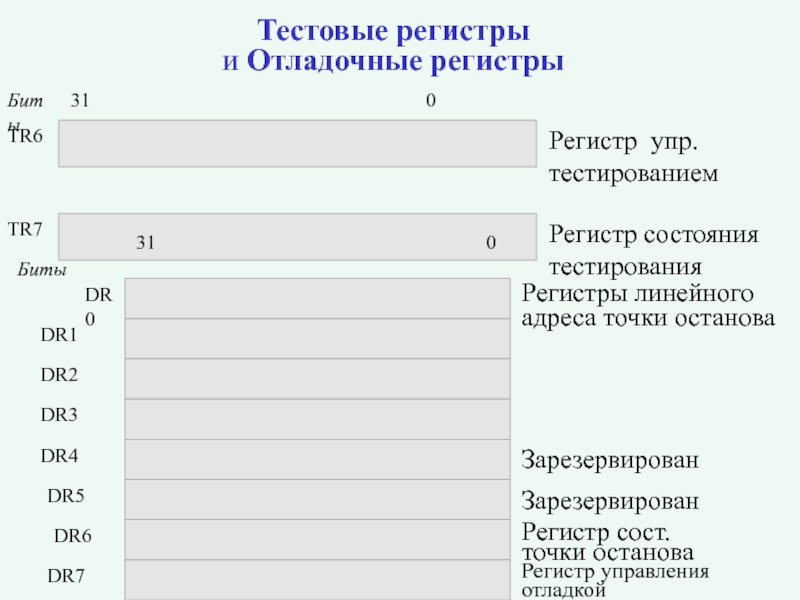

- 35. Программно-адресуемые регистры ПЭВМ.Процессор 80486 содержит 34 программно-адресуемых

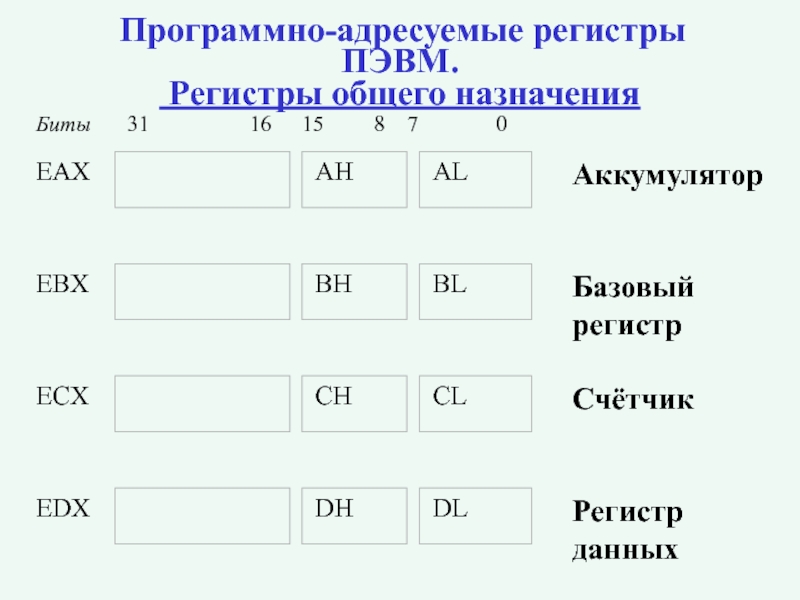

- 36. Программно-адресуемые регистры ПЭВМ. Регистры общего назначения

- 37. Регистры-указатели

- 38. Сегментные регистры

- 39. Указатель команд и регистр флагов

- 40. Регистры системных адресов

- 41. Управляющие регистры CR2 Биты31

- 42. Регистр ФлаговФлаг переноса CF (Carry Flag) индицирует

- 43. Флаг паритета PF (Parity Flag) устанавливается в

- 44. Флаги состояния автоматически устанавливаются процессором после выполнения

- 45. Тестовые регистры и Отладочные регистры

- 46. Спящий, пробудись!Мудрецы говорят: «Сон полностью исчезнет, стоит

- 47. Скачать презентанцию

Слайды и текст этой презентации

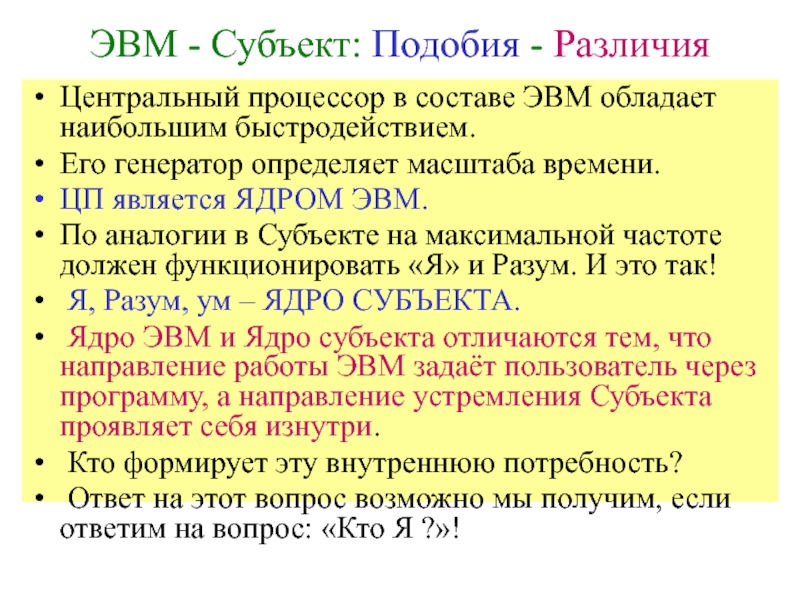

Слайд 3ЭВМ - Субъект: Подобия - Различия

Центральный процессор в составе ЭВМ

обладает наибольшим быстродействием.

Его генератор определяет масштаба времени.

ЦП является ЯДРОМ

ЭВМ.По аналогии в Субъекте на максимальной частоте должен функционировать «Я» и Разум. И это так!

Я, Разум, ум – ЯДРО СУБЪЕКТА.

Ядро ЭВМ и Ядро субъекта отличаются тем, что направление работы ЭВМ задаёт пользователь через программу, а направление устремления Субъекта проявляет себя изнутри.

Кто формирует эту внутреннюю потребность?

Ответ на этот вопрос возможно мы получим, если ответим на вопрос: «Кто Я ?»!

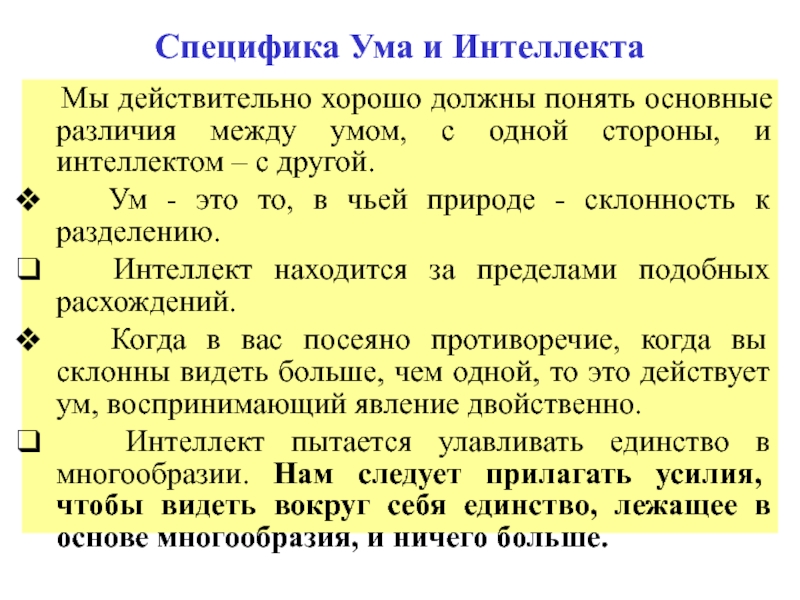

Слайд 4Специфика Ума и Интеллекта

Мы действительно хорошо должны понять

основные различия между умом, с одной стороны, и интеллектом –

с другой.Ум - это то, в чьей природе - склонность к разделению.

Интеллект находится за пределами подобных расхождений.

Когда в вас посеяно противоречие, когда вы склонны видеть больше, чем одной, то это действует ум, воспринимающий явление двойственно.

Интеллект пытается улавливать единство в многообразии. Нам следует прилагать усилия, чтобы видеть вокруг себя единство, лежащее в основе многообразия, и ничего больше.

Слайд 5

Мудрецы древности знали, что ум является инструментом, который

может связать человека или освободить его от пут. Человеку следует

осознать свой путь, так же как и их потенциальные возможности. Вы должны научится пользоваться ими, прежде чем использовать их.Именно ум плетёт узор, называемый «я». Он создаёт понятия наслаждения и боли, радости и печали, и всё множество побуждений и импульсов. Он противостоит всем попыткам ухода к Вечному, Универсальному, к Абсолюту. Он протестует, когда человек жаждет стать сознающим свою истинную личность, но когда он встречает непреклонное противостояние его тактике, он капитулирует и исчезает.

Слайд 6Содержание

Информация о видах процессоров и разновидность архитектуры.

Оперативная память и ее

типы.

Кэш память и ее особенности.

Слайд 7Процессор

Центра́льный проце́ссор (ЦП; CPU — англ. céntral prócessing únit, дословно

— центральное вычислительное устройство) — процессор машинных инструкций, часть аппаратного

обеспечения компьютера или программируемого логического контроллера, отвечающая за выполнение арифметических операций, заданных программами операционной системы, и координирующий работу всех устройств компьютера.Слайд 8Современные ЦП

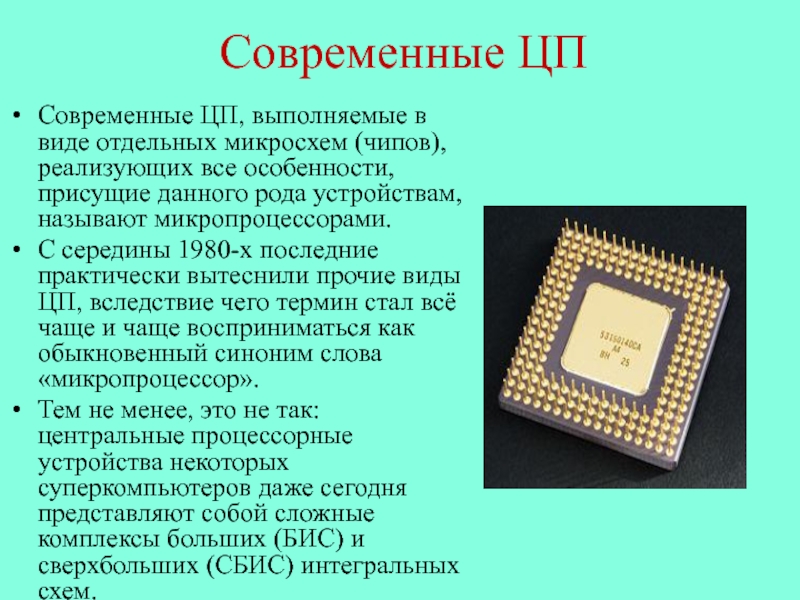

Современные ЦП, выполняемые в виде отдельных микросхем (чипов), реализующих

все особенности, присущие данного рода устройствам, называют микропроцессорами.

С середины

1980-х последние практически вытеснили прочие виды ЦП, вследствие чего термин стал всё чаще и чаще восприниматься как обыкновенный синоним слова «микропроцессор». Тем не менее, это не так: центральные процессорные устройства некоторых суперкомпьютеров даже сегодня представляют собой сложные комплексы больших (БИС) и сверхбольших (СБИС) интегральных схем.

Слайд 9Разновидности Архитектур ЦП

Архитектура фон Неймана

Конвейерная архитектура

Многоядерные процессоры

Параллельная архитектура

CISC-процессоры

RISC-процессоры

MISC-процессоры

Слайд 10Архитектура фон Неймана

Большинство современных процессоров для персональных компьютеров в общем

основаны на той или иной версии циклического процесса последовательной обработки

информации, изобретённого Джоном фон Нейманом. (с 1946г.)Отличительной особенностью архитектуры фон Неймана является то, что инструкции и данные хранятся в одной и той же памяти.

Этапы цикла выполнения:

Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса, и отдаёт памяти команду чтения;

Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности;

Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет её;

Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды;

Снова выполняется п. 1.

Слайд 11Конвейерная архитектура

Конвейерная архитектура (pipelining) была введена в центральный процессор с

целью повышения быстродействия. Обычно для выполнения каждой команды требуется осуществить

некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифрация команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера.Например, конвейер микропроцессора с архитектурой MIPS-I содержит четыре стадии:

получение и декодирование инструкции (Fetch)

адресация и выборка операнда из ОЗУ (Memory access)

выполнение арифметических операций (Arithmetic Operation)

сохранение результата операции (Store)

Некоторые современные процессоры имеют более 30 ступеней в конвейере, что увеличивает производительность процессора, однако приводит к большому времени простоя (например, в случае ошибки в предсказании условного перехода.)

Слайд 12Многоядерные процессоры

Содержат несколько процессорных ядер в одном корпусе (на одном

или нескольких кристаллах).

Процессоры, предназначенные для работы одной копии операционной системы

на нескольких ядрах, представляют собой высокоинтегрированную реализацию системы «Мультипроцессор».На данный момент массово доступны процессоры с двумя ядрами, в частности Intel Core 2 Duo на ядре Conroe и Athlon64X2 на базе микроархитектуры K8. В ноябре 2006 года вышел первый четырёхъядерный процессор Intel Core 2 Quad на ядре Kentsfield, представляющий собой сборку из двух кристаллов Conroe в одном корпусе.

10 сентября 2007 года были выпущены в продажу нативные (в виде одного кристалла) четырёхьядерные процессоры для серверов AMD Quad-Core Opteron, имевшие в процессе разработки кодовое название AMD Opteron Barсelona[1]. 19 ноября 2007 вышел в продажу четырёхьядерный процессор для домашних компьютеров AMD Quad-Core Phenom[2]. Эти процесоры реализуют новую микроархитектуру K8L (K10).

27 сентября 2006 года Intel продемонстрировала прототип 80-ядерного процессора[3]. Предполагается, что массовое производство подобных процессоров станет возможно не раньше перехода на 32-нанометровый техпроцесс, а это в свою очередь ожидается к 2010 году.

Слайд 13Параллельная архитектура

Архитектура фон Неймана обладает тем недостатком, что она последовательная.

Какой бы огромный массив данных ни требовалось обработать, каждый его

байт должен будет пройти через центральный процессор, даже если над всеми байтами требуется провести одну и ту же операцию. Этот эффект называется узким горлышком фон Неймана.Для преодоления этого недостатка предлагались и предлагаются архитектуры процессоров, которые называются параллельными. Параллельные процессоры используются в суперкомпьютерах.

Возможными вариантами параллельной архитектуры могут служить (по классификации Флинна):

SISD — один поток команд, один поток данных;

SIMD — один поток команд, много потоков данных;

MISD — много потоков команд, один поток данных;

MIMD — много потоков команд, много потоков данных.

Слайд 14CISC-процессоры

Complex Instruction Set Computing — вычисления со сложным набором команд.

Процессорная архитектура, основанная на усложнённом наборе команд. Типичными представителями CISC

является семейство микропроцессоров Intel x86 (хотя уже много лет эти процессоры являются CISC только по внешней системе команд).Слайд 15RISC-процессоры

Reduced Instruction Set Computing (technology) — вычисления с сокращённым набором

команд. Архитектура процессоров, построенная на основе сокращённого набора команд. Характеризуется

наличием команд фиксированной длины, большого количества регистров, операций типа регистр-регистр, а также отсутствием косвенной адресации. Концепция RISC разработана Джоном Коком (John Cocke) из IBM Research, название придумано Дэвидом Паттерсоном (David Patterson).Самая распространённая реализация этой архитектуры представлена процессорами серии PowerPC, включая G3, G4 и G5. Довольно известная реализация данной архитектуры — процессоры серий MIPS и Alpha.

Слайд 16MISC-процессоры

Minimum Instruction Set Computing — вычисления с минимальным набором команд.

Дальнейшее развитие идей команды Чака Мура, который полагает, что принцип

простоты, изначальный для RISC процессоров, слишком быстро отошёл на задний план. В пылу борьбы за максимальное быстродействие, RISC догнал иСлайд 17Оперативная память

Операти́вная па́мять (также ОЗУ — оперативное запоминающее устройство) —

в информатике — память, это часть системы памяти ЭВМ, в

которую процессор может обратиться за одну операцию (Jump, Move и пр.). Предназначена для временного хранения данных и команд, необходимых процессору для выполнения им операций. Оперативная память передаёт процессору команды и данные непосредственно, либо через кэш-память. Каждая ячейка оперативной памяти имеет свой индивидуальный адрес.Слайд 18

В современных вычислительных устройствах, оперативная память выполнена по технологии динамической

памяти с произвольным доступом (англ. dynamic random access memory, DRAM).

Понятие памяти с произвольным доступом предполагает, что текущее обращение к памяти не учитывает порядок предыдущих операций и расположения данных в ней. ОЗУ может изготавливаться как отдельный блок, или входить в конструкцию однокристальной ЭВМ или микроконтроллера.Ячейка памяти — часть запоминающего устройства ЭВМ для хранения 1 машинного слова (числа) или его части (например, 1 байта). Общее число ячеек памяти всех запоминающих устройств определяет ёмкость памяти ЭВМ.

Слайд 20Кэш память

Впервые слово «кэш» в компьютерном контексте было использовано в

1967 году во время подготовки статьи для публикации в журнале

«IBM Systems Journal». Статья касалась усовершенствования памяти в разрабатываемой модели 85 из серии IBM System/360. Редактор журнала Лайл Джонсон попросил придумать более описательный термин, нежели «высокоскоростной буфер», но из-за отсутствия идей сам предложил слово «кэш». Статья была опубликована в начале 1968 года, авторы были премированы IBM, их работа получила распространение и впоследствии была улучшена, а слово «кэш» вскоре стало использоваться в компьютерной литературе как общепринятый термин.Слайд 21

Кэш — это память с большей скоростью доступа, предназначенная для

ускорения обращения к данным, содержащимся постоянно в памяти с меньшей

скоростью доступа (далее «основная память»). Кэширование применяется ЦПУ, жёсткими дисками, браузерами и веб-серверами.Быстродействие современных процессоров во многом обусловлено наличием в них встроенной Кэш памяти.

Слайд 22РЕГИСТРОВАЯ КЭШ-ПАМЯТЬ

Регистровая КЭШ-память - высокоскоростная память сравнительно большой емкости, являющаяся

буфером между ОП и МП и позволяющая увеличить скорость выполнения

операций. Создавать ее целесообразно в ПК с тактовой частотой задающего генератора 40 МГц и более. Регистры КЭШ-памяти недоступны для пользователя, отсюда и название КЭШ (Cache), в переводе с английского означает "тайник".Слайд 23Два типа КЭШ-памяти

КЭШ-память "с обратной записью" - результаты операций прежде,

чем их записать в ОП, фиксируются в КЭШ-памяти, а затем

контроллер КЭШ-памяти самостоятельно перезаписывает эти данные в ОП;КЭШ-память "со сквозной записью" - результаты операций одновременно, параллельно записываются и в КЭШ-память, и в ОП.

Слайд 24 ЭВМ и С Лекция № 6. Реферат.

Центральный

процессора (ЦП)

предназначен для:

обработки потока команд и данных,

считанных из ОП;организации обмена данными между Каналами и ОП;

обработки внутренних и внешних прерываний ЭВМ;

обработки ошибок и сбоев, возникающих в ЭВМ;

диагностирования оборудования ЭВМ;

организации общения оператора или инженера с ЭВМ ;

организации связи между процессорами в ВК.

Слайд 25К блоку систем-ных средств

БК -

буфер каналов

АП -

адаптер памяти

УБ- управление

буферной памятью

БИ, АД -блоки команд и адресов данных

БП -блок прерываний

МП

местная память

МУ

микропрограммного управления

ПМ - память микропрограмм

ТМ,ВС - таймеров, внешних связей

БА -блок арифме-тики

УМ

ускоренного умножения

ПУ, КД

пульт управления, блок контроля и диагностики

Каналы

Структурная схема ЦП ЭВМ общего назначения

Прользователь Каналы Блоки оперативной памяти

Слайд 26Управление памятью

Блоки Управление памятью предназначен для связи

с учётом приоритетов Каналов и ЦП с блоками ОП.

АП- приём

запросов, адреса и информации от УБ, обращение к блокам ОП, четырёхкратное расслоение памяти, контроль по коду Хемминга.БК- приём запросов, адреса и информации от каналов, буферирование четырёх двойных слов, передачу через УБ в каналы.

УБ- основной в группе Управление памятью, включает: буферную память 8К байт; матрицу адресов; преобразование логических адресов в физические; память ключей защиты.

Слайд 27Центральное управление

Группа блоков Центральное управление обрабатывает поток команд,

адреса операндов, обращение в основную и местную память, прерываний, формирование

сигналов управления, отсчёт реального и относительных интервалов времени, организацию мультипроцессорной системы.БИ,АД- основные, включают: регистр ССП; счётчик команд; буфер команд; регистры прохождения команд по уровням обработки; регистры адресов обращения в память. Этапы: распаковка из буфера; считывание операндов; выполнение и запись. Параллельное формирование адреса следующего участка программы.

Слайд 28Центральное управление (продолжение)

МП- 16 регистров общего назначения (РОН)и 4 регистра

с плавающей запятой (РПЗ). Считывание по адресу из БИ.

БП- прерывания

внутренние, от Каналов, внешних.. Приоритеты. Формирование адреса записи/ считывания ССП.ПМ- память микропрограмм включает 4096 слов по 144 разряда.

МУ- формирует с учётом схемных условий адрес микрокоманд, дешифрирует поля микрокоманд. Микропрограммное управление охватывает все блоки ЦП.

ТМ- счётчик времени дня, таймер, интервальный таймер, компаратор. Использует для обновления БА.

ПУ,КД- связаны со всеми блоками ЦП.

Слайд 30Интерфейс магистрали

Синхросигнал (тактирует пер. фронт, диап. ст.

0,1%) Подт.

Кода адр.

Цик. Магистрали Конец передачи

Прерывания

Управление внутренней кеш

Обработка ошибок

FPY(пл.т)Маска лин. А20: эмулитует циклическое адр. Пр.(1Мб)МП8083

Арбитраж магистрали:

BREQ –запрос магист. от МП ;

HOLD – запрос маг. от внешнего устр.

Слайд 34Эффективность ЦП

На эффективность ЦП влияют следующие

особенности структуры:

• разрядность трактов передачи и обработки данных;

• число уровней

совмещения обработки команд;• структура и алгоритмы работы исполнительных блоков;

• организация выполнения команд передачи управления;

• организация внутренней памяти процессора;

• степень совмещения использования оборудования процессора и каналов.

Слайд 35Программно-адресуемые регистры ПЭВМ.

Процессор 80486 содержит 34 программно-адресуемых регистра. с точки

зрения программиста 24 из них являются 32-разрядными, а 10 регистров

16- разрядные.Регистры принято объединять в семь групп: регистры общего назначения ( или регистры данных ), регистры-указатели, сегментные регистры, управляющие регистры, регистры системных адресов, отладочные регистры и тестовые регистры.

Кроме того, в отдельную группу выделяют счётчик команд и регистр флагов.

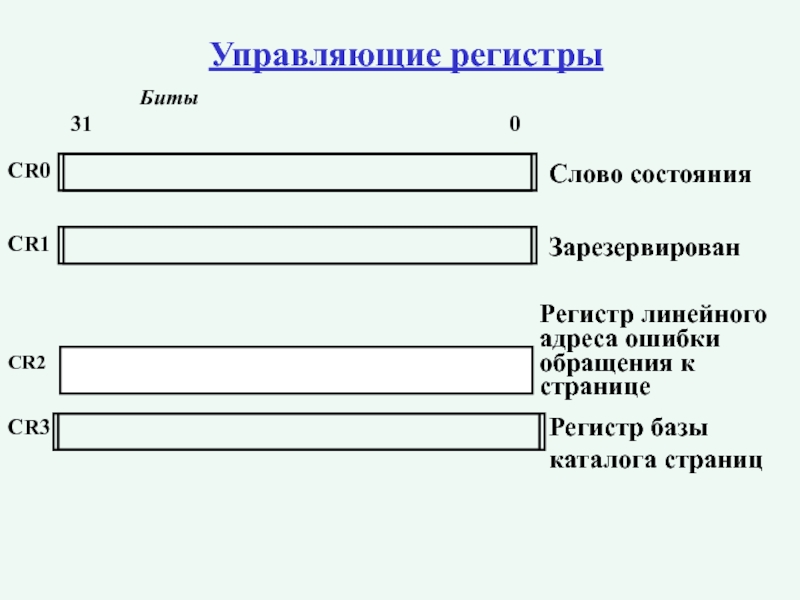

Слайд 41Управляющие регистры

CR2

Биты

31

0

CR0

Слово состояния

CR1

Зарезервирован

Регистр линейного адреса ошибки обращения к странице

CR3

Регистр базы каталога страниц

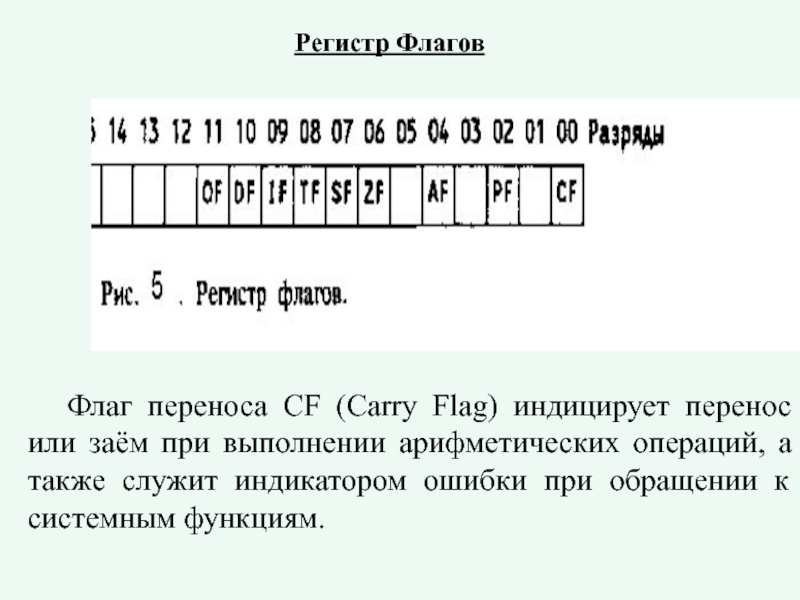

Слайд 42Регистр Флагов

Флаг переноса CF (Carry Flag) индицирует перенос или заём

при выполнении арифметических операций, а также служит индикатором ошибки при

обращении к системным функциям.Слайд 43

Флаг паритета PF (Parity Flag) устанавливается в 1, если младшие

8 бит результата операции содержат четное число двоичных единиц.

Флаг вспомогательного

переноса AF (Auxiliary Flag) используется в операциях над упакованными двоично-десятичными числами. Он индицирует перенос или заем из старшей тетрады (бита 3). Флаг нуля ZF (Zero Flag) устанавливается в 1, если резуьтат операции равен 0.

Флаг знака SF (Sign Flag) показывает знак результата операции, устанавливаясь в 1 при отрицательном результате.

Флаг переполнения OF (Overflow Flag) фиксирует переполнение, т.е. выход результата операции за пределы допустимого для данного процессора диапазона значений.

Слайд 44

Флаги состояния автоматически устанавливаются процессором после выполнения каждой команды. Так,

если в регистре AX держится число 1, то после выполнения

команды декремента (уменьшения содержимого АХ на 1) dec AXсодержимое АХ станет равно 0, и процессор сразу отметит этот факт, установив в регистре флагов бит ZF (флаг нуля) Если попытаться сложить два больших числа (например, 50000 и 60000), то установится флаг переноса CF, так как число 110000, получающееся в результате сложения, должно занять больше двоичных разрядов, чем помещается в регистрах или ячейках памяти, и возникает "перенос" старшего бита этого числа в бит CF регистра флагов.Индицирующие флаги процессора дают возможность проанализировать, если это нужно, результат последней операции и осуществить "разветвление" программы.

Слайд 46Спящий, пробудись!

Мудрецы говорят: «Сон полностью исчезнет, стоит Вам проснуться». Какова

причина сновидения? Его причина – сон. Соответственно, пробуждение заставляет сон

исчезнуть.Что приводит к возникновению этого мира? Долгий сон наяву. А исчезновение этого мира –такого, какого мы видим, - это пробуждение к освобождённому состоянию.

И тогда мы продолжаем видеть всё, как и раньше: людей, горы, машины,…- но вдобавок к форме мы начинаем видеть и единую основу. Имя и форма меняются, но основа, поддерживающая всё остальное, - остаётся.

Это приведёт к успокоению Ума и торжеству Разума!