Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Конвейер. Типы конфликтов

Содержание

- 1. Конвейер. Типы конфликтов

- 2. Конвейер инструкцийСтадии:Выборка инструкций.Выборка данных из регистров и

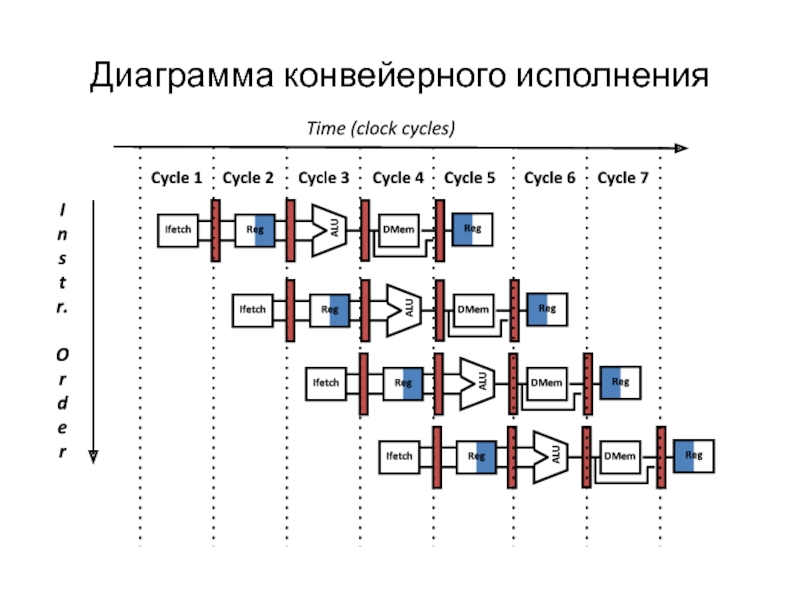

- 3. Диаграмма конвейерного исполненияInstr.OrderTime (clock cycles)

- 4. Что препятствует эффективному исполнению инструкций на конвейере?Зависимости

- 5. КонфликтКонфликты – это некоторая ситуация, при которой

- 6. Типы конфликтов.Структурные конфликтыРазным инструкциям требуется доступ к

- 7. Конфликты по данным.RAW (read after write). Чтение поле записи.i.R2

- 8. Способы разрешения конфликтов.ПрограммныеОбнаружение конфликтов в процессе компиляции

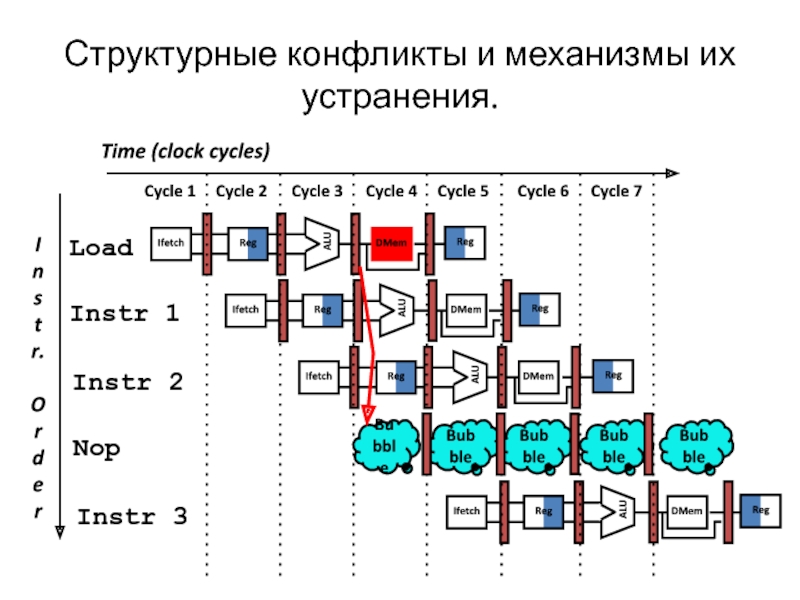

- 9. Структурные конфликты и механизмы их устранения.Instr.OrderTime (clock

- 10. Структурные конфликты и механизмы их устранения.Instr.OrderTime (clock

- 11. Структурные конфликты и механизмы их устранения.Второй способ

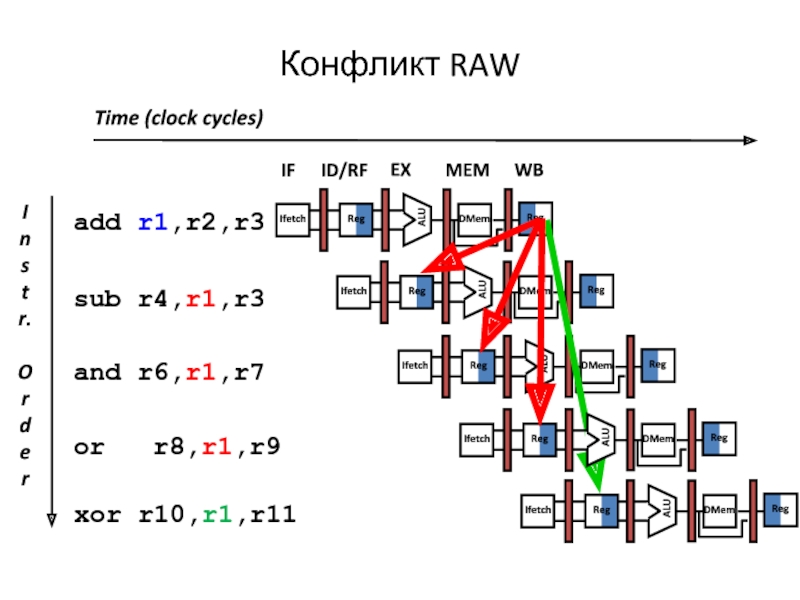

- 12. Конфликт RAWTime (clock cycles)

- 13. Конфликт RAWTime (clock cycles)

- 14. Устранение RAW конфликтов методом bypass Метод Bypass

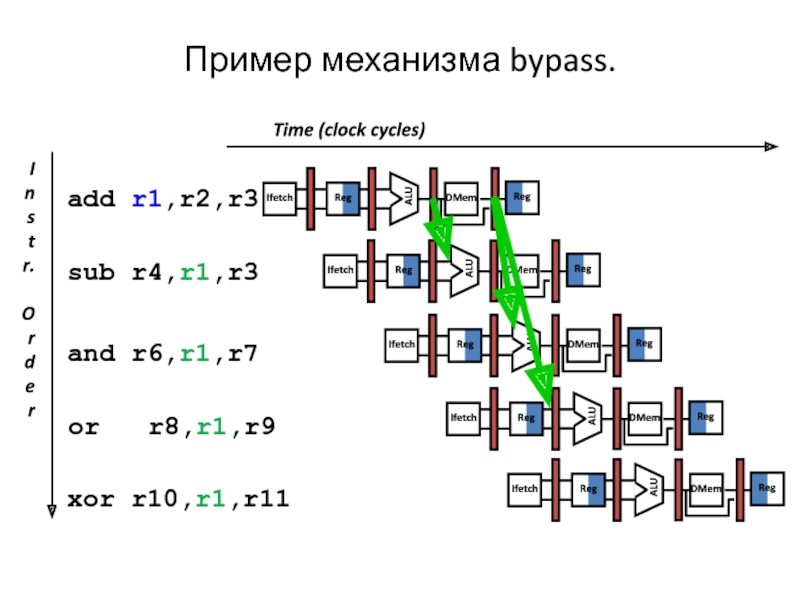

- 15. Пример механизма bypass.Time (clock cycles)

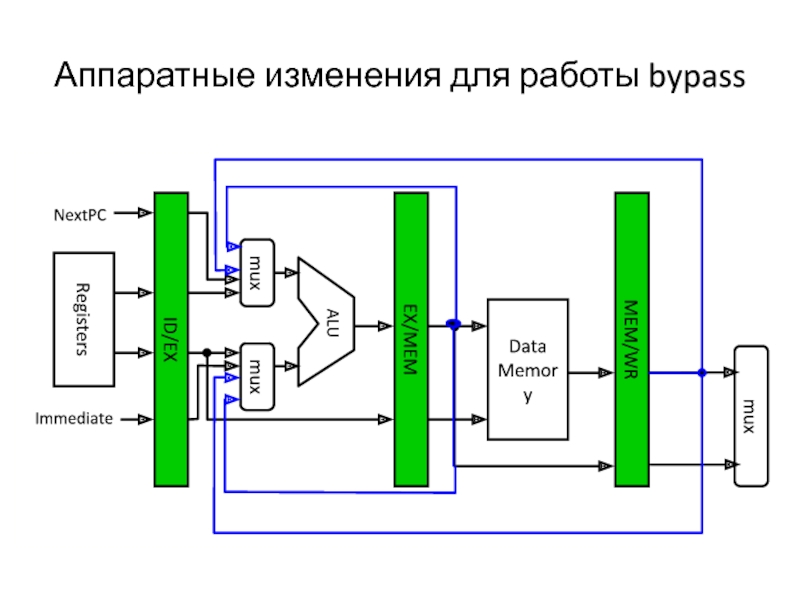

- 16. Аппаратные изменения для работы bypassMEM/WRID/EXEX/MEM DataMemorymuxmuxRegistersNextPCImmediatemux

- 17. Ограничения bypass (проблема загрузки)Time (clock cycles)

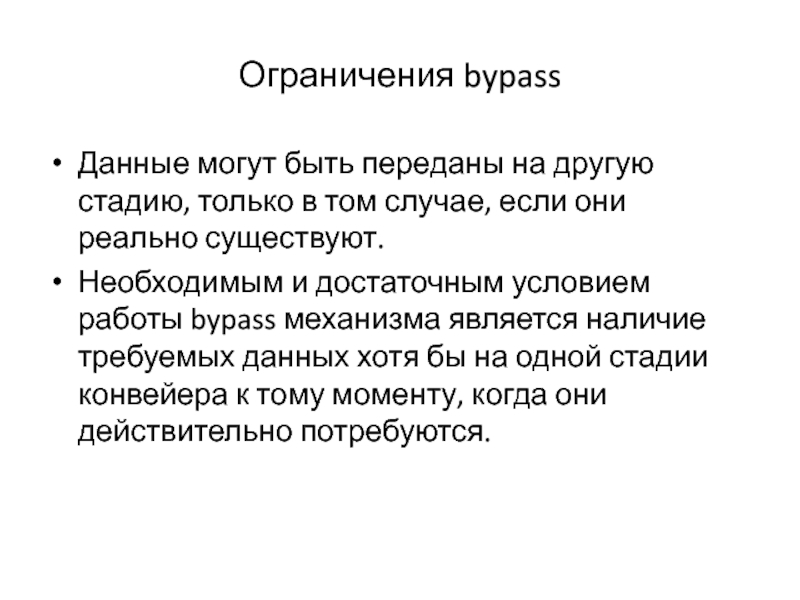

- 18. Ограничения bypassДанные могут быть переданы на другую

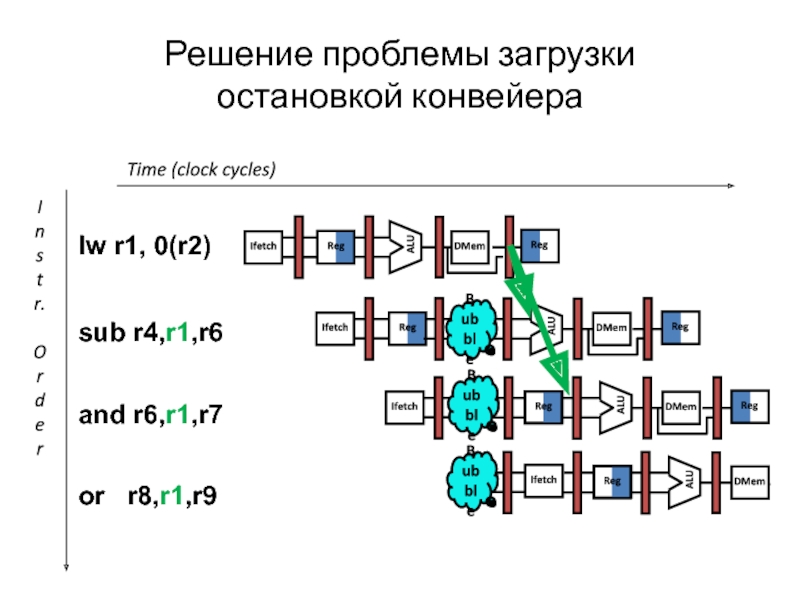

- 19. Решение проблемы загрузки остановкой конвейераTime (clock cycles)or r8,r1,r9Instr.Orderlw r1, 0(r2)sub r4,r1,r6and r6,r1,r7ALUDMemBubble

- 20. Статическое планирование конвейераЭто программный подход, который сводиться

- 21. Конфликт управленияTime (clock cycles)

- 22. Как уменьшить количество тактов простояAdderMemoryAccessWriteBackInstructionFetchInstr. DecodeReg. FetchExecuteAddr. CalcMemoryReg FileMUXDataMemoryMUXSignExtendZero?Next SEQ PCRDRDRDWB DataNext PCRS1RS2ImmMUX

- 23. Динамическое планирование исполнения инструкцийИдея динамического планирования в

- 24. Конфликты связанные с внеочередным исполнениемПример:DIV.D F0,F2,F4ADD.D F6,F0,F8SUB.D

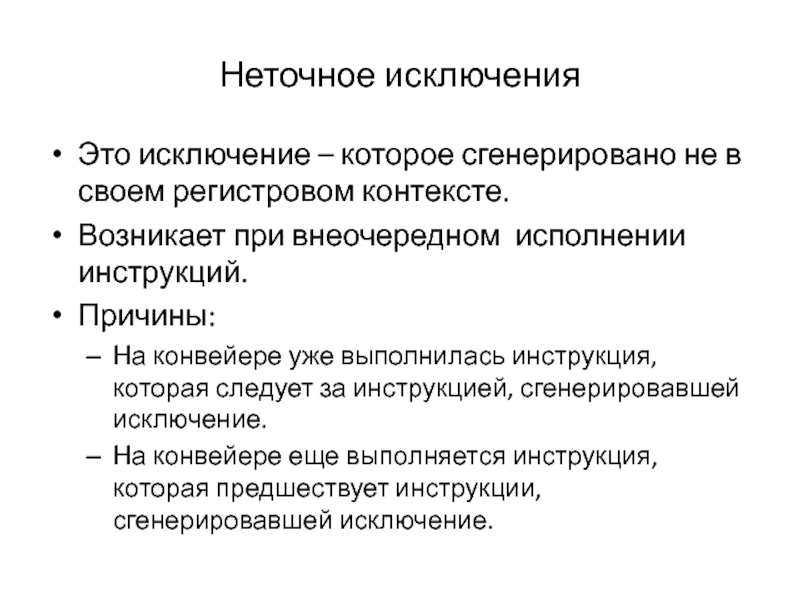

- 25. Неточное исключенияЭто исключение – которое сгенерировано не

- 26. Скачать презентанцию

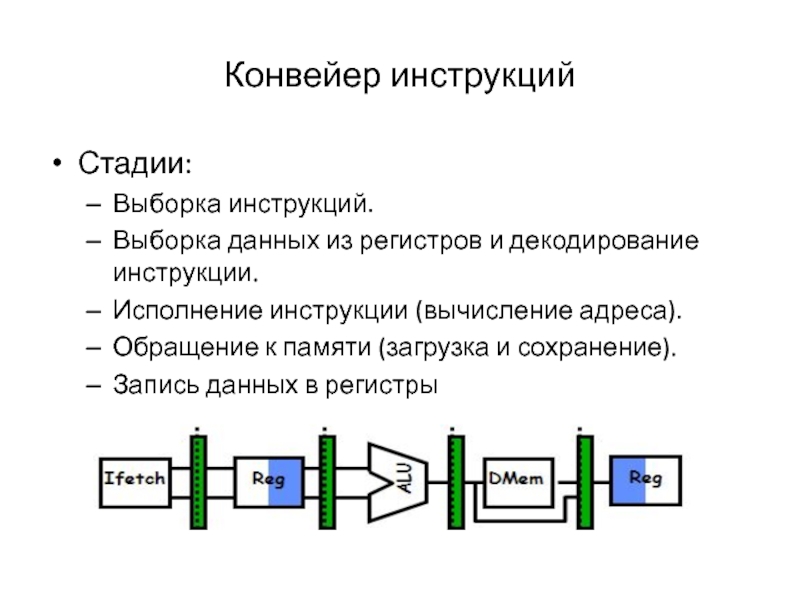

Конвейер инструкцийСтадии:Выборка инструкций.Выборка данных из регистров и декодирование инструкции.Исполнение инструкции (вычисление адреса).Обращение к памяти (загрузка и сохранение).Запись данных в регистры

Слайды и текст этой презентации

Слайд 1Конвейер

Характеристики:

Латентность

Пропускная способность

Не конвейер

Для быстрого выполнения малого количества

операций

больше чем у не конвейерной реализации.Слайд 2Конвейер инструкций

Стадии:

Выборка инструкций.

Выборка данных из регистров и декодирование инструкции.

Исполнение инструкции

(вычисление адреса).

Обращение к памяти (загрузка и сохранение).

Запись данных в регистры

Слайд 4Что препятствует эффективному исполнению инструкций на конвейере?

Зависимости между инструкциями.

Наличие зависимостей

приводит к возникновению конфликтов (hazard).

Слайд 5Конфликт

Конфликты – это некоторая ситуация, при которой не возможно запустить

следующую инструкцию непосредственно за предыдущий, не нарушив критерия сохранения корректности

программы.Запуск инструкции происходит спустя n тактов.

Конфликты – это не атрибут программы или алгоритма, это следствие параллельного исполнения зависимых инструкций на процессоре.

Слайд 6Типы конфликтов.

Структурные конфликты

Разным инструкциям требуется доступ к одному ресурсу процессора.

Конфликты

по данным

Следствие наличия зависимостей по данным именам.

Конфликты по управлению

Следствие наличия

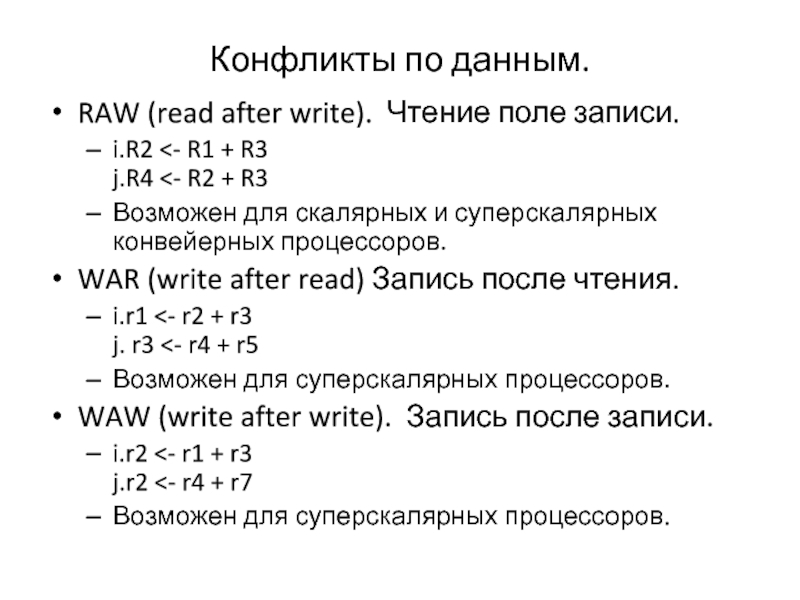

зависимости по управлению.Слайд 7Конфликты по данным.

RAW (read after write). Чтение поле записи.

i.R2

R1 + R3 j.R4

суперскалярных конвейерных процессоров.WAR (write after read) Запись после чтения.

i.r1 <- r2 + r3 j. r3 <- r4 + r5

Возможен для суперскалярных процессоров.

WAW (write after write). Запись после записи.

i.r2 <- r1 + r3 j.r2 <- r4 + r7

Возможен для суперскалярных процессоров.

Слайд 8Способы разрешения конфликтов.

Программные

Обнаружение конфликтов в процессе компиляции и добавление инструкций

nop.

Статическое планирование конвейера.

Аппаратные

Добавление устройства обнаружения конфликтов и останова конвейера.

Добавление специфичных

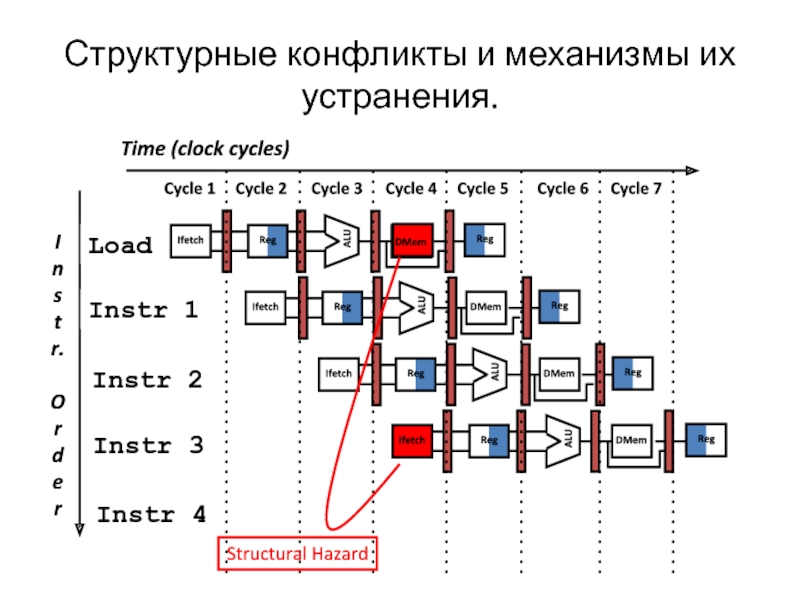

аппаратных решений.Слайд 9Структурные конфликты и механизмы их устранения.

I

n

s

t

r.

O

r

d

e

r

Time (clock cycles)

Load

Instr 1

Instr 2

Instr

3

Instr 4

DMem

Cycle 1

Cycle 2

Cycle 3

Cycle 4

Cycle 6

Cycle 7

Cycle 5

Слайд 10Структурные конфликты и механизмы их устранения.

I

n

s

t

r.

O

r

d

e

r

Time (clock cycles)

Load

Instr 1

Instr 2

Nop

Instr

3

DMem

Cycle 1

Cycle 2

Cycle 3

Cycle 4

Cycle 6

Cycle 7

Cycle 5

Слайд 11Структурные конфликты и механизмы их устранения.

Второй способ устранения приводит к

добавлению второго канала к памяти, разделению общего кэша на кэш

данных и кэш инструкций.Слайд 14Устранение RAW конфликтов методом bypass

Метод Bypass сводиться к возможности

передачи данных между стадиями конвейера напрямую.

Вход стадии может быть соединен

с выходом любой последующей стадии.Слайд 16Аппаратные изменения для работы bypass

MEM/WR

ID/EX

EX/MEM

Data

Memory

mux

mux

Registers

NextPC

Immediate

mux

Слайд 18Ограничения bypass

Данные могут быть переданы на другую стадию, только в

том случае, если они реально существуют.

Необходимым и достаточным условием работы

bypass механизма является наличие требуемых данных хотя бы на одной стадии конвейера к тому моменту, когда они действительно потребуются. Слайд 19Решение проблемы загрузки

остановкой конвейера

Time (clock cycles)

or r8,r1,r9

I

n

s

t

r.

O

r

d

e

r

lw r1,

0(r2)

sub r4,r1,r6

and r6,r1,r7

ALU

DMem

Bubble

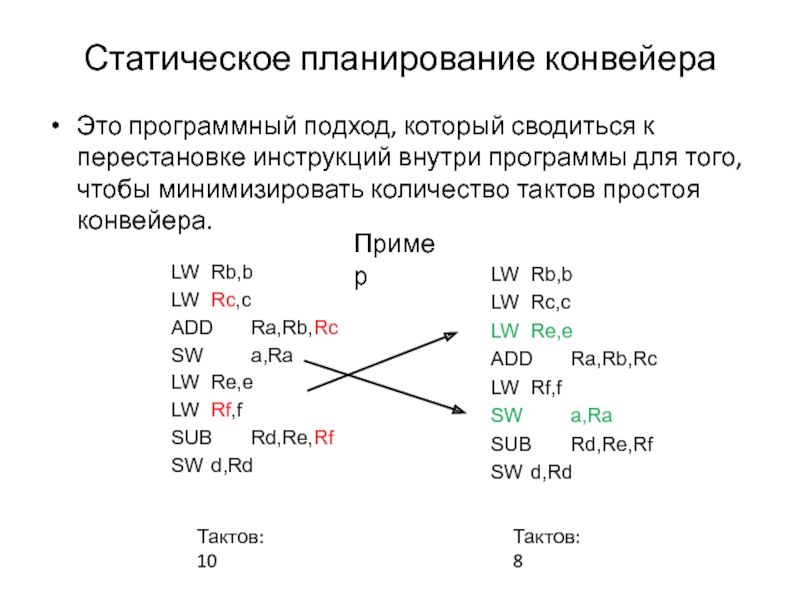

Слайд 20Статическое планирование конвейера

Это программный подход, который сводиться к перестановке инструкций

внутри программы для того, чтобы минимизировать количество тактов простоя конвейера.

LW

Rb,bLW Rc,c

ADD Ra,Rb,Rc

SW a,Ra

LW Re,e

LW Rf,f

SUB Rd,Re,Rf

SW d,Rd

LW Rb,b

LW Rc,c

LW Re,e

ADD Ra,Rb,Rc

LW Rf,f

SW a,Ra

SUB Rd,Re,Rf

SW d,Rd

Тактов: 10

Тактов: 8

Пример

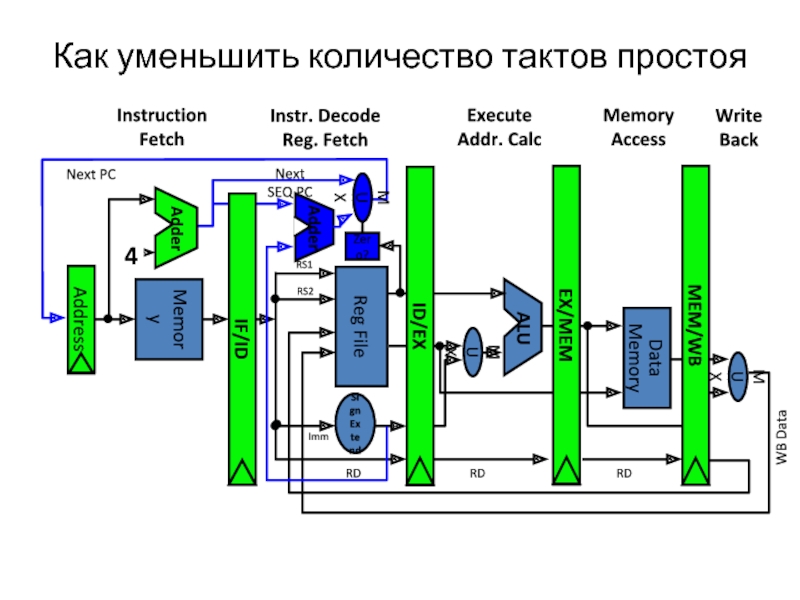

Слайд 22Как уменьшить количество тактов простоя

Adder

Memory

Access

Write

Back

Instruction

Fetch

Instr. Decode

Reg. Fetch

Execute

Addr. Calc

Memory

Reg File

MUX

Data

Memory

MUX

Sign

Extend

Zero?

Next SEQ

PC

RD

RD

RD

WB Data

Next PC

RS1

RS2

Imm

MUX

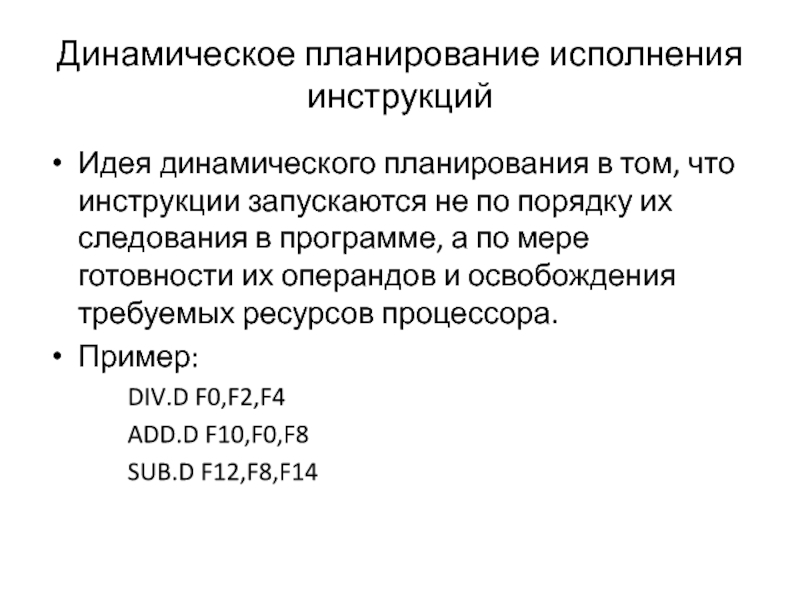

Слайд 23Динамическое планирование исполнения инструкций

Идея динамического планирования в том, что инструкции

запускаются не по порядку их следования в программе, а по

мере готовности их операндов и освобождения требуемых ресурсов процессора.Пример:

DIV.D F0,F2,F4

ADD.D F10,F0,F8

SUB.D F12,F8,F14

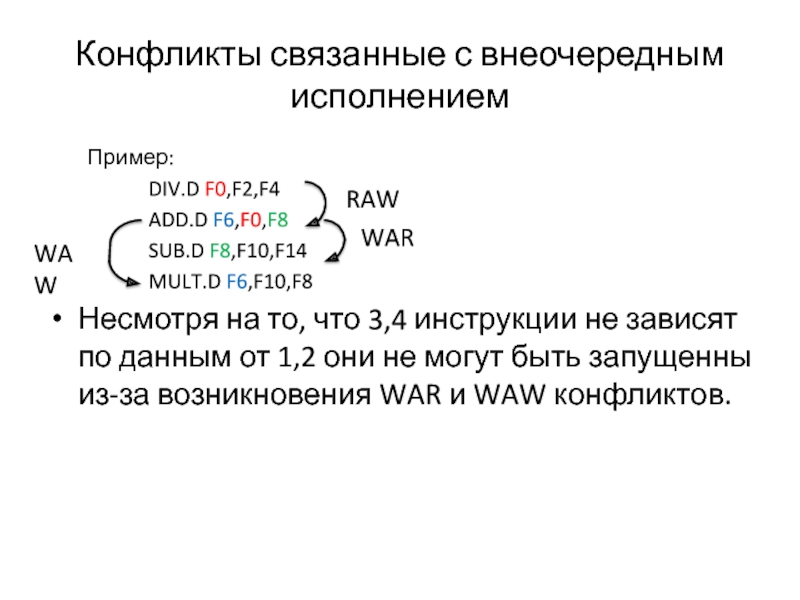

Слайд 24Конфликты связанные с внеочередным исполнением

Пример:

DIV.D F0,F2,F4

ADD.D F6,F0,F8

SUB.D F8,F10,F14

MULT.D F6,F10,F8

Несмотря на

то, что 3,4 инструкции не зависят по данным от 1,2

они не могут быть запущенны из-за возникновения WAR и WAW конфликтов.RAW

WAR

WAW

Слайд 25Неточное исключения

Это исключение – которое сгенерировано не в своем регистровом

контексте.

Возникает при внеочередном исполнении инструкций.

Причины:

На конвейере уже выполнилась

инструкция, которая следует за инструкцией, сгенерировавшей исключение.На конвейере еще выполняется инструкция, которая предшествует инструкции, сгенерировавшей исключение.