памяти представляет собой аппаратный механизм, позволяющий операционной системе создавать для

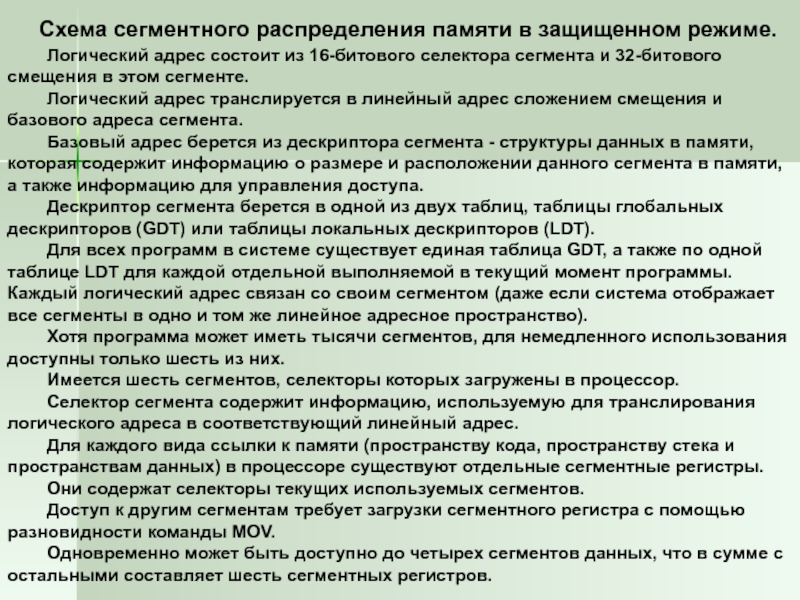

выполняющихся программ упрощенную среду. Например, при одновременном выполнении нескольких программ каждой из них должно быть дано независимое адресное пространство. При разделении всеми этими программами одного и того же адресного пространства каждая из них должна была бы выполнять сложные и занимающие много процессорного времени проверки, чтобы избежать влияния на другие программы.Организация памяти состоит из сегментации и подкачки страниц. Сегментация служит для того, чтобы дать каждой программе несколько независимых, защищенных адресных пространств.

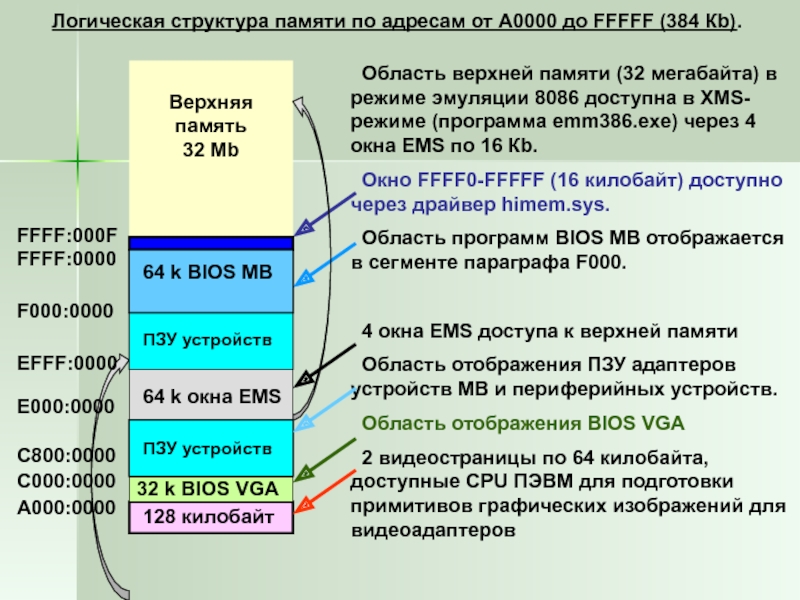

Подкачка страниц используется для поддержки среды, в которой большие адресные пространства моделируются на базе небольшой области оперативной памяти и некоторой дисковой памяти. Разработчики систем могут использовать как оба этих механизма, так и любой из них. При одновременном выполнении нескольких программ для защиты программ от влияния на них других программ можно использовать любой механизм.

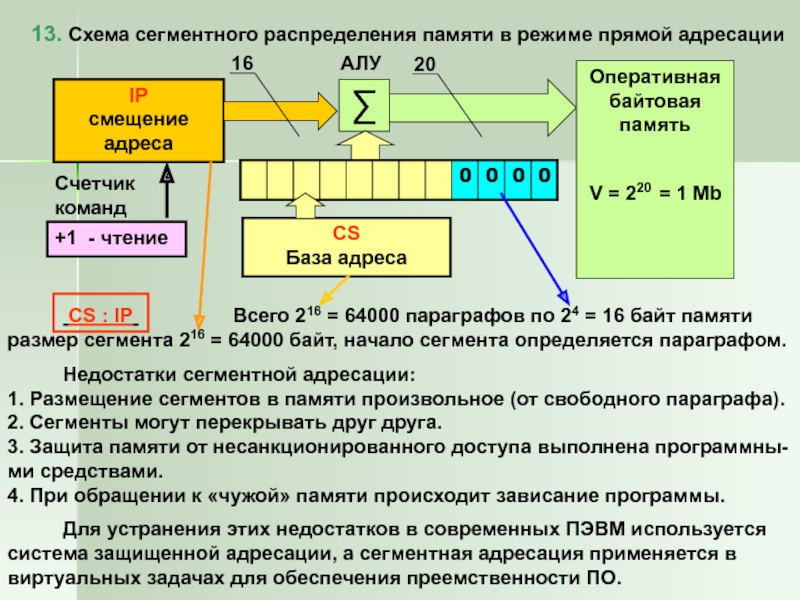

Сегментация позволяет иметь полностью неструктурированную и простую память, подобную модели памяти 8-битового процессора, либо высоко структурированную память, с использованием трансляции адресов и защиты.

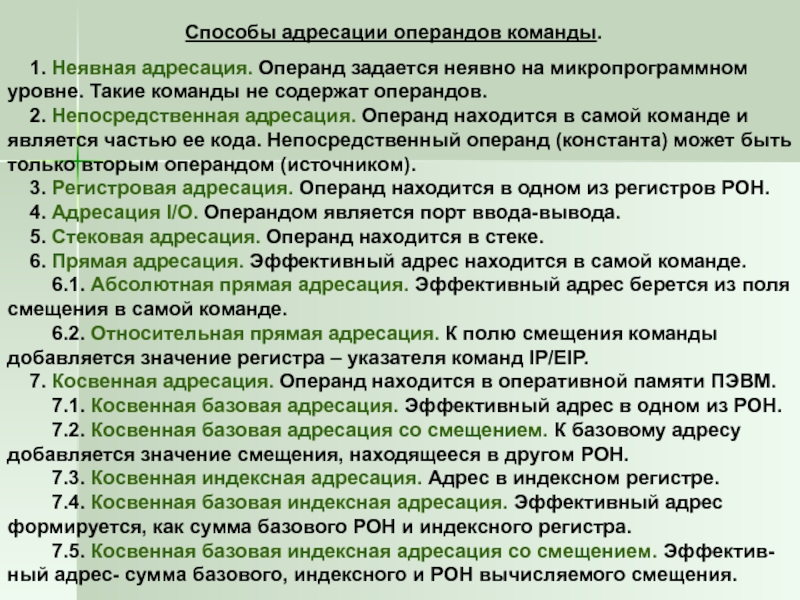

Средства организации памяти работают с единицами, которые называются сегментами.

Каждый сегмент представляет собой независимое, защищенное адресное пространство.

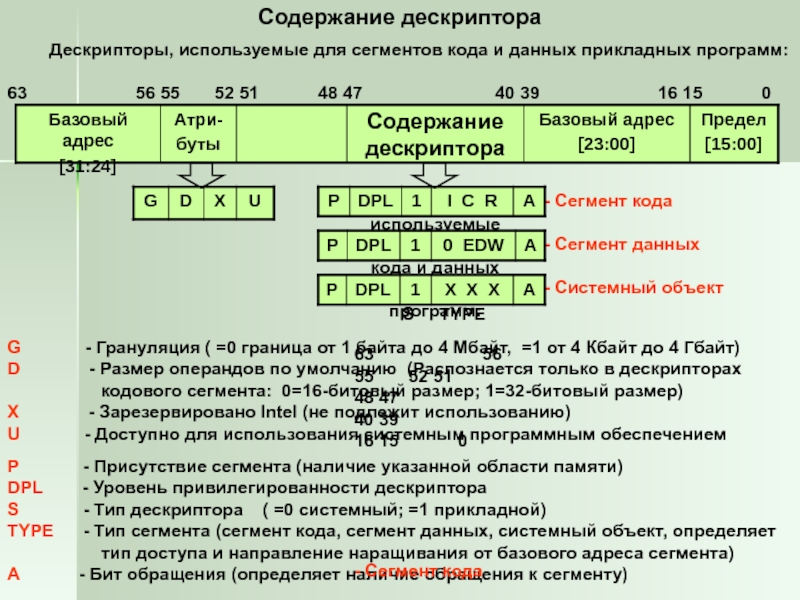

Доступ к сегментам управляется данными, в которых описаны их размер, уровень привилегированности, который нужен для доступа к ним, типы ссылок к памяти, применимые к этому сегменту (выборка команды, помещение или извлечение из стека, операция чтения, операция записи и т.д.), а также его присутствие в памяти.

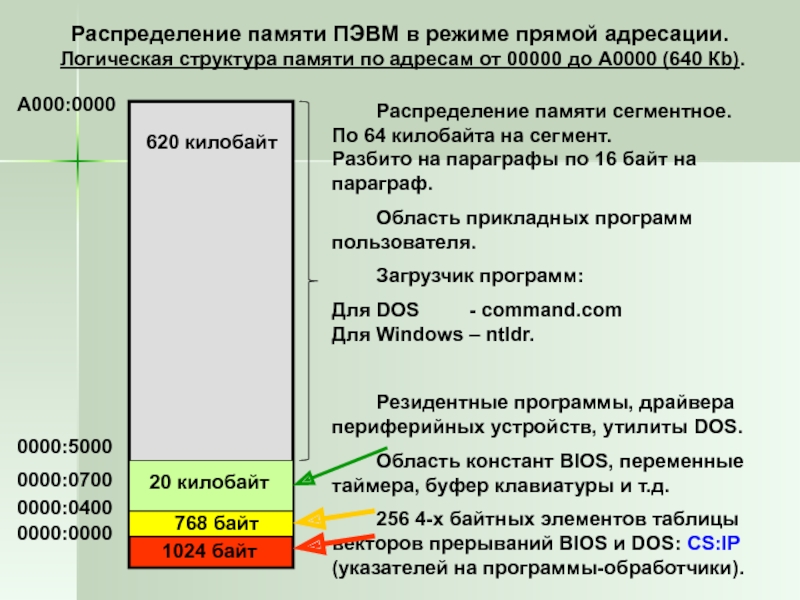

В случае простой архитектуры памяти все адреса относятся к одному и тому же адресному пространству. Это модель памяти, используемая 8-битовыми микропроцессорами, такими как 8080, где логический и физический адреса совпадают.

Процессор х86 может быть использован подобным же образом посредством отображения всех сегментов в одном и том же адресном пространстве и запрещения подкачки страниц памяти.

Такая модель может понадобиться при адаптации старых разработок для 32-разрядного процессора.