одним битом информации (ноль — единица).

Числа, адреса, команды представляются в

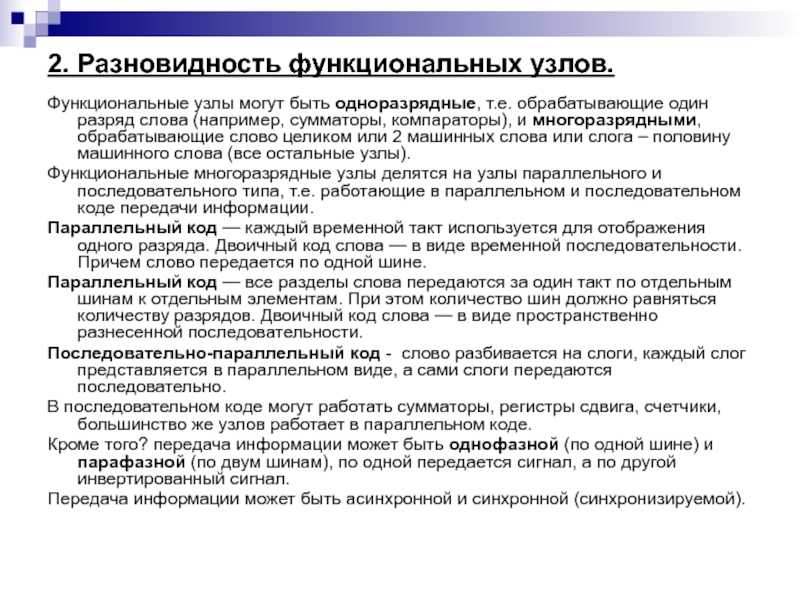

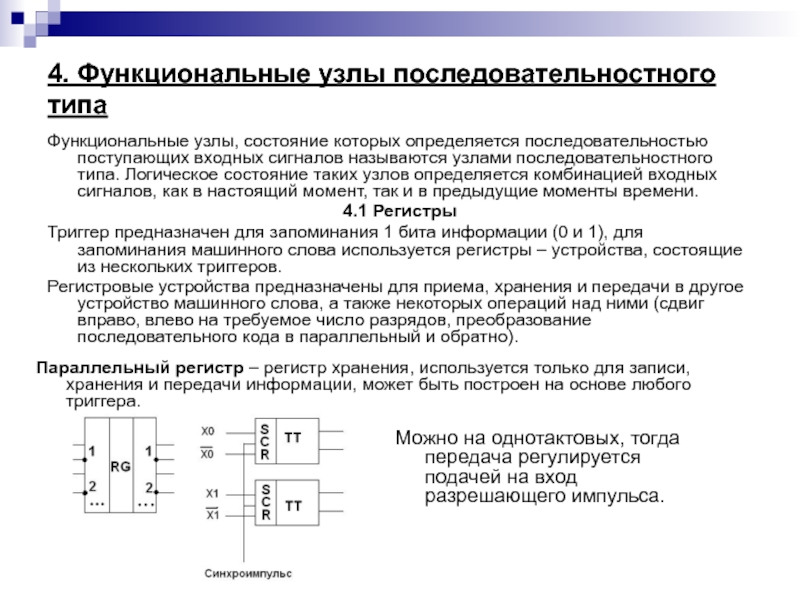

виде машинного слова, т.е. Совокупности нулей и единиц. Интерес представляет обработка и передача не одного бита, а их совокупности, т.е. машинного слова, включающей 16, 32, 64 бита.Совокупность логических (функциональных) элементов, часть логической (функциональной) схемы, описывающая одну или несколько логических функций, объединенных в одно целое, называется функциональным узлом.

Т.е. функциональный узел — можно изобразить с помощью совокупности элементов или в виде одного графического символа.

Еще одно определение: функциональный узел — это совокупность логических элементов, обеспечивающих выполнение определенной операции.

x1 y1

x2 F y2

xn yn

Обозначение функциональных узлов: xi – входные параметры, yj - выходные параметры, F – название или условное обозначение узла.