Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

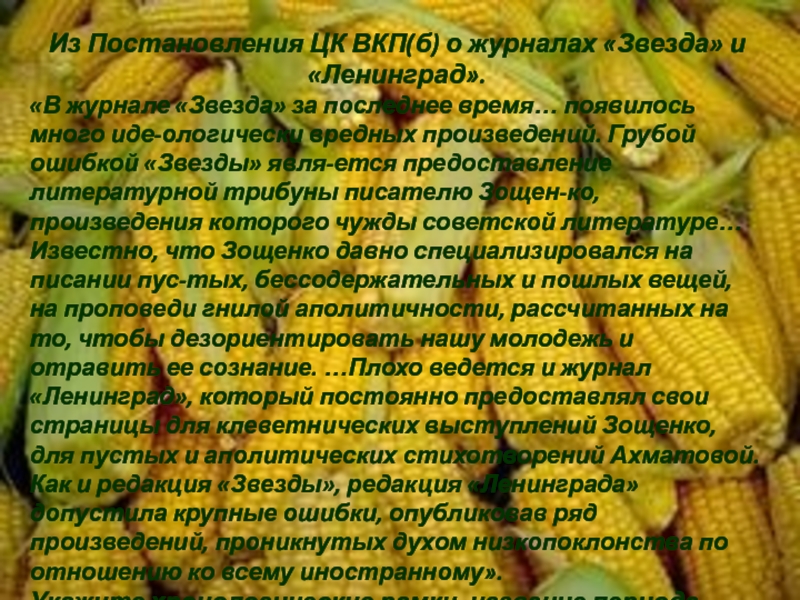

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

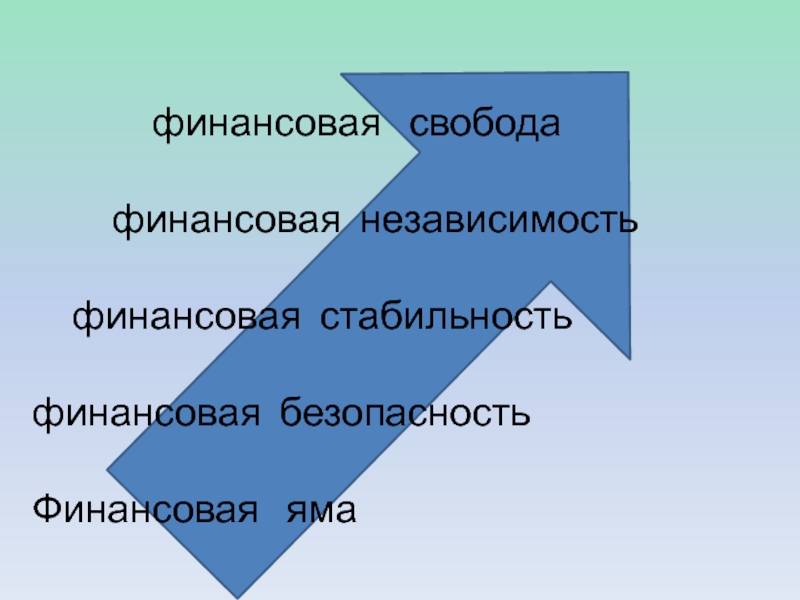

- Экономика

- Юриспруденция

Раздел 3: Элементы и комбинационные узлы цифровых устройств. Лекция 4. Вопросы:

Содержание

- 1. Раздел 3: Элементы и комбинационные узлы цифровых устройств. Лекция 4. Вопросы:

- 2. Мобильный телефон GSM

- 3. 1 По степени интеграции:- малой степени интеграции

- 4. Требования к логическим элементам 1) Согласованность по

- 5. Логические уровни ТТЛ

- 6. Быстродействие и экономичностьUл = UOH –

- 7. Работа переключения A = Pп tз Задержки распространения сигналов

- 8. Стандарты логических уровней

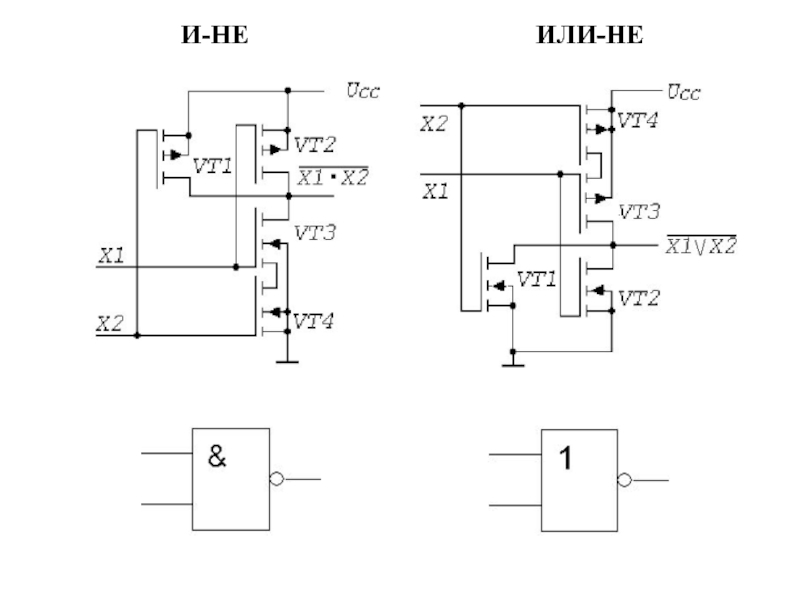

- 9. Элемент ТТЛ(Ш)Транзистор с барьеромШотткиБазовые логические элементы (вентили)

- 10. Элементы КМОП (CMOS) НЕLayout

- 11. И-НЕ

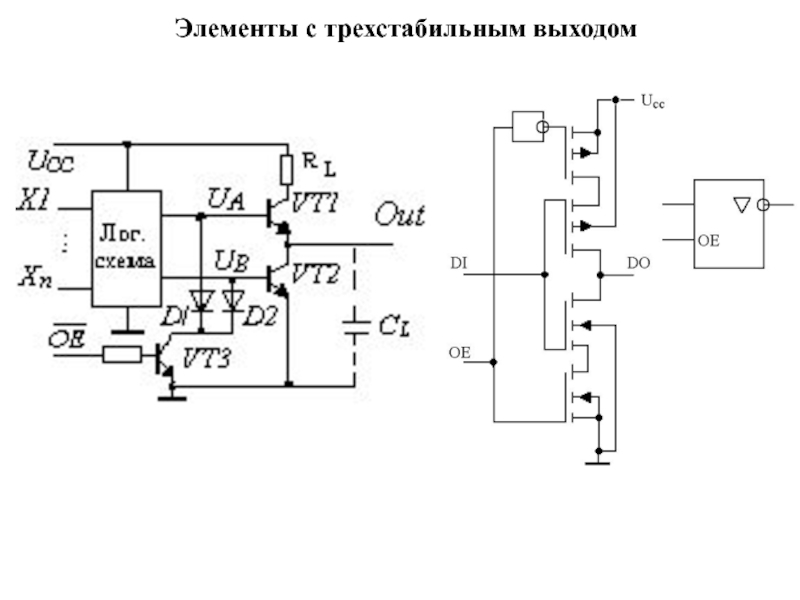

- 12. 1.3 Элементы с открытым выходом

- 13. Применение элементов с открытым выходомМонтажная логикаРабота на длинную линиюУправление СИД

- 14. Элементы с трехстабильным выходом

- 15. Функциональные узлы комбинационного типаПреобразователи кода

- 16. Двоичный дешифратор

- 17. Мультиплексор

- 18. Одноразрядный сумматор

- 19. Многоразрядный сумматор с последовательным переносомtPS = tpc + (n-2)tcc + tcstPC = tpc + (n-1)tcc

- 20. Арифметико-логические устройства (АЛУ)

- 21. Матричный умножительt = 2* tHS + tSM(nA + nB - 4)

- 22. Раздел 4: Цифровые узлы последовательностного типа

- 23. Классификация триггеровПо логике функционирования: D-триггеры; T-триггеры; RS-триггеры; JK-триггеры; комбинированные.1 Функциональные узлы последовательностного типа

- 24. По способу записи информации: асинхронные триггеры; синхронные триггеры: управляемые (синхронизируемые) уровнем; управляемые (синхронизируемые) фронтом; двухступенчатые.

- 25. Асинхронные триггеры

- 26. Триггеры, синхронизируемые уровнем (прозрачные защелки)

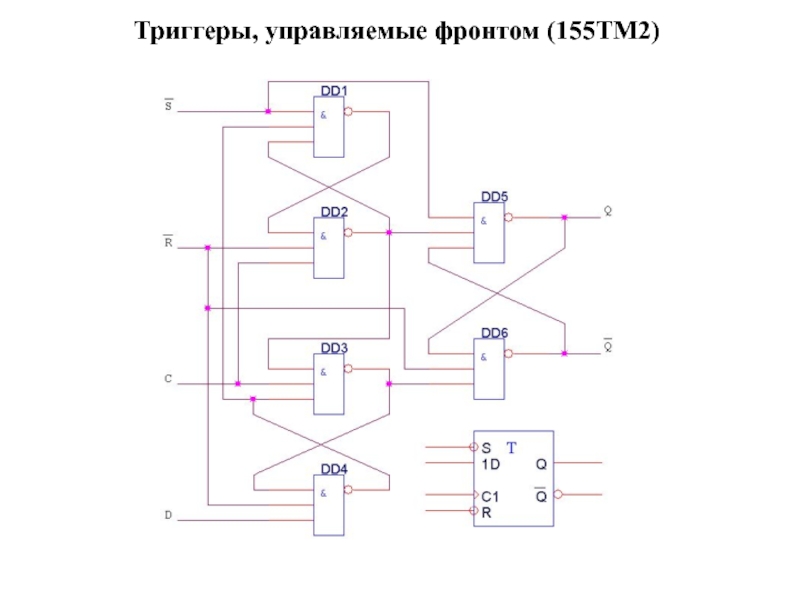

- 27. Триггеры, управляемые фронтом (155ТМ2)

- 28. Параллельные регистры

- 29. Сдвигающие регистры

- 30. Универсальные регистры

- 31. Счетчики – автоматы, фиксирующие число поступивших на

- 32. Двоичные счетчики с последовательным переносомt уст = n * t тг

- 33. Двоичный счетчик с параллельным переносом

- 34. Синхронный счетчик

- 35. Сериализация - десериализация

- 36. 2 Интегральные запоминающие устройства

- 37. ПЗУ - ROM (Read Only Memory)ОЗУ –

- 38. ПЗУМ – ROM(M) - Mask ROMППЗУ –

- 39. Классификация ОЗУ

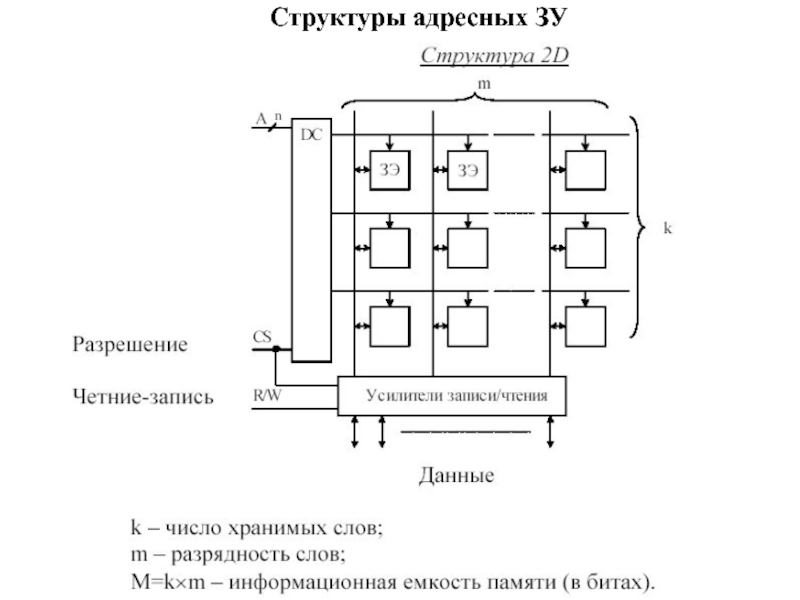

- 40. Структуры адресных ЗУ

- 41. Слайд 41

- 42. Слайд 42

- 43. Структура блочного ЗУ

- 44. Запоминающие элементы ПЗУ Накопитель ROM(M)

- 45. Запоминающие элементы PROMЗапоминающие элементы EPROM и EEPROM

- 46. Программирование ЛИЗМОП

- 47. Транзистор с программируемым порогом

- 48. Запоминающие ячейки Flash

- 49. Внешняя организация EPROM27C12816Kx8

- 50. Чтение EPROM

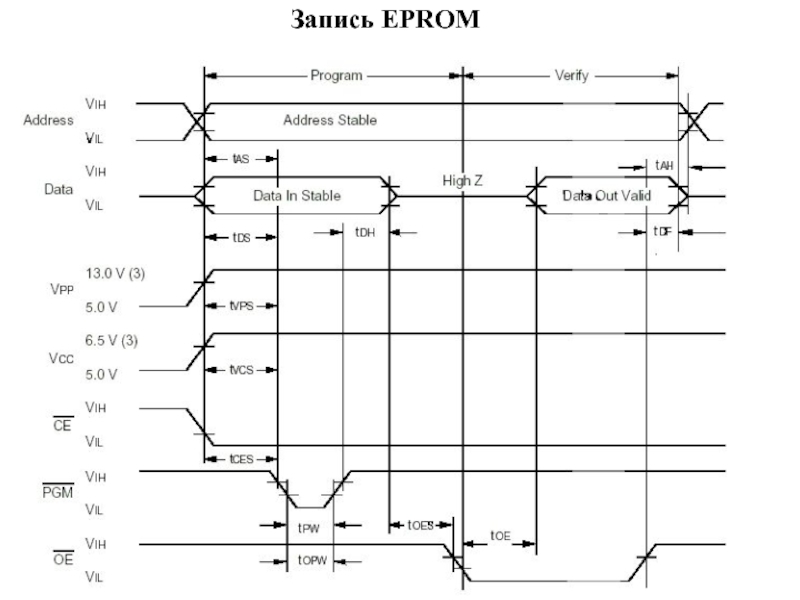

- 51. Запись EPROM

- 52. Внешняя организация EEPROM28С648Кх8

- 53. Структура EEPROM

- 54. Запись EEPROM

- 55. Внешняя организация NAND-Flash

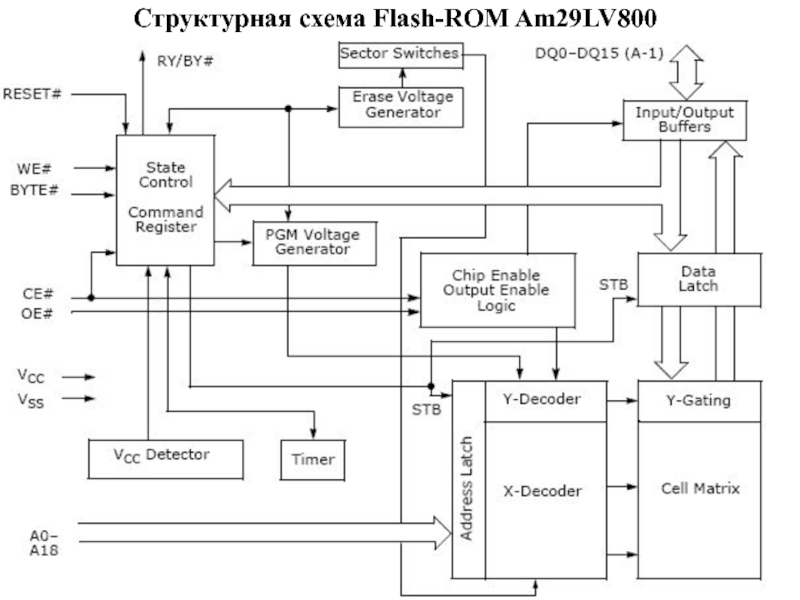

- 56. Структурная схема Flash-ROM Am29LV800

- 57. Режимы работы NAND-FlashRA – адрес ячейки при

- 58. 32-Гбит ИС флэш-памяти NAND-типа (техпроцесс 34-нм)

- 59. Запоминающие элементыКМОПСтатические ЗУ

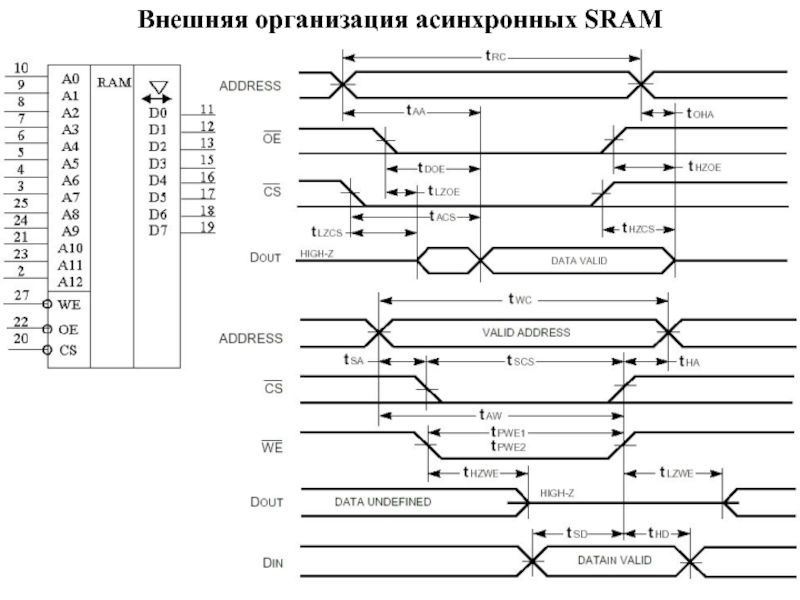

- 60. Внешняя организация асинхронных SRAM

- 61. Динамические ОЗУ

- 62. Внешняя организация асинхронных DRAMАдрес задаетсявнутренним счетчикомCBR (CAS Before RAS)

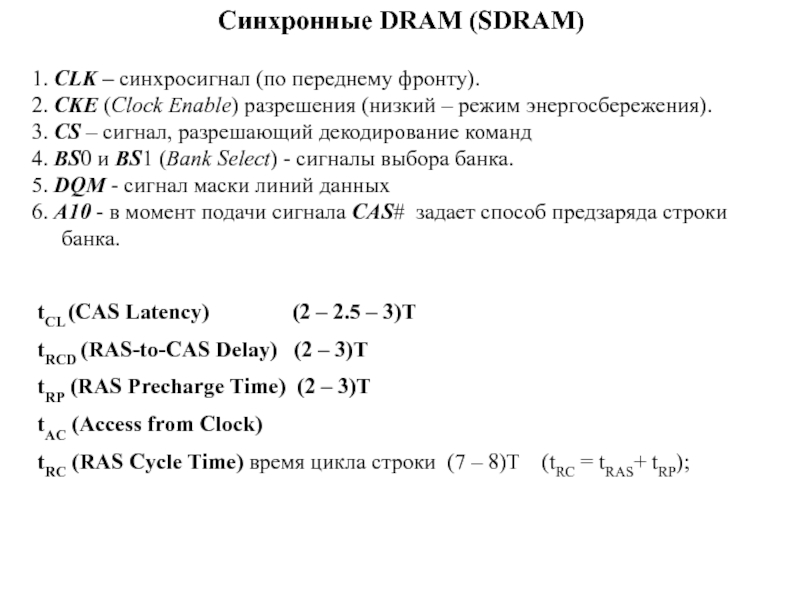

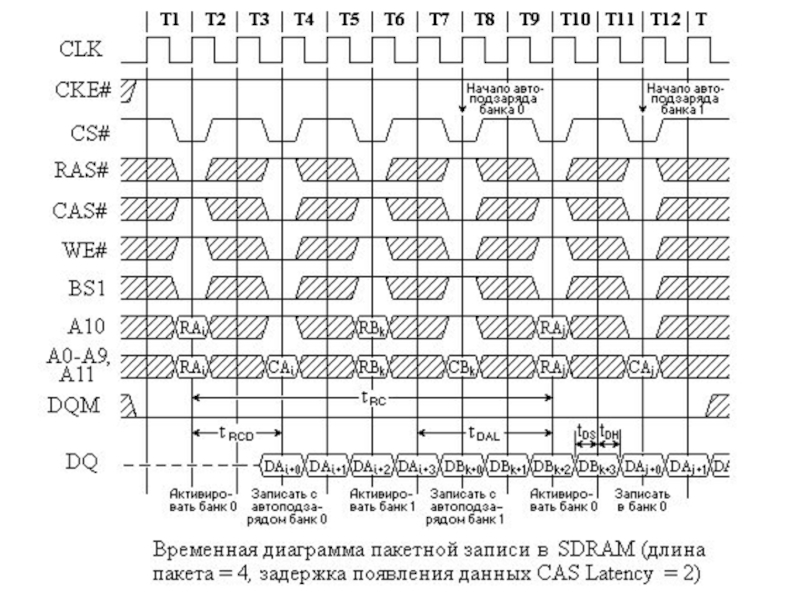

- 63. Синхронные DRAM (SDRAM)1. CLK – синхросигнал (по

- 64. Слайд 64

- 65. Слайд 65

- 66. Регенерация (refresh) SDRAM

- 67. Слайд 67

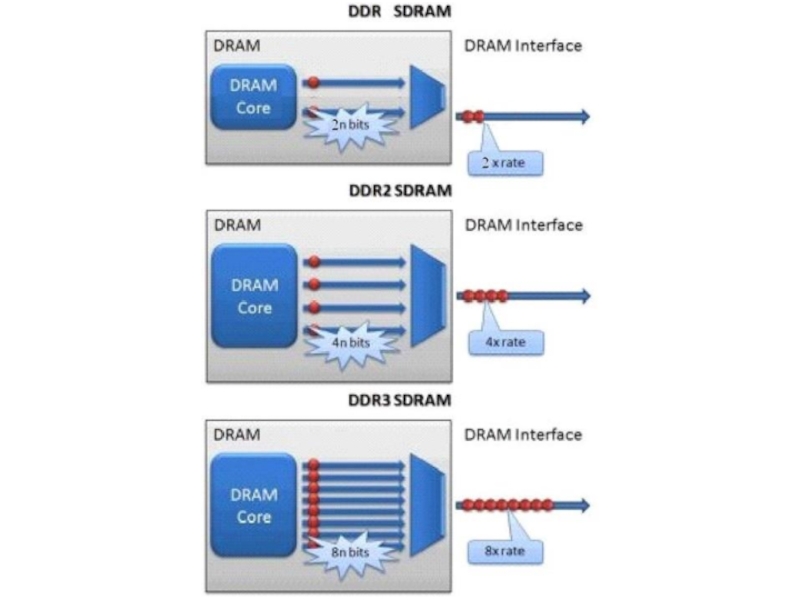

- 68. Структура DDR SDRAM

- 69. Команды DDR SDRAM

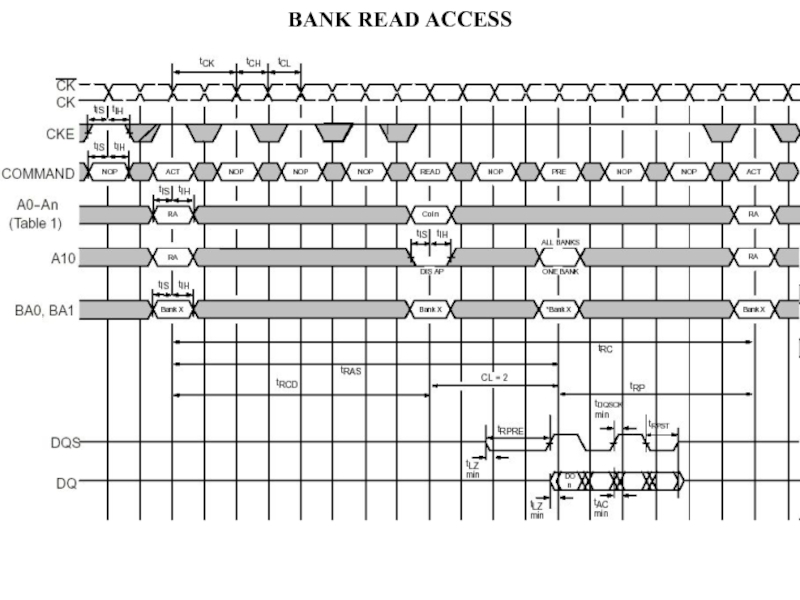

- 70. BANK READ ACCESS

- 71. BANK WRITE ACCESS

- 72. Авторегенерация

- 73. Прямой цифровой синтез сигналов (DDS)

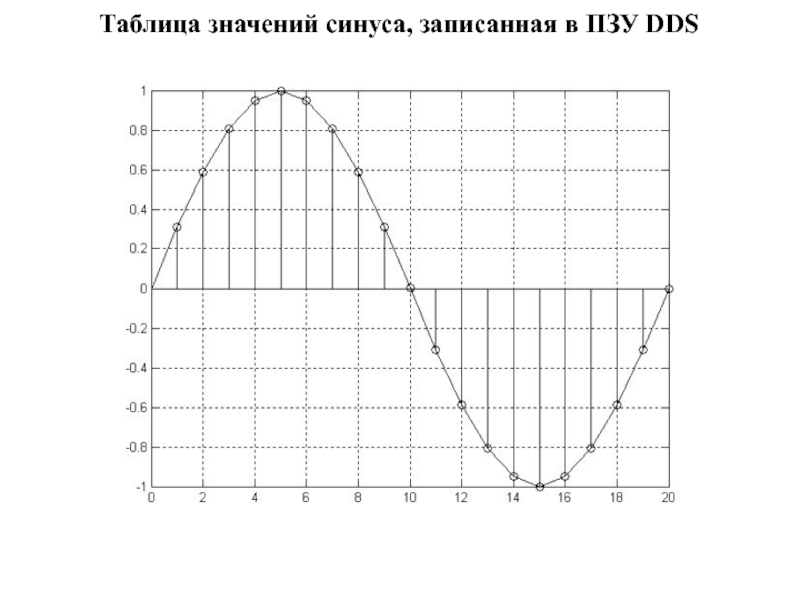

- 74. Таблица значений синуса, записанная в ПЗУ DDS

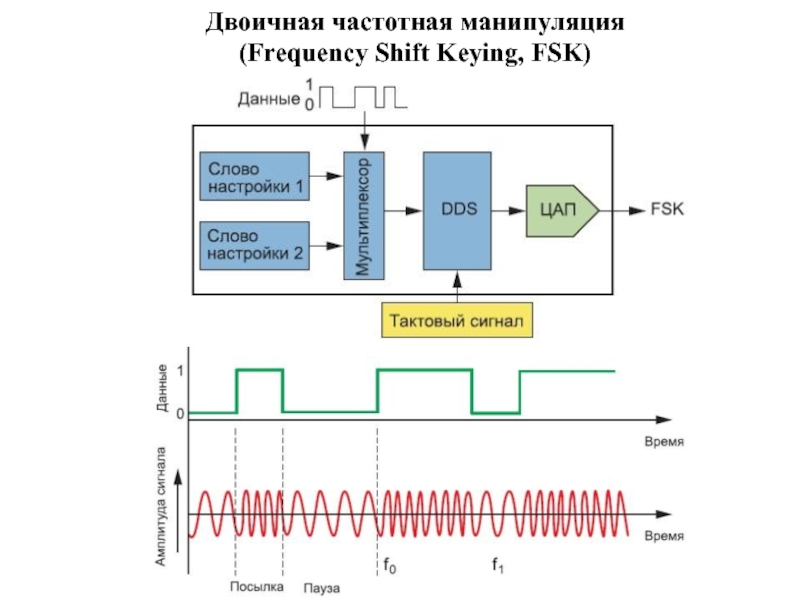

- 75. Двоичная частотная манипуляция (Frequency Shift Keying, FSK)

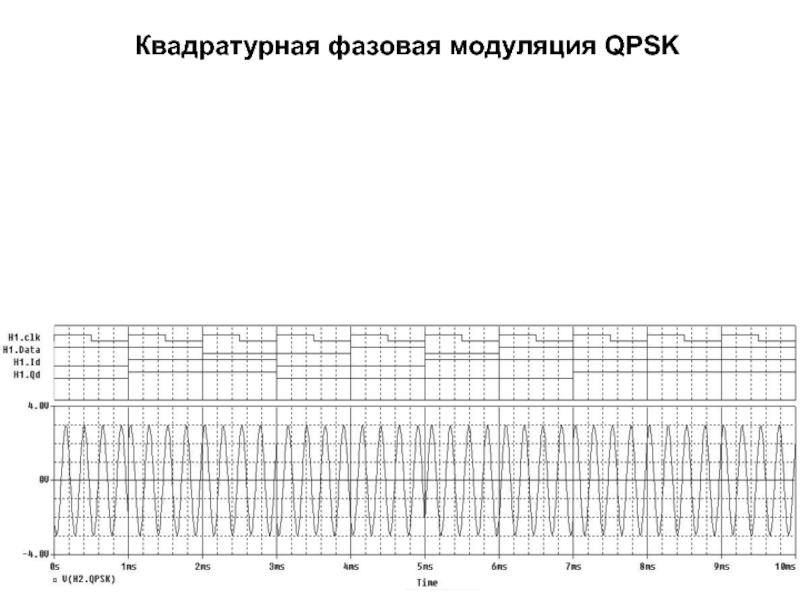

- 76. Квадратурная фазовая модуляция QPSK

- 77. Сплиттер Модулятор

- 78. Скачать презентанцию

Слайды и текст этой презентации

Слайд 1Раздел 3: Элементы и комбинационные узлы цифровых устройств. Лекция 4. Вопросы: 1 Элементная

база цифровых устройств.

2 Функциональные узлы комбинационного типа.

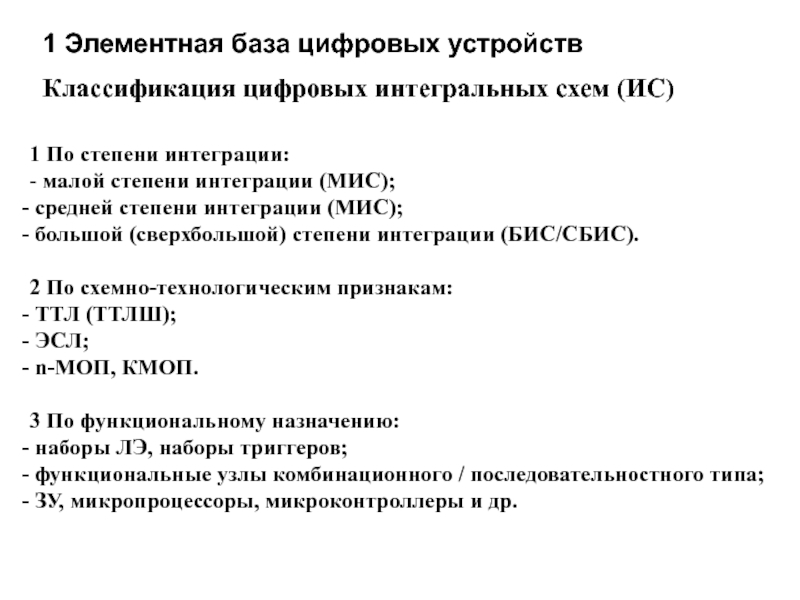

Слайд 31 По степени интеграции:

- малой степени интеграции (МИС);

средней степени

интеграции (МИC);

большой (сверхбольшой) степени интеграции (БИС/СБИС).

2 По схемно-технологическим признакам:

ТТЛ (ТТЛШ);ЭСЛ;

n-МОП, КМОП.

3 По функциональному назначению:

наборы ЛЭ, наборы триггеров;

функциональные узлы комбинационного / последовательностного типа;

ЗУ, микропроцессоры, микроконтроллеры и др.

1 Элементная база цифровых устройств

Классификация цифровых интегральных схем (ИС)

Слайд 4Требования к логическим элементам

1) Согласованность по логическим уровням

Положительная логика:

UH - 1 UL – 0;

Отрицательная логика: UH -

0 UL – 1;Слайд 13Применение элементов с открытым выходом

Монтажная логика

Работа на длинную линию

Управление СИД

Слайд 19Многоразрядный сумматор с последовательным переносом

tPS = tpc + (n-2)tcc +

tcs

tPC = tpc + (n-1)tcc

Слайд 20Арифметико-логические устройства (АЛУ)

Входы

Выходы

Операция M

FSel1 FSel0 F[3..0]Clear 0 0 0 L

Q - P 0 0 1 Q - P - CI

P - Q 0 1 0 P - Q - CI

P + Q 0 1 1 P + Q + CI

P $ Q 1 0 0 P $ Q

P # Q 1 0 1 P # Q

P & Q 1 1 0 P & Q

Preset 1 1 1 H

Слайд 22Раздел 4: Цифровые узлы последовательностного типа Лекция 5. Вопросы: 1 Функциональные узлы последовательностного

типа.

2 Интегральные запоминающие устройства

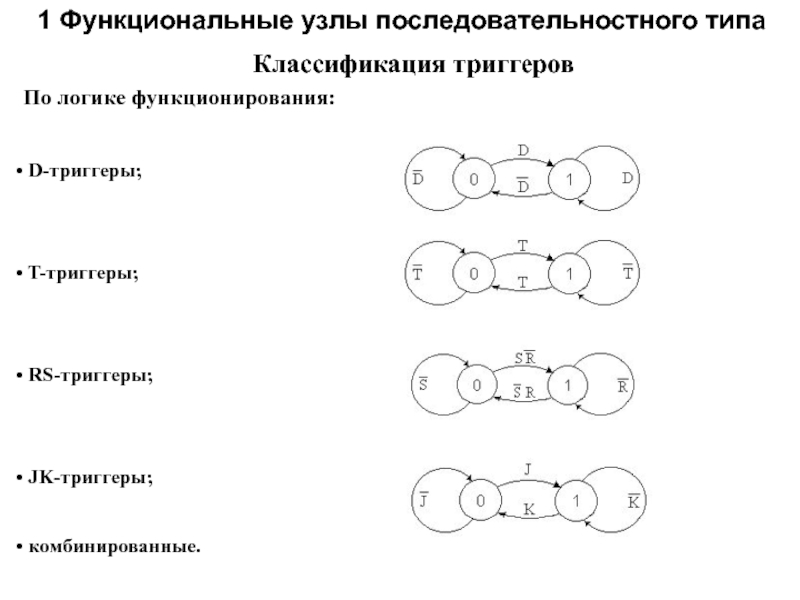

Слайд 23Классификация триггеров

По логике функционирования:

D-триггеры;

T-триггеры;

RS-триггеры;

JK-триггеры;

комбинированные.

1 Функциональные

узлы последовательностного типа

Слайд 24По способу записи информации:

асинхронные триггеры;

синхронные триггеры:

управляемые (синхронизируемые)

уровнем;

управляемые (синхронизируемые) фронтом;

двухступенчатые.

Слайд 31Счетчики – автоматы, фиксирующие число поступивших на их вход импульсов

в том или ином коде

Модуль счета М –число возможных состояний

счетчикаКлассификация

По способу кодирования: - двоичные (М=2n);

- двоично-кодированные.

По направлению счета: - суммирующие;

- вычитающие;

- реверсивные.

По принадлежности к классам автоматов – синхронные;

- асинхронные.

Счетчики

Возможные режимы работы:

- регистрация числа событий;

- деление частоты.

Слайд 37ПЗУ - ROM (Read Only Memory)

ОЗУ – RAM (Random Access

Memory)

FIFO (First In – First Out)

LIFO (Last In – First

Out)Классификация полупроводниковых ЗУ

Слайд 38ПЗУМ – ROM(M) - Mask ROM

ППЗУ – PROM (Programmable ROM)

РПЗУ-УФ

– EPROM (Erasable Programmable ROM)

EPROM – OTP (One Time Programmable

ROM) РПЗУ-ЭС –EEPROM (Electrically Erasable Programmable ROM)

Классификация ПЗУ

Слайд 57Режимы работы NAND-Flash

RA – адрес ячейки при чтении;

RD – считываемые

данные;

PA – адрес ячейки при программировании (записи);

PD – записываемые данные;

SA

– адрес стираемого сектора.Слайд 63Синхронные DRAM (SDRAM)

1. CLK – синхросигнал (по переднему фронту).

2.

CKE (Clock Enable) разрешения (низкий – режим энергосбережения).

3. CS

– сигнал, разрешающий декодирование команд 4. BS0 и BS1 (Bank Select) - сигналы выбора банка.

5. DQM - сигнал маски линий данных

6. A10 - в момент подачи сигнала CAS# задает способ предзаряда строки банка.

tCL (CAS Latency) (2 – 2.5 – 3)T

tRCD (RAS-to-CAS Delay) (2 – 3)T

tRP (RAS Precharge Time) (2 – 3)T

tAC (Access from Clock)

tRC (RAS Cycle Time) время цикла строки (7 – 8)T (tRC = tRAS+ tRP);