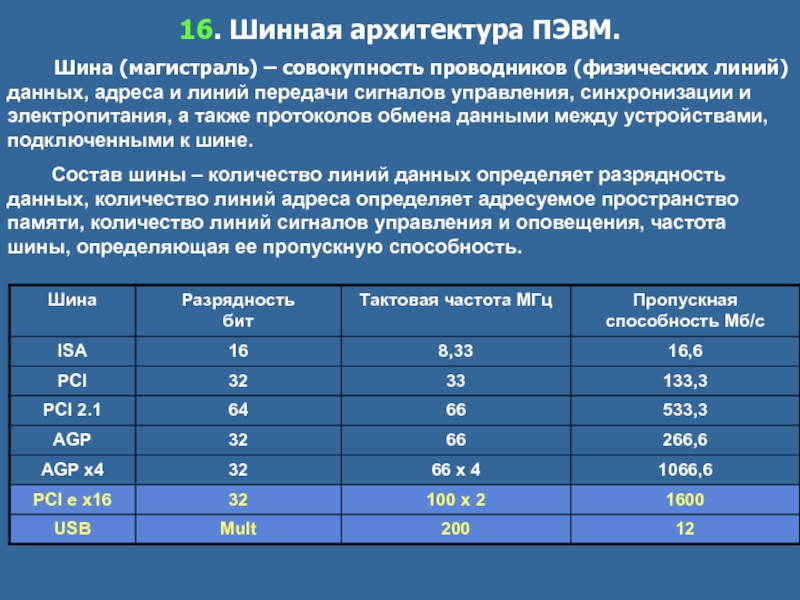

16. Шинная архитектура ПЭВМ.

Шина (магистраль)

– совокупность проводников (физических линий) данных, адреса и линий передачи сигналов управления, синхронизации и электропитания, а также протоколов обмена данными между устройствами, подключенными к шине.

Состав шины – количество линий данных определяет разрядность данных, количество линий адреса определяет адресуемое пространство памяти, количество линий сигналов управления и оповещения, частота шины, определяющая ее пропускную способность.

Слайд 2 Схема формирования шинного интерфейса для внешних

устройств.

Любое внешнее устройство, предназначенное для

установки в разъёмы расширений шины должно содержать, как минимум, 2 регистра: регистр данных (буфер данных) и регистр признаков (сигналов запроса-готовности), который связан с линией передачи сигналов.

Внешние устройства работают обычно существенно медленнее центрального процессора, т.е. асинхронно по отношению к нему, поэтому имеют в своем составе собственный генератор синхронизации.

Готовность к приёму/передачи данных должна подтверждаться соответствующими сигналами готовности. ЦП или вспомогательные схемы контроллера шины производят циклический опрос регистров состояния внешних устройств и, при приеме сигнала готовности, обеспечивают подключение к шине через дешифратор номера этого устройства.

шина данных

дешифратор

CPU

D

OU 1

D

OU 2

D

D

OU 3

OU 4

Пояснения к шинной архитектуре ПЭВМ

Контроллер шины является устройством, связывающим центральный процессор с периферийными устройствами по сигналу запроса и сигналу готовности внешнего устройства к обмену данными с центральным процессором. При этом управление шиной передается этому внешнему устройству через дешифратор номера и это устройство становится задатчиком шины.

Задатчиками (хозяевами) шины могут выступать центральный процессор (обычная ситуация), контроллер ПДП, контроллер регенерации и некоторые платы системы расширения.

В каждом цикле обмена задатчиком всегда является только одно устройство. Контроллер ПДП захватывает магистраль (запрещает работу центрального процессора с шиной данных) на время прямой передачи информации между устройством ввода/вывода и памятью (по запросу устройства ввода/вывода).

Контроллер регенерации периодически становится задатчиком магистрали для проведения циклов регенерации системной динамической памяти через заданные интервалы времени.

Для 32-разрядных компьютеров (386DX, 486, Pentium и т.д.) обмен процессора с памятью (а иногда и с другими устройствами) осуществляется через быстродействующую локальную шину VLB или через РСI.

Слайд 4 Протокол передачи данных по заданному адресу памяти

Слайд 5

УУ

Буферизация и изменение формата данных.

Назначение

буферного регистра:

1. Временное хранение данных

для согласования скоростей устройств.

2. Подключение устройства к шине.

3. Изменение формата данных.

Схема мостового контроллера.

MUX CPU

32

D

D

16

36

Слайд 6 Схема наследуемой шинной архитектуры на базе шины ISA

ЦП

ОЗУ

Контроллер

клавиатуры

клавиатура

Контроллер ISA

LPT1

Контроллер LPT

LPT2

COM1

Контроллер COM

COM2

CD ROM

Контроллер IDE

HDD1

HDD2

HDD3

FDD1

Контроллер FDD

FDD2

Звуковой адаптер

Видео адаптер

SCSI адаптер

Адаптер внешних устройств

SCSI 1

SCSI 1

SCSI 1

SCSI 1

SCSI 1

SCSI 1

ВУ SCSI 7

Внешнее устройство

Адаптер внешних устройств

Внешнее устройство

Схема наследуемой

шинной архитектурой

Слайд 8Внешний вид системной платы с наследуемой шинной архитектурой

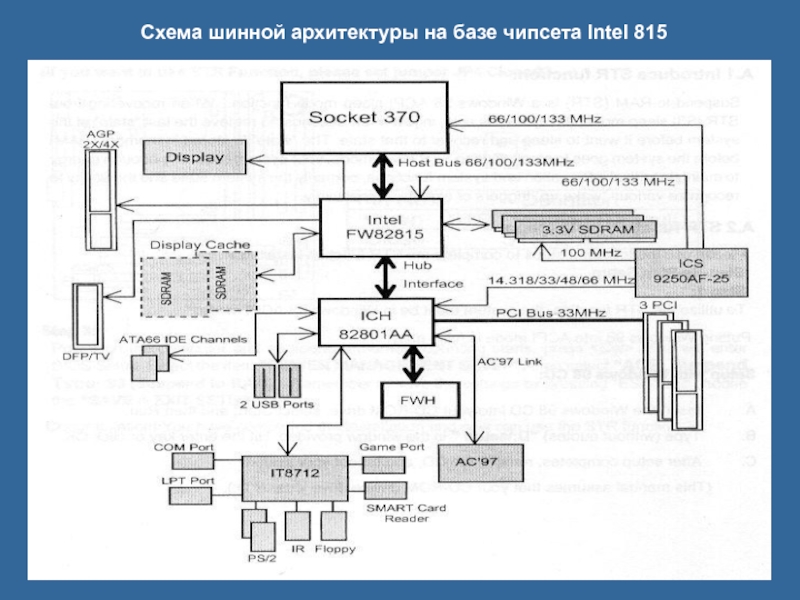

Схема шинной архитектуры на базе чипсета Intel 815

Слайд 10Внешний вид системной платы с шинной архитектуры Intel 815

Слайд 11Схема шинной архитектуры на базе чипсета Intel 865

Слайд 12Схема шинной архитектуры на базе чипсета Intel 945

Слайд 13Внешний вид системной платы ASUS P7P55D DELUXE

с шинной архитектурой на базе чипсета Intel P55 Express

Слайд 14

Технические характеристики системной платы ASUS P7P55D DELUXE

с шинной архитектурой на базе чипсета Intel P55 Express

Поддерживаемые процессоры: INTEL CORE i5

Разъем: LGA1156

Чипсет: INTEL P55 EXPRESS

Память: 4 х DIMM. 16 ГБАЙТ max, DDRIII - 2133/1600/1333/1066

Слоты локальной шины : - З х PCI EXPRESS X16.

- 2 х PCI EXPRESS X1.

- 2 х PCI

Интерфейсы накопителей: - 9 х SATA,

- I х IDE UDMA.

Порты USB: - 6 на задней панели,

- 8 дополнительно на системной плате

Сетевой адаптер: контроллер REALTEK 8112L/8110SC 1 GB/c

Звуковой адаптер: 10-канальный HDA-кодек VIA VT2020

Форм-фактор: АТХ.

Размеры: 305 х 244 мм.

Слайд 15

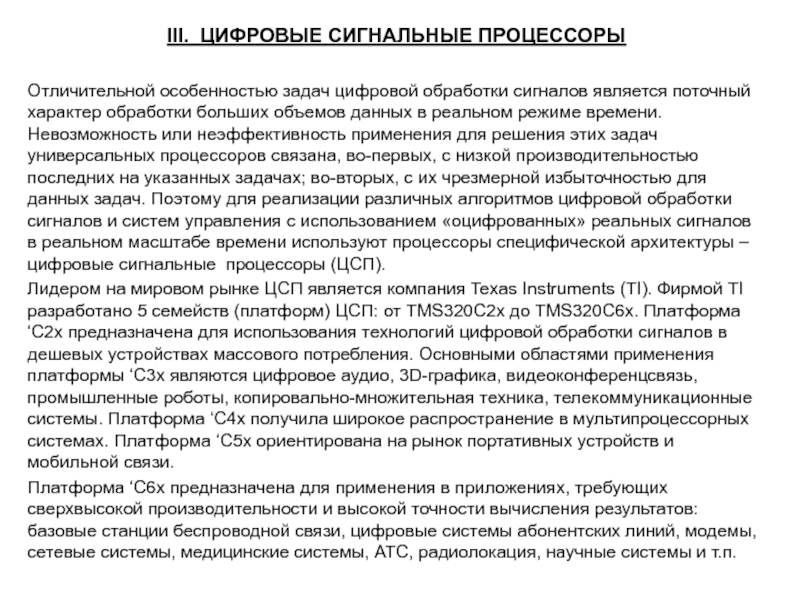

Характеристика локальной шины PCI

(Peripheral component interconnect — взаимосвязь периферийных компонентов

)

частота шины — 33,33 или 66,66 МГц, передача адреса и

данных синхронная;

разрядность шины — 32 или 64 бита, шина мультиплексированная (адрес и данные передаются по одним и тем же линиям);

пропускная способность для 32-разряднй шины на частоте 33,33 МГц — 133 Мбайт/с;

адресное пространство памяти — 32 бита (4 байта);

адресное пространство портов ввода-вывода — 32 бита (4 байта);

конфигурационное адресное пространство (для одной функции) 256 байт;

напряжение 3,3 или 5 В.

Стандартные модификации шины PCI

PCI 2.0 — первая версия базового стандарта, получившая широкое распространение, Пиковая пропускная способность — 133 Мбайт/с; напряжение – 5 в.

PCI 2.1-3.0 — отличались от 2.0 возможностью одновременной работы нескольких bus-master устройств (т. н. конкурентный режим), а также появлением универсальных карт расширения, способных работать как в 5 В, так и в 3,3 В слотах (с частотой 33 и 66 МГц соответственно).

Версия 2.1 — работа с 3,3 В картами и наличие соответствующих линий питания

Версия 2.2 —карты расширения имеют универсальный разъём и способны работать практически во всех более поздних разновидностях слотов шины PCI, а также, в некоторых случаях, и в слотах 2.1;

Версия 2.3 — несовместима с картами PCI 5 В, несмотря на продолжающееся использование 32-битных слотов с 5 В-ключом. Карты расширения имеют универсальный разъём, но не способны работать в 5 В-слотах ранних версий (до 2.1 включительно);

Версия 3.0 — завершает переход на карты PCI 3,3 В, карты PCI 5 В больше не поддерживаются.

Слайд 16

PCI 64 — расширение базового стандарта PCI,

появившееся в версии 2.1, удваивающее число линий данных, и, следовательно,

пропускную способность. Слот PCI64 является удлинённой версией обычного PCI-слота. Формально совместимость 32-битных карт с 64-битным слотами (при условии наличия общего поддерживаемого сигнального напряжения) полная, а совместимость 64-битной карты с 32-битным слотами является ограниченной (в любом случае произойдёт потеря производительности).

Работает на тактовой частоте 33 МГц. Пиковая пропускная способность — 266 Мбайт/с;

PCI 66 — это PCI 64 работающий на тактовой частоте 66 МГц, использует 3,3 В-слоты, карты имеют универсальный, либо 3,3 В форм-фактор. Пиковая пропускная способность — 533 Мбайт/с;

PCI 64/66 — комбинация PCI 64 и PCI 66, позволяет учетверить скорость передачи данных по сравнению с базовым стандартом PCI, и использует 64-битные 3,3 В-слоты, совместимые только с универсальными и 3,3 В 32-битными картами расширения.

Пиковая пропускная способность — 533 Мбайт/с;

PCI-X — расширение PCI64, для всех вариантов шины существуют следующие ограничения по количеству подключаемых к каждой шине устройств: 66 МГц — 4, 100 МГц — 2, 133 МГц — 1 (или 2, если одно или оба устройства не находятся на платах расширения, а уже интегрированы на одну плату вместе с контроллером), 266, 533 МГц и выше — 1;

Версия 1.0 — введено две новые рабочие частоты: 100 и 133 МГц, а также механизм раздельных транзакций для улучшения производительности при одновременной работе нескольких устройств.

Пиковая пропускная способность — 1024 Мбайт/с;

Версия 2.0 — введено две новые рабочие частоты: 266 и 533 МГц, а также коррекция ошибок чётности при передаче данных (ECC). Расширяет конфигурационное пространство PCI до 4096 байт и допускает расщепление на 4 независимых 16-битных шины, что применяется исключительно во встраиваемых и промышленных системах

Пиковая пропускная способность — 4096 Мбайт/с;

Слайд 17

Mini PCI — новый форм-фактор PCI 2.2

для использования в основном в ноутбуках;

Cardbus —

PCMCIA форм-фактор для 32-бит, 33 МГц PCI;

CompactPCI — использует модули размера Eurocard, включаемые в PCI backplane;

PC/104-Plus — индустриальная шина, использующая сигнализацию PCI с другим разъёмом;

PMC — PCI mezzanine card - мезонинная шина, соответствует стандарту IEEE P1386.1;

ATCA или AdvancedTCA — шина следующего поколения для телекоммуникационной индустрии.

PCI Express (3GI0/Arapaho) — новый последовательный интерфейс, использующий программную модель PCI, однако обладающий более производительным многоуровневым механизмом передачи данных.

PCI Express 2 - скорость передачи увеличена в 2 раза и более.

Слайд 18Счетчик 2

17. Системный интервальный

таймер ПЭВМ.

Служит для задания временных

интервалов и формирования сигналов с различными временными параметрами в ПЭВМ применяется программи-руемый таймер i8254

В состав таймера входят: буфер шины данных, схема управления вводом-выводом и три независимых канала, каждый из которых содержит регистр режима, схему управления каналом, буфер и 16-разрядный счетчик.

Буфер обмена

Устройство управления

А0 А1

D0 … D7

Регистр управляющего слова порт 43h

Счетчик 0

Gate 0

Out 0

Счетчик 1

Gate 1

Out 1

Регистр защелка

Регистр счетчик n--

Регистр ввода-вывода порт 42h

Gate 2

Out 2

CLK от часов CMOS

внутренняя шина данных

RD WR

Слайд 19 Режим 0 Прерывание терминального счета.

После записи управляющего слова в регистр режима канала на

выходе ОUT устанавливается напряжение низкого уровня. Загрузка счетчика не изменяет это состояние. Затем начинается работа счетчика (декремент).

В момент, когда счетчик обнулится, на выходе OUT устанавливается напряжение высокого уровня и сохраняется до загрузки счетчика новым значением.

Счет возможен только при сигнале высокого уровня на входе GATE. Низкий уровень этого сигнала или ниспадающий фронт запрещают счет.

Перезагрузка счетчика во время счета приводит к остановке счета младшим байтом, загрузка старшего байта запускает новый цикл счета.

Минимально допустимое значение счетчика n равно 2.

Слайд 20

Режим 1 Ждущий мультивибратор.

На выходе OUT формируется отрицательный импульс длительностью

t = n ●T, где n - число, загруженное в счетчик, T- период тактовых импульсов.

Низкий уровень на выходе OUT устанавливается со следующего такта после подачи на вход GATE сигнала высокого уровня.

Загрузка в счетчик нового числа не влияет на длительность текущего импульса, но учитывается при следующем запуске счетчика.

Перезапуск счетчика производится нарастающим фронтом сигнала на входе GATE (без перезагрузки счетчика).

Минимально допустимое значение счетчика n равно 1.

Слайд 21

Режим 2 Генератор частоты (периодический).

Каждый раз после достижения счетчиком нуля на выходе

OUT появляется отрицательный импульс с длительностью один такт.

Перезагрузка значения n счетчика вступает в силу только после перезапуска счетчика.

При исчезновении сигнала высокого уровня на входе GATE прекращается счет и на выход OUT подается напряжение высокого уровня.

Перезапуск счетчика происходит при наличии на входе GATE сигнала высокого уровня.

Минимально допустимое значение счетчика n равно 4.

Слайд 22

Режим 3 Генератор меандра (периодический).

Аналогичен режиму 2, но выходной сигнал имеет форму

меандра, т.е. прямоугольной формы, где положительный уровень выходного сигнала занимает первый полупериод, а отрицательный - второй полупериод.

Если n (начальное значение счетчика) четно, то длительность положительного и отрицательного полупериодов равна t1,2 = n ●T/2, а если n нечетно - то t1 = (n+1) ● T/2 и t2 = (n-1) ● Т/2 соответственно.

Низкий уровень сигнала на входе GATE запрещает счет, на выходе OUT устанавливается сигнал высокого уровня.

Высокий уровень GATE разрешает счет, а нарастание его запускает счетчик начального состояния. Значение счетчика n не менее 4.

Слайд 23

Режим 4 Счетчик событий.

По окончании отсчета числа, загруженного в счетчик, на

выходе OUT формируется отрицательный импульс длительностью один такт.

Запись в счетчик во время счета младшего байта не влияет на текущий счет, а запись старшего байта перезапускает счетчик.

Низкий уровень входа GATE запрещает счет, высокий - разрешает.

Минимально допустимое значение счетчика n равно 1.

Слайд 24

Режим 5 Счетчик событий с

автозагрузкой.

Отличие от режима 4 состоит в

том, что каждое нарастание сигнала на входе GATE перезапускает счетчик.

Перезагрузка счетчика не влияет на текущий цикл, однако следующий цикл определяется вновь занесенным числом n.

Минимально допустимое значение счетчика n равно 1.

каналы таймера имеют следующее назначение:

Канал 0

- системные часы (IRQ0), режим 3, счетчик n=0 (65536)

Тактовая частота каждого канала равна 1,193181 МГц, т.е. каждый такт имеет длительность 0,84 мксек.

Вход GATE канала 0 всегда имеет высокий уровень, поэтому счет на этом канале разрешен всегда.

При начальной загрузке BIOS инициализирует этот канал для работы в режиме 3 со счетчиком 0 (т.е. 65536 декрементов на цикл счета).

Поэтому частота системных часов равна 1193181 / 65536 = 18.2 Гц, а сигнал на выходе канала 0 – Out 0, воспринимаемый контроллером прерываний, как сигнал прерывания IRQ0, инициирует вектор прерывания Int8 18,2 раз в секунду (т.е. каждые 55 мсек).

Системные часы CMOS

i8254

Канал 0 n=65535

i8259

Вызывает Int8

ROM BIOS

Выполняет Int8

Область данных BIOS 0040:006С

4-х байтовый счетчик увеличивает свое значение

Out0

IRQ0

clk

1 - Регенерация памяти, режим 2, значение счетчика n =

18.

Вход GATE канала 1 также, как и канала 0 всегда имеет высокий уровень, поэтому счет на этом канале также разрешен всегда.

Выход счетчика связан со входом DRQ0 контроллера прямого доступа к памяти на захват канала 0 в режиме блочного приема-передачи данных из памяти в память.

Сигнал DRQ0 имеет приоритет над другими запросами прямого доступа к памяти.

Сигнал GATE представляет собой подтверждение контроллера прямого доступа к памяти на захват канала 0 – DACK0

Канал 1 работает в режиме 2 со счетчиком 18, поэтому регенерация памяти происходит каждые 18 мксек или 66288 раз в секунду.

Перепрограммировать счетчик канала 1 не рекомендуется, т.к. это приведет к потере данных в ОЗУ и зависанию ПЭВМ.

Слайд 27

Генератор часов РВ

Регистр сч.0

Счетчик 0

Регистр

сч.1

Счетчик 1

Регистр сч.2

Счетчик 2

Gate 0=1

Gate 1=1

Gate 2=1

Порт 61h

Порт 62h

Порт 43h

i8255

i8254

часы

BIOS

регенерация памяти

Канал 2 - генератор звука системного динамика или другое назначение пользователя (например, генерация псевдослучайных чисел), режим 3, значение счетчика n задается пользователем при программировании.

При генерации звука значение счетчика n канала 2 вычисляется по формуле n = 1193181 / f, где f - требуемая частота звука в герцах.

Слайд 28 Системный таймер имеет следующие программно доступные регистры:

Адрес порта Операция

Назначение

0040h запись Загрузка счетчика канала 0

чтение Чтение счетчика канала 0

0041h запись Загрузка счетчика канала 1

чтение Чтение счетчика канала 1

0042h запись Загрузка счетчика канала 2

чтение Чтение счетчика канала 2

0043h запись Запись управляющего слова

в регистр режима канала

Программирование канала осуществляется путем ввода управляющих слов в регистр режима каналов и начального значения в его счетчики.

Назначение битов управляющего слова показано на следующем экране.

Существует два способа чтения текущего значения счетчика канала.

1. Чтение с остановом счетчика. Для обеспечения стабильных показаний необходимо приостановить работу канала либо подачей сигнала низкого уровня на вход GATE (кроме режима 1), либо блокированием тактовых импульсов.

2. Чтение "на лету". Для считывания счетчика без остановки процесса счета используется посылка в порт 43h управляющего слова в режиме "защелкивания". Это управляющее слово фиксирует текущее значение

счетчика в буфере, а затем считывается младший байт, потом старший.

Слайд 29 Управляющее слово имеет следующий формат:

- в порт 43h

бит 0 – режим кодирования значения n

0 - двоичный код,

1 - двоично-десятичный код

биты 1-3 - режим работы канала:

000 - режим 0

001 - режим 1

X10 - режим 2

X11 - режим 3

100 - режим 4

101 - режим 5

биты 4-5 - вид загрузки и чтения счетчика:

00 - "защелкивание" (биты 0-3 безразличны)

01 - только младший байт

10 - только старший байт

11 - младший байт, затем старший

биты 6-7 - номер канала:

00 - канал 0

01 - канал 1

10 - канал 2

11 – запрещенная комбинация

Слайд 30 18. Часы реального времени ПЭВМ, память

CMOS.

Часы реального времени и память CMOS

- самостоятельное энергонеза-висимое устройство на системной плате ПЭВМ - МС 146818 (ф. «Motorola»).

00h 01h 02h 03h 04h 05h 06h 07h 08h 09h 0Ah 0Bh 0Ch 0Dh

124 регистра CMOS

IRQ8

Буферный регистр порт 71h

Устройство управления

D0 … D7

внутренняя шина данных

CLK

. . . . . . . . . . . . . 7Fh

Индексный регистр порт 70h

- +

1,5 .. 5 V

Генератор часов РВ f = 1,193181 МГц

Счетчик

Слайд 31 Содержание основных регистров часов реального времени

в CMOS

00h секунды

01h секундная тренога (будильник)

02h минуты

03h минутная тренога (будильник)

04h часы

05h часовая тревога (будильник)

06h день недели

07h день месяца

08h месяц

09h год

0Ah регистр статуса часов реального времени

0Bh регистр статуса часов реального времени

0Ch регистр статуса выполнения прерывания IRQ8

0Dh регистр статуса состояния батарейки и памяти

0Ah бит 7=1 идет модификация времени (надо ждать значения 0,

чтобы читать)

0Вh бит 6=1 разрешено периодическое прерывание

бит 5=1 разрешено прерывание треноги

бит 4=1 разрешено прерывание конца модификации

бит 1=1 часы считаются до 24,

=0 часы считаются до 12.

бит 0=1 разрешено запоминание времени суток

Содержание регистров SETUP

в CMOS

0Eh состояние констант POST после загрузки BIOS

0Fh состояние констант POST после выключения ПЭВМ

10h типы дисководов для гибких дисков

11h резерв

12h типы жестких дисков

13h резерв

14h константы SETUP

15h .. 16h размер основной памяти в килобайтах

17h .. 18h размер дополнительной памяти в килобайтах

19h константы первого жесткого диска

1Ah константы второго жесткого диска

1Bh .. 2Dh резерв

2Eh .. 2Fh контрольная сумма регистров CMOS

30h .. 31h расширение размера дополнительной памяти

32h значение века в формате BCD

33h свойства размера памяти ( < 1 Мб или > 1 Мб )

34h .. 3Fh другие константы SETUP и BIOS

40h .. 7Fh недокументированный резерв различных

производителей системных плат и BIOS

Слайд 33 Особенности использования аппаратного прерывания IRQ8

Часы реального времени вызывают аппаратное (радиальное) прерывание IRQ8

и соответствующее векторное прерывание 70h.

Программа пользователя может установить вектор этого прерывания на любую процедуру, которую требуется выполнить в определенное время.

Для этого разработано векторное прерывание 1Аh.

Прерывание IRQ8 может появляться по одной из трех причин:

1. Периодическое прерывание происходит через определенные интервалы времени обновления счетчика часов реального времени.

Их периодичность приближенно равна одной миллисекунде.

2. Прерывание тревоги происходит, когда значение трех регистров тревоги совпадает со значениями соответствующих временных регистров.

Тревога устанавливается как смещение относительно текущего момента времени.

Максимальная величина смещения установки тревоги равна 23:59:59.

Вектор прерывания 4АН может указывать на пользовательскую процедуру обработки тревоги.

3. Прерывание конца модификации происходит после каждого обновления значений регистров часов РВ CMOS – 04h.

Примечание: номер причины вызова прерывания указывается в регистре 0Ch. бит 6=1 – периодическое,

бит 5=1 – прерывание тревоги,

бит 4=1 – обновление часов.

Особенности использования прерывания 1Ah.

Функции 0 и

1 прерывания 1АН читают и устанавливают счетчик времени суток.

Функция 2: Чтение времени из часов реального времени AH = 02h.

При возврате: CH = часы в BCD

CL = минуты в BCD

DH = секунды в BCD

Функция 3: Установка времени часов реального времени AH = 03h.

При входе: CH = часы в BCD

CL = минуты в BCD

DH = секунды в BCD

DL = 1 - переход на летнее время, иначе – 0.

Функция 4: Чтение даты из часов реального времени AH = 04h.

При возврате: CH = век в BCD (19 или 20)

CL = год в BCD (с 1980)

DH = месяц в BCD

DL = день месяца в BCD

Функция 5: Установка даты часов реального времени AH = 05h.

При входе: CH = век в BCD (19 или 20)

CL = год в BCD (с 1980)

DH = месяц в BCD

DL = день месяца в BCD

Функция 6: Установка тревоги для часов реального времени AH = 06h.

При входе: CH = часы смещения в BCD

CL = минуты смещения в BCD

DH = секунды смещения в BCD

Функция 7: Сброс тревоги AH = 07h

Особенности использования формата BCD.

Поскольку

показания часов реального времени никогда не состоят более чем из двух десятичных цифр, значения времени очень удобно выдавать в двоично-кодированной десятичной форме (BCD), т.е. когда байт делится на две половины и каждая десятичная цифра представляется всего четырьмя битами.

Такой формат позволяет легко переводить десятичные числа в номера соответствующих символов ASCII или ANSI.

Для такого преобразования необходимо поместить соответствующую половину байта в младший конец регистра и добавить 48 для получения кода ASCII или ANSI, соответствующего данному числу.

Два числа в одном байте в формате BCD

Первое числа в виде номера символа ANSI

Второе числа в виде номера символа ANSI

ВНИМАНИЕ! Программная очистка памяти CMOS может привести

к полному отказу начальной загрузки BIOS.

Слайд 36 19. Контроллер клавиатуры

ПЭВМ i8049.

шифратор

Схема контроля дребезга

Буферный регистр

мультиплексор

Контроллер периферии i8255

Буфер (порт 60h/64h)

IRQ1

+ 5

V

Устройство управления

Интерфейс связи с МВ PS/2, IR, USB

Сдвиг СКЭН-кода по состоянию нажатия управляющих клавиш

CLK

СКЭН – поле клавиш клавиатуры

Слайд 37 Схема прерывания

от клавиатуры.

i8049

I8255 60h/64h

Интерфейс с периферией

I8259

Контроллер прерываний

IRQ1

ПЗУ BIOS - XLAT

Обработчик прерывания от клавиатуры

Int9

ОЗУ 0040:001Е - буфер клавиатуры

ASCII или расширенный код

Прерывание программы для вывода символа на экран

ОЗУ А000:0000

видеобуфер

ОЗУ 00F0:0000 программа пользователя

ОЗУ F000:0000 образ символа

монитор

Процедура обработки СКЭН-кодов клавиатуры (XLAT)

Получение скэн-кода

Это клавиша Shift или переключатель

?

Анализ статуса клавиш Shift и переключателей

Выбор кода символа из таблицы ASCII

Помещаем 0 и расширенный код в буфер клавиатуры

Анализ статуса клавиш Shift и переключателей

Клавиша отпущена ?

Это расширенный код?

Это клавиша INS?

Клавиша отпущена ?

конец

конец

конец

конец

Выбор кода символа из таблицы ASCII

Помещаем в буфер код ASCII и скэн-код

Выбор кода нажатой клавиши из таблицы ASCII

да

да

да

да

да

нет

нет

нет

нет

нет

схема буфера клавиатуры

0040:003E 0040:003F 0040:003C 0040:003D 0040:003A 0040:003B 0040:0038 0040:0039 0040:0036 0040:0037 0040:0034 0040:0035 0040:0032 0040:0033 0040:0030 0040:0031 0040:002E 0040:002F 0040:002C 0040:002D 0040:002A 0040:002B 0040:0028 0040:0029 0040:0026 0040:0027 0040:0024 0040:0025 0040:0022 0040:0023 0040:0020 0040:0021 0040:001E 0040:003F 0040:001C 0040:003D 0040:001A 0040:003B

<- указатель хвоста буфера <- указатель головы буфера

<- указатель границы буфера

Схема формирования буфера по принципу FIFO

содержание буфера клавиатуры

вариант 1

клавиши управления, функциональные клавиши и их комбинации

вариант 2

буквенно-цифровые клавиши и их комбинации с клавишами изменения регистра

вариант 3

ALT-ввод номера символа ASCII при нажатой клавише “alt”

Содержание команды программирования контроллера клавиатуры

<- первый байт в порт 64h

<-второй байт в порт 64h

Задержка (0,25-1сек) Число повторов в секунду (2-30)

Слайд 41Содержание констант статуса клавиш-переключателей в ОЗУ

<- первый байт 0040:0017

<-второй байт 0040:0018

0040:0017 бит = 1

7 – insert

6 – caps lock

5 – num lock включено

4 – scroll lock

3 – alt

2 - ctrl

1 – левый schift

0 – правый schift

0040:0018 клавиша нажата

7 – insert

6 – caps lock

5 – num lock

4 – scroll lock

3 – ctrl + num lock включено

2

1 не используется

0

Для работы с буфером клавиатуры используются функции прерывания BIOS 21h, для работы с контроллером – 16h.