Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

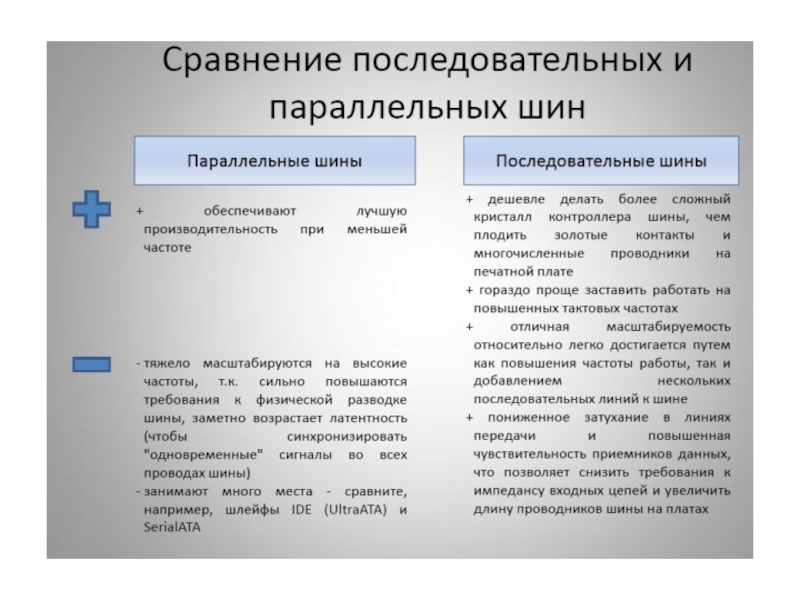

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

шины, память, макросы

Содержание

- 1. шины, память, макросы

- 2. Вычислительная машина с одной шинойВычислительная машина с тремя видами шинСтруктура взаимосвязей с двумя видами шин

- 3. Шина — это несколько проводников, соединяющих различные

- 4. АЛУРегистрыМикросхема процессораКонтроллершиныПамятьШинапамятиHDDПринтерШина ввода-выводаВстроенная в микросхему шинаТипичная компьютерная организация с несколькими шинами

- 5. Слайд 5

- 6. Слайд 6

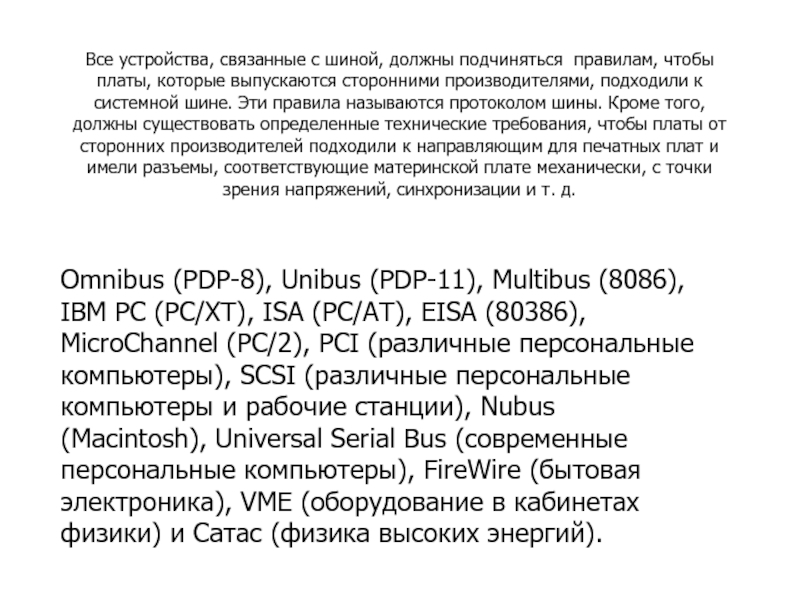

- 7. Все устройства, связанные с шиной, должны подчиняться

- 8. Слайд 8

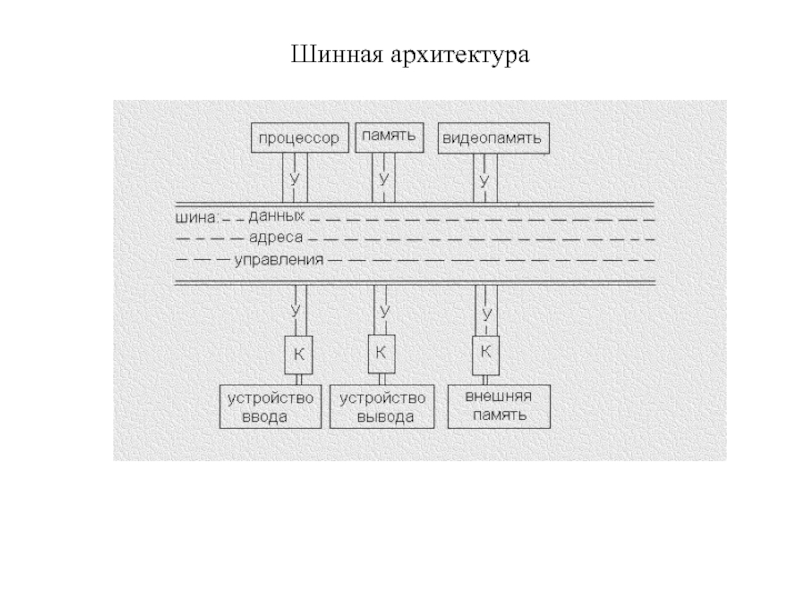

- 9. Шинная архитектура

- 10. Слайд 10

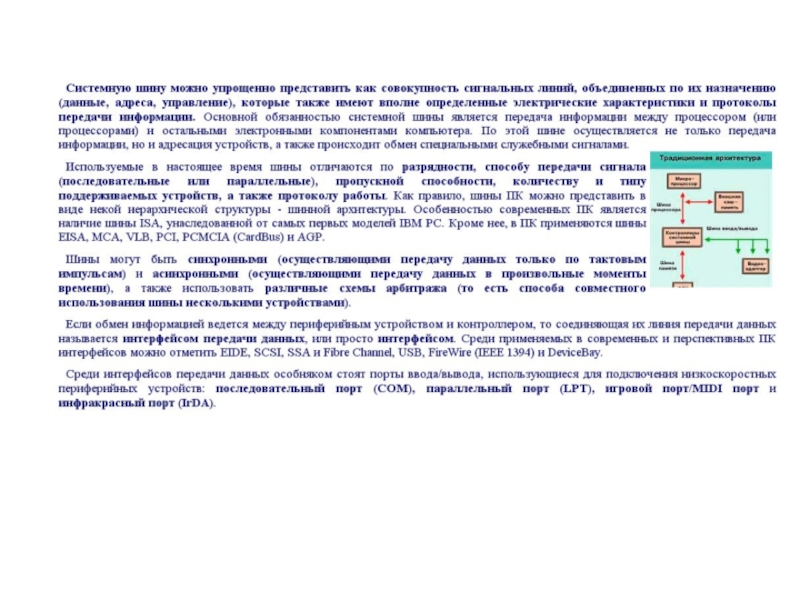

- 11. ШиныШина - это группа проводников, соединяющих различные

- 12. Все связанные с шиной устройства при взаимодействии

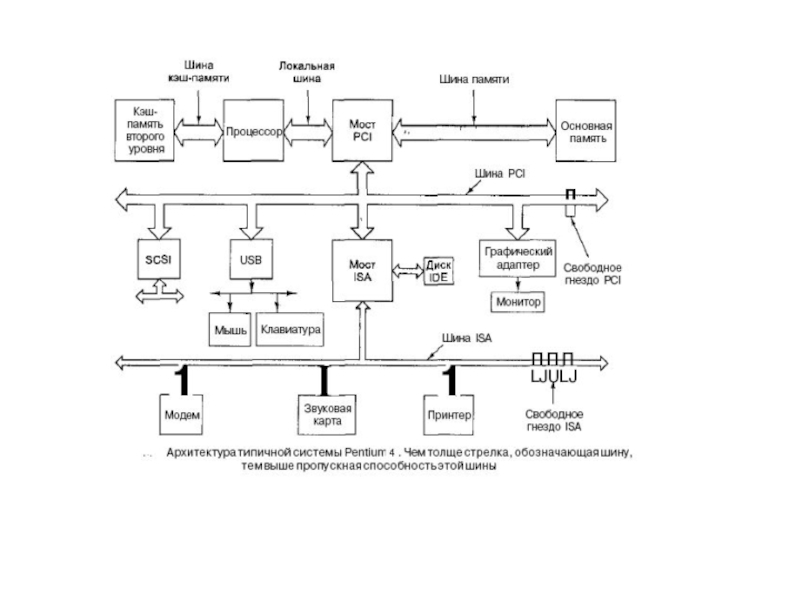

- 13. В современном ПК довольно много шин периферийных

- 14. Зачем придумали шинуВ 70-х годах, после изобретения

- 15. Одни устройства, связанные с шиной, являются активными

- 16. Обычно сами устройства не могут давать достаточно

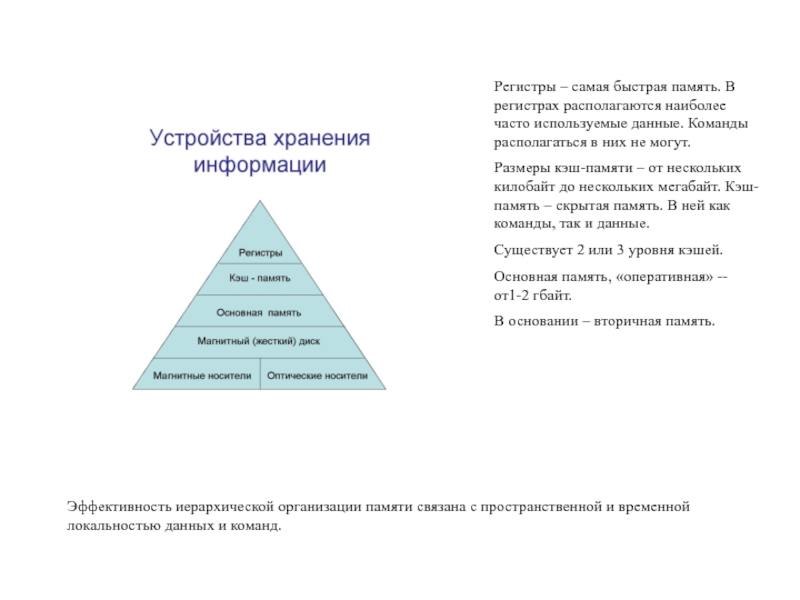

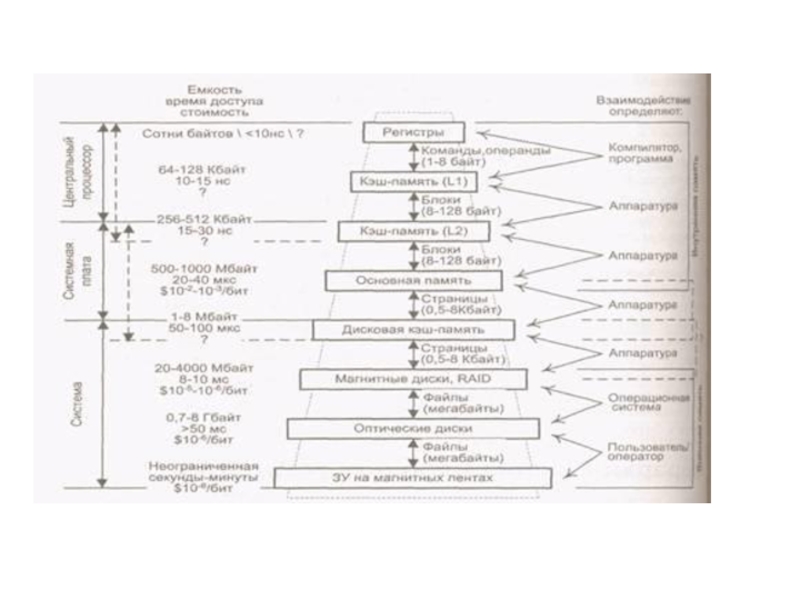

- 17. Устройство шинОбычно шина содержит набор адресных линий,

- 18. Синхронизация шиныСинхронные шины - шина, которая содержит

- 19. ПримерПусть у нас есть синхронная шина с

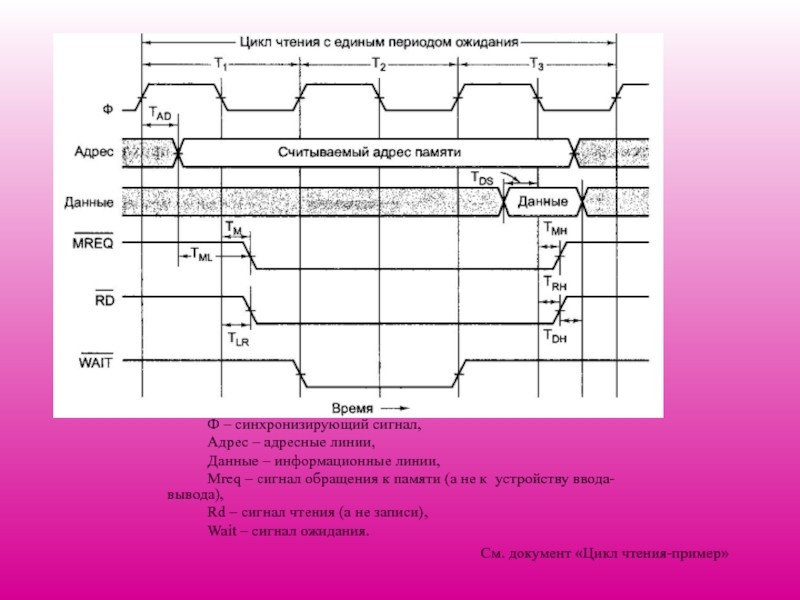

- 20. Ф – синхронизирующий сигнал, Aдрес – адресные линии, Данные

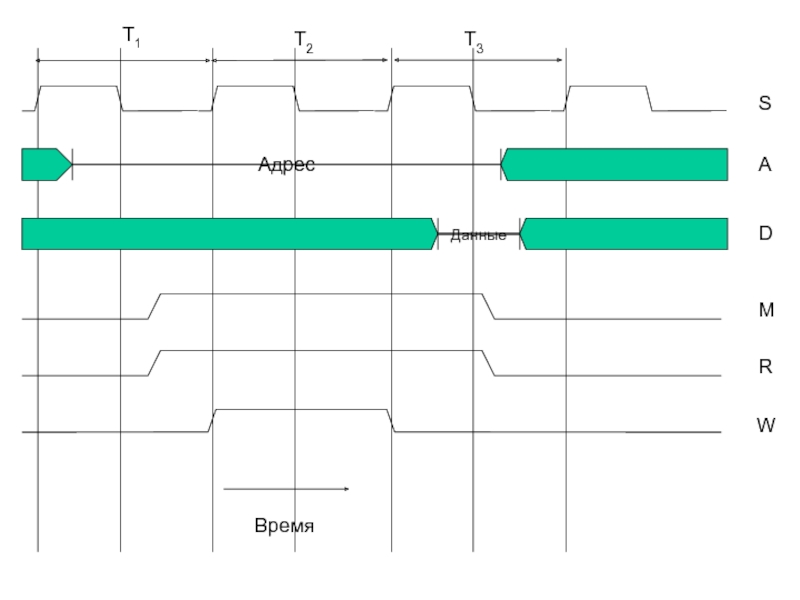

- 21. АдресДанныеВремяТ1Т2Т3SADMRW

- 22. Что лучше?Преимущества асинхронной шины очевидны. Но синхронную

- 23. Арбитраж шиныНа одной шине может быть несколько

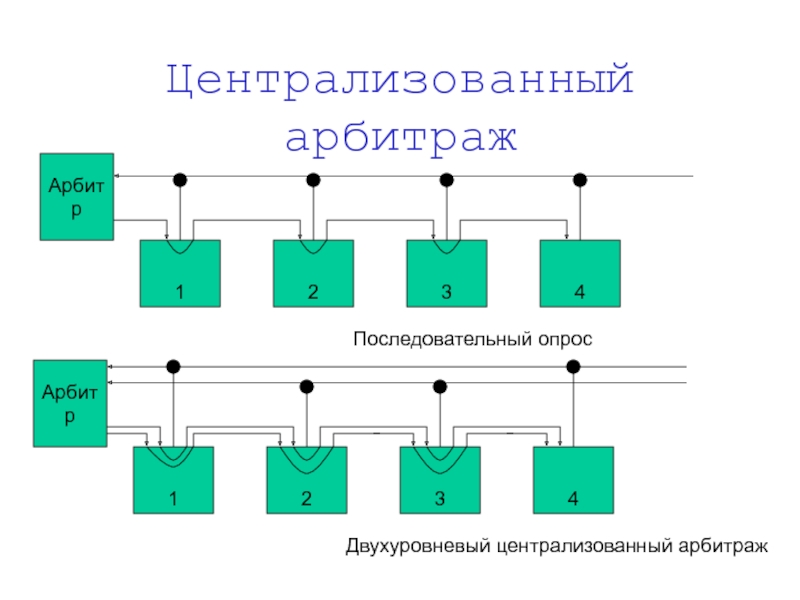

- 24. Централизованный арбитраж1234АрбитрПоследовательный опрос1234АрбитрДвухуровневый централизованный арбитраж

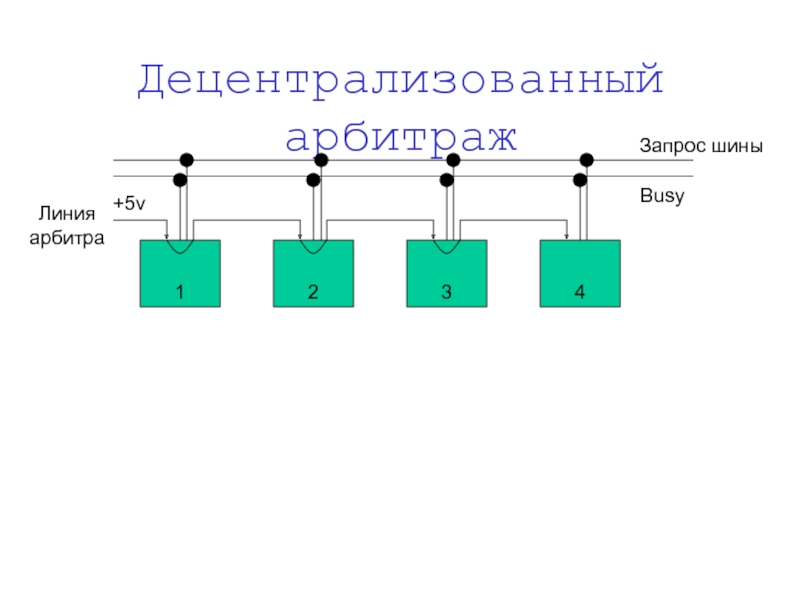

- 25. Децентрализованный арбитраж1234Запрос шиныBusy+5vЛинияарбитра

- 26. Скорость передачи данных по шине зависит от

- 27. PCIПервую версию шины PCI (Peripheral Component Interconnect

- 28. Слайд 28

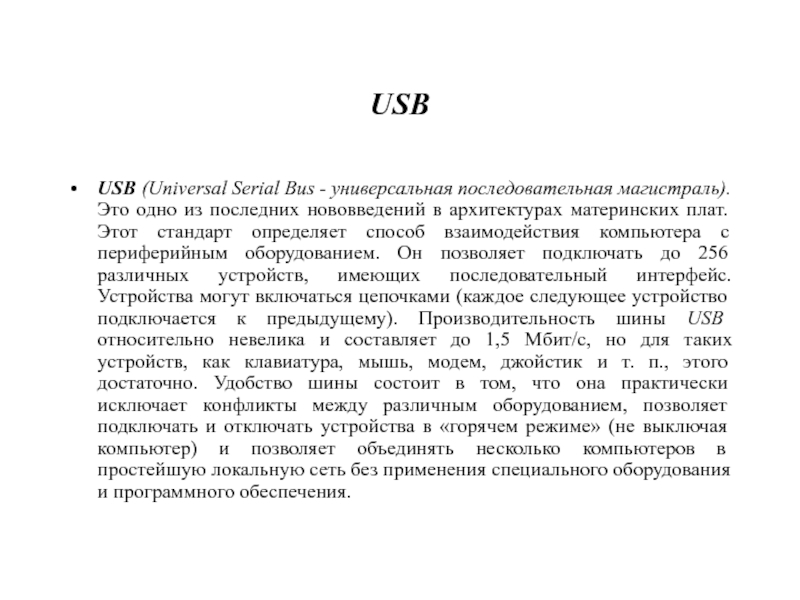

- 29. USBUSB (Universal Serial Bus - универсальная последовательная

- 30. http://library.krasu.ru/ft/ft/b72/0227142/pdf/6/13a.pdfРасскажите о тенденции развития шин передачи данныхЧто

- 31. Общение программы с "внешним миром" на компьютере с общей шиной (глазами системного программиста)

- 32. Центральный процессор может обмениваться с портами байтами

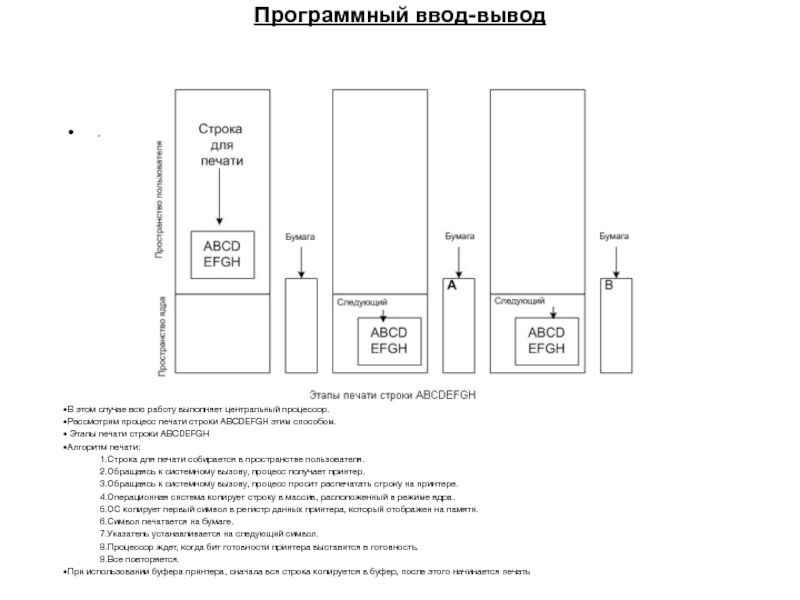

- 33. Программный ввод-вывод .В этом случае всю работу

- 34. Дальние подпрограммы. Макросы

- 35. Слайд 35

- 36. Слайд 36

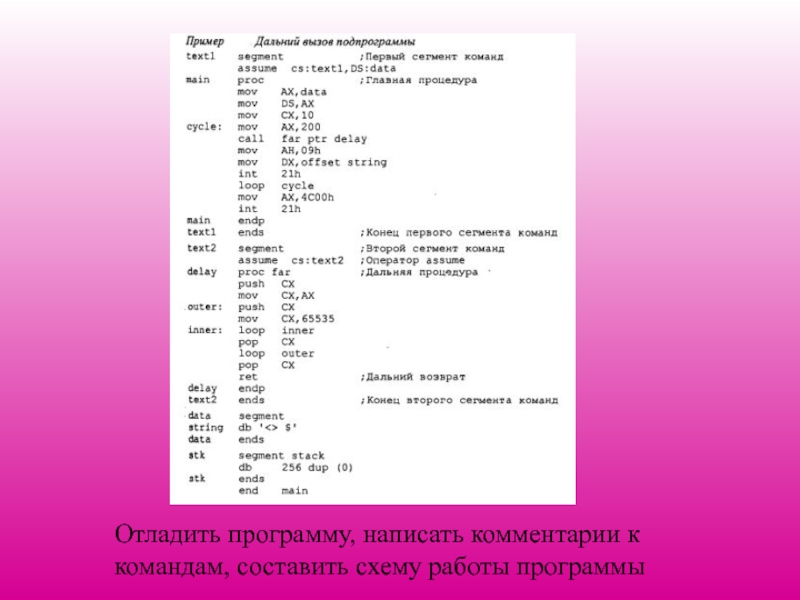

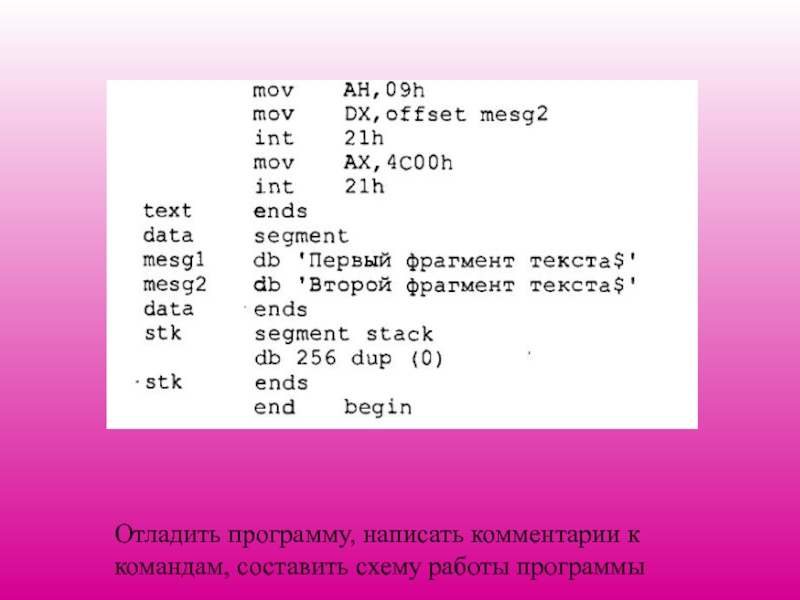

- 37. Отладить программу, написать комментарии к командам, составить схему работы программы

- 38. Слайд 38

- 39. Слайд 39

- 40. Слайд 40

- 41. Слайд 41

- 42. Слайд 42

- 43. Слайд 43

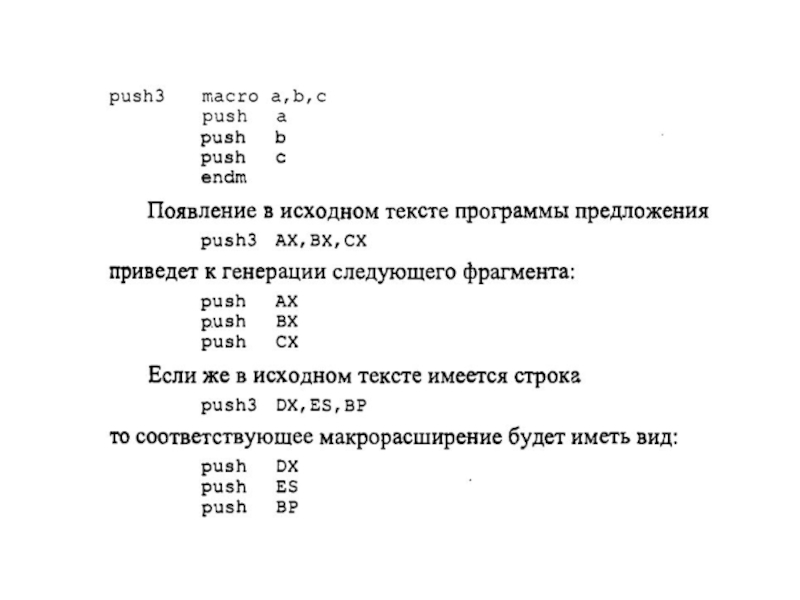

- 44. Отладить программу, написать комментарии к командам, составить схему работы программы

- 45. Отладить программу, написать комментарии к командам, составить схему работы программы

- 46. Главная задача компьютерной системы – выполнять программы.

- 47. Память - совокупность отдельных устройств, которые запоминают,

- 48. В некоторых запоминающих устройствах считывание данных сопровождается

- 49. Запоминающие устройства с произвольным доступом. Цикл обращения

- 50. Слайд 50

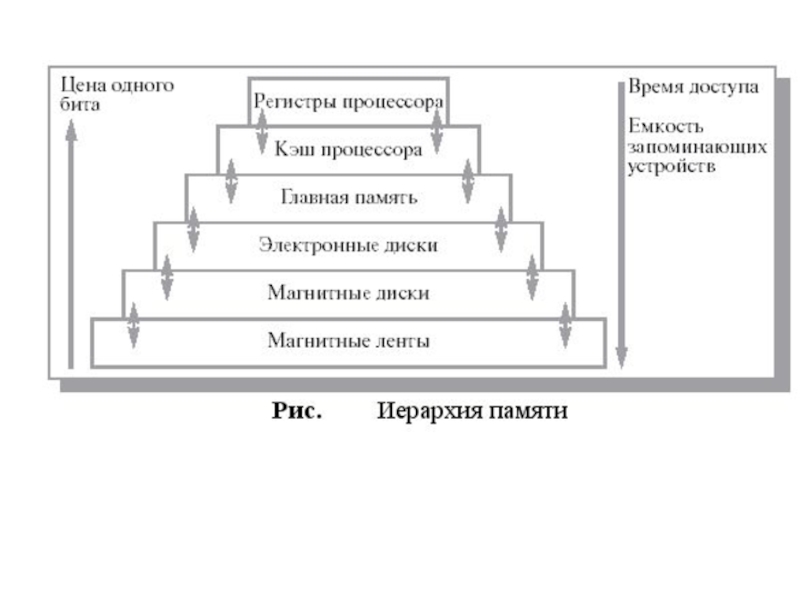

- 51. Параллельность работы и иерархия памятиБыстродействие компьютерной системы

- 52. Регистры – самая быстрая память. В регистрах

- 53. Слайд 53

- 54. Слайд 54

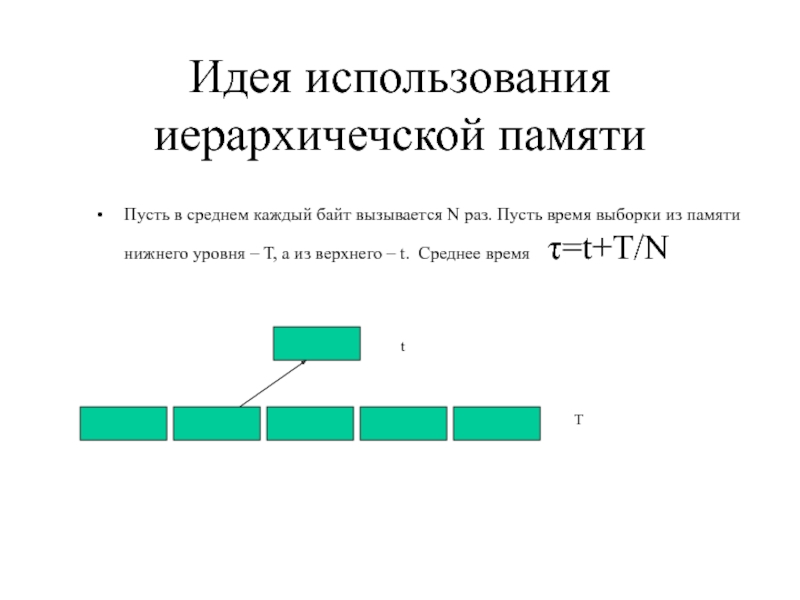

- 55. Идея использования иерархичечской памятиПусть в среднем каждый

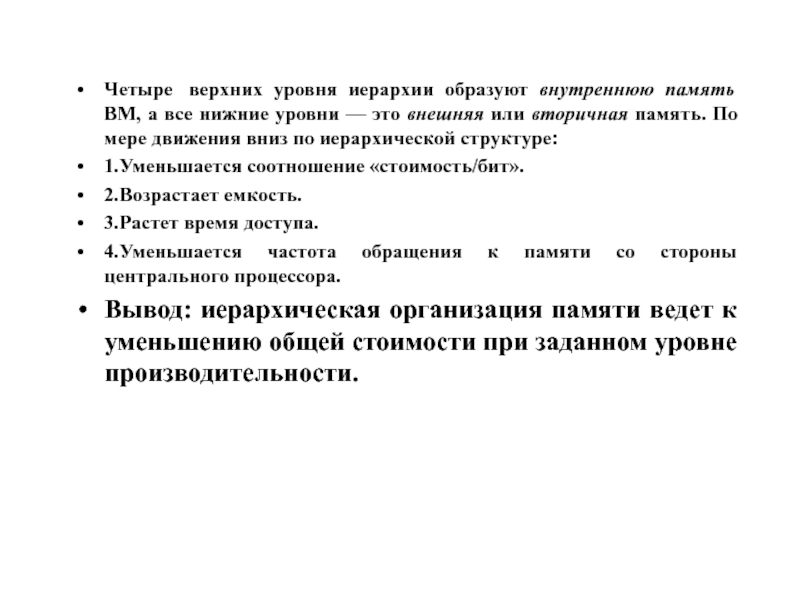

- 56. Четыре верхних уровня иерархии образуют внутреннюю память

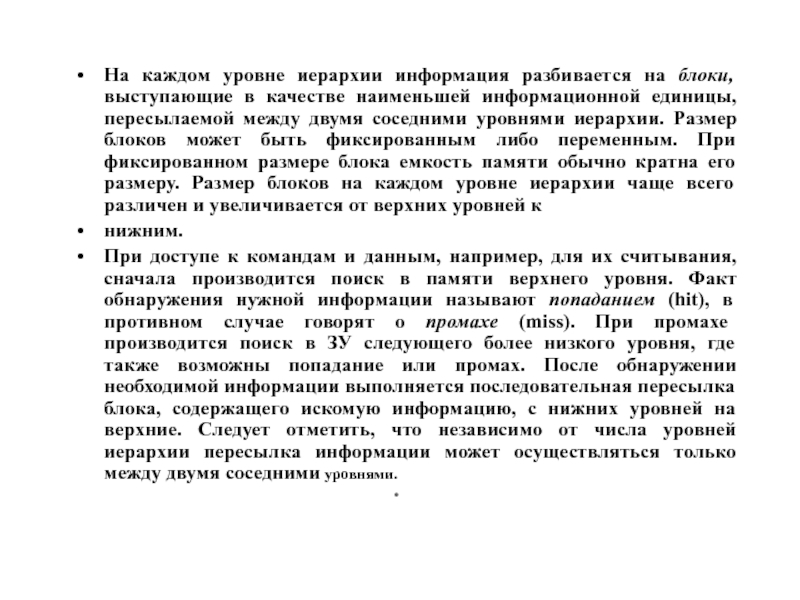

- 57. На каждом уровне иерархии информация разбивается на

- 58. Параллельность работы. ИдеяПараллельная работа разных уровней памяти,

- 59. Буфер и Кэш Эти термины не являются

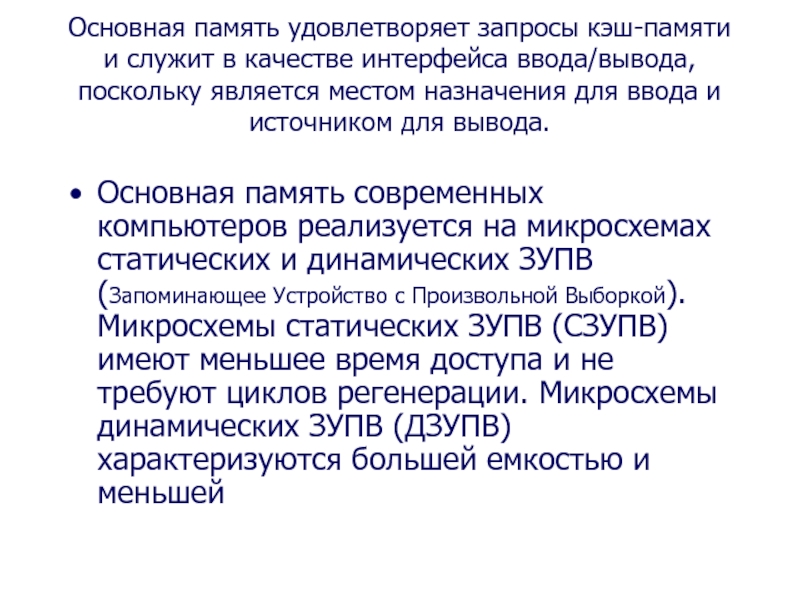

- 60. Основная память удовлетворяет запросы кэш-памяти и служит

- 61. Слайд 61

- 62. Слайд 62

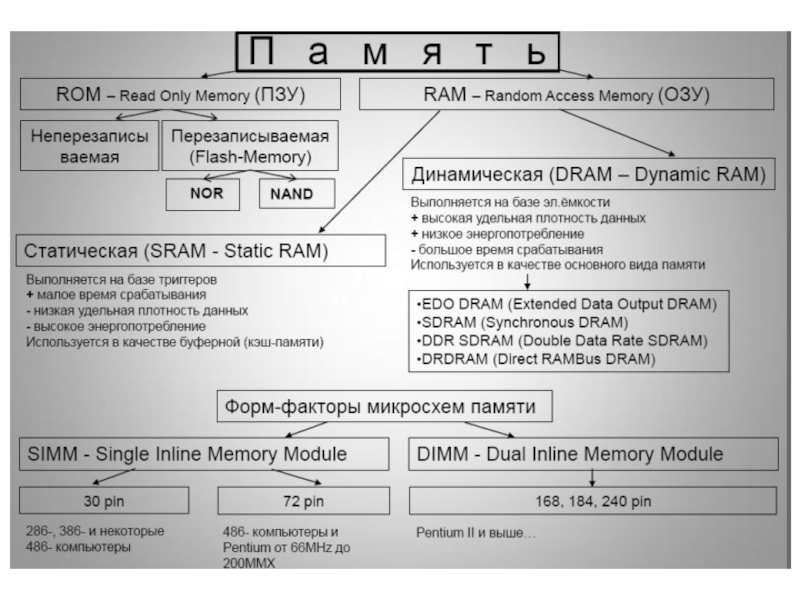

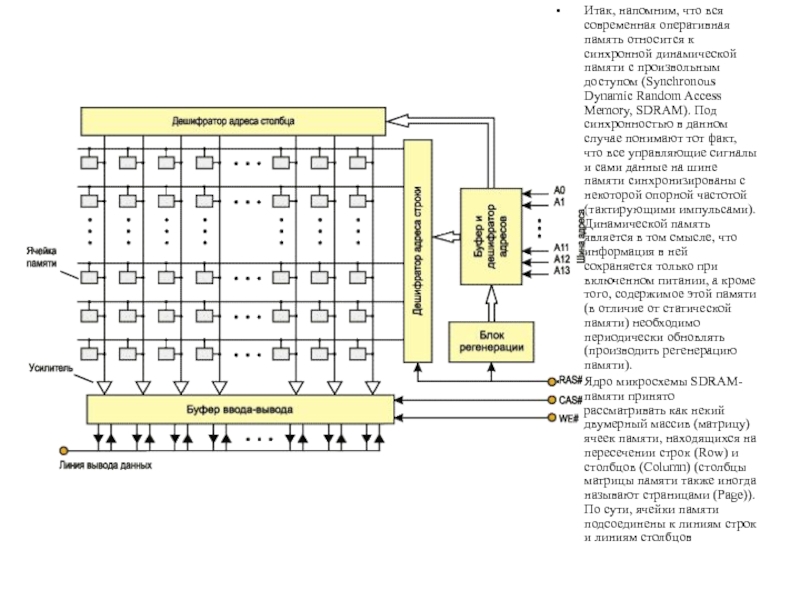

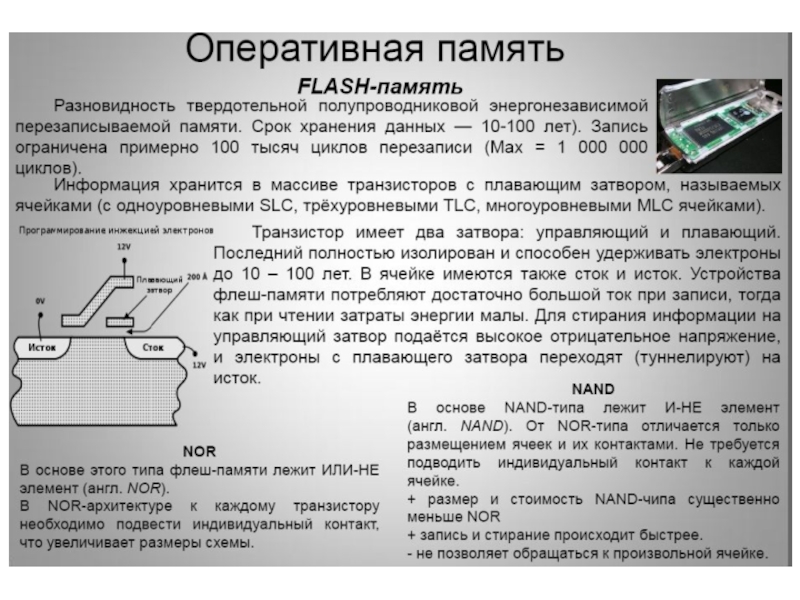

- 63. Итак, напомним, что вся современная оперативная память

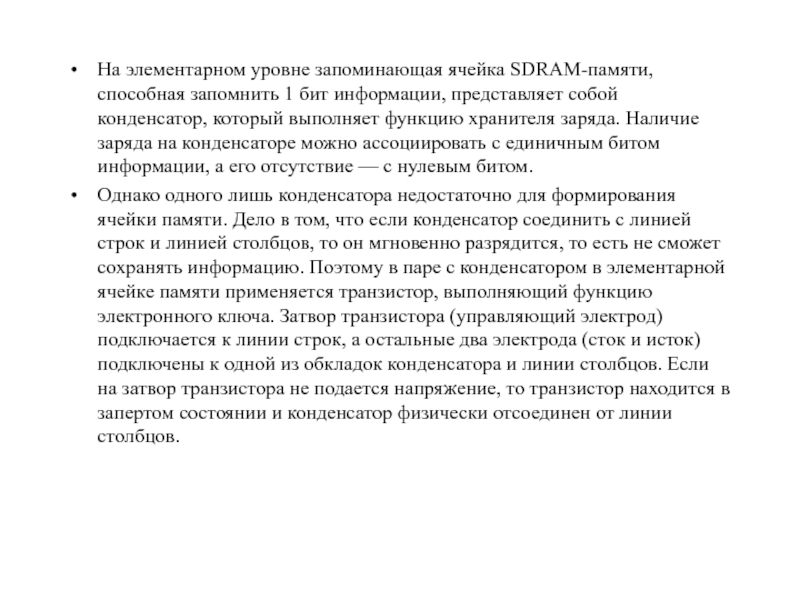

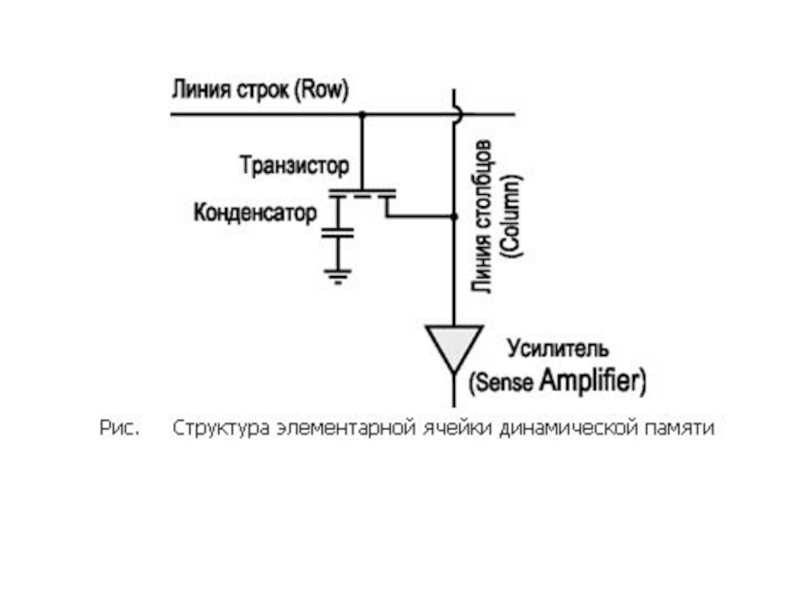

- 64. На элементарном уровне запоминающая ячейка SDRAM-памяти, способная

- 65. Слайд 65

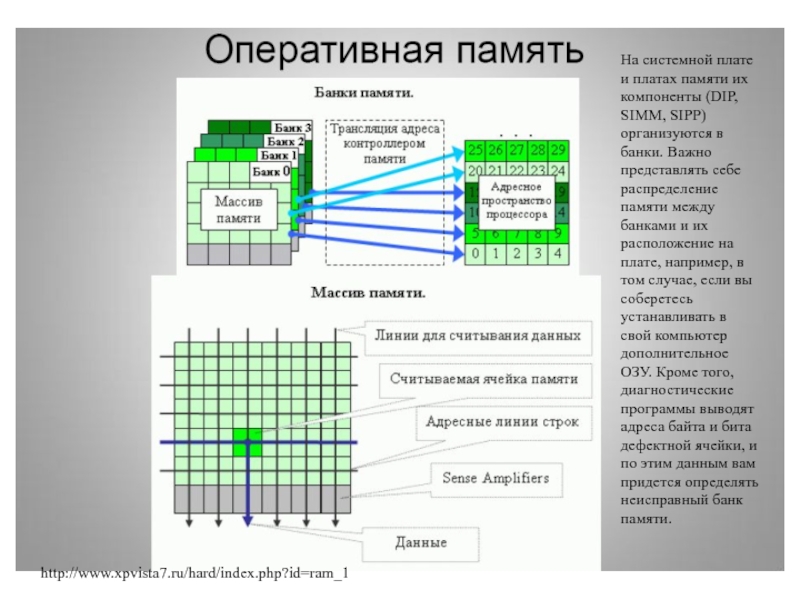

- 66. На системной плате и платах памяти их

- 67. Слайд 67

- 68. Слайд 68

- 69. Слайд 69

- 70. Слайд 70

- 71. Слайд 71

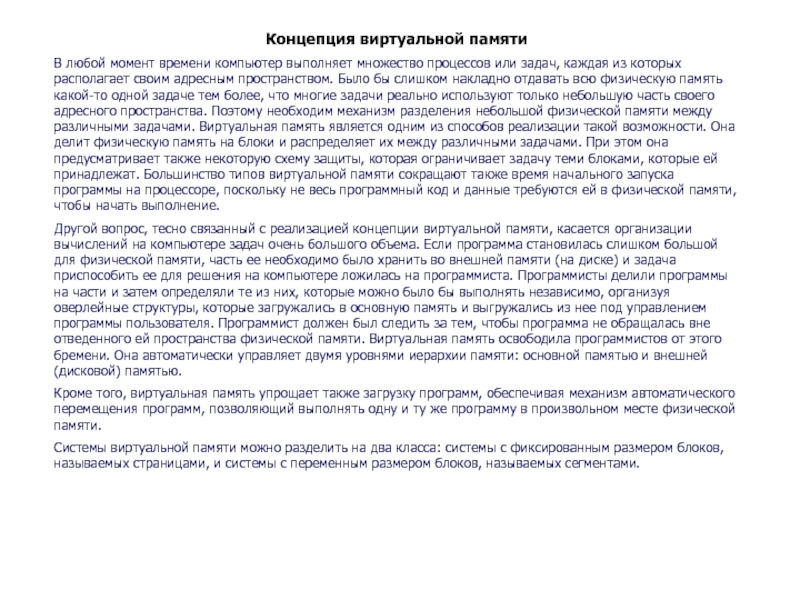

- 72. Концепция виртуальной памятиВ любой момент времени компьютер

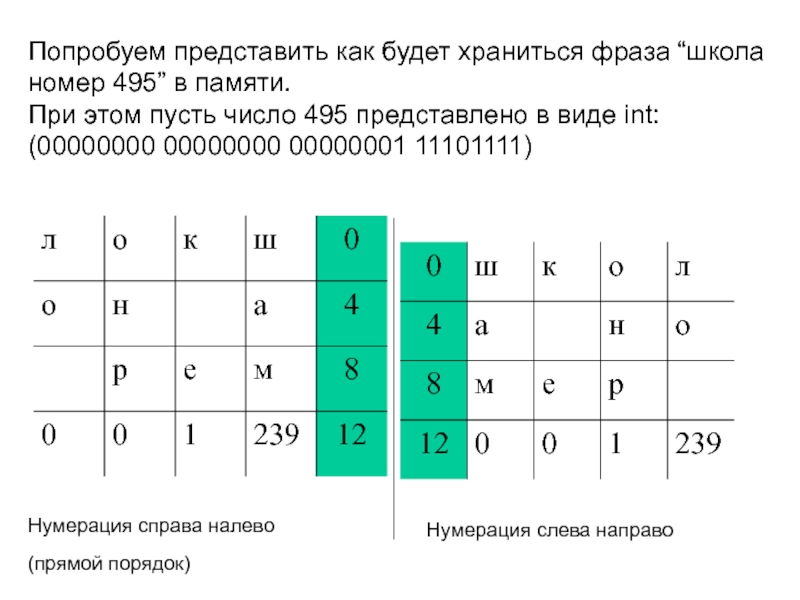

- 73. Нумерация справа налевоНумерация слева направо(прямой порядок)Попробуем представить

- 74. ПроблемаЕсли мы попробуем скопировать такие данные по

- 75. ОшибкиПамять компьютера время от времени может делать

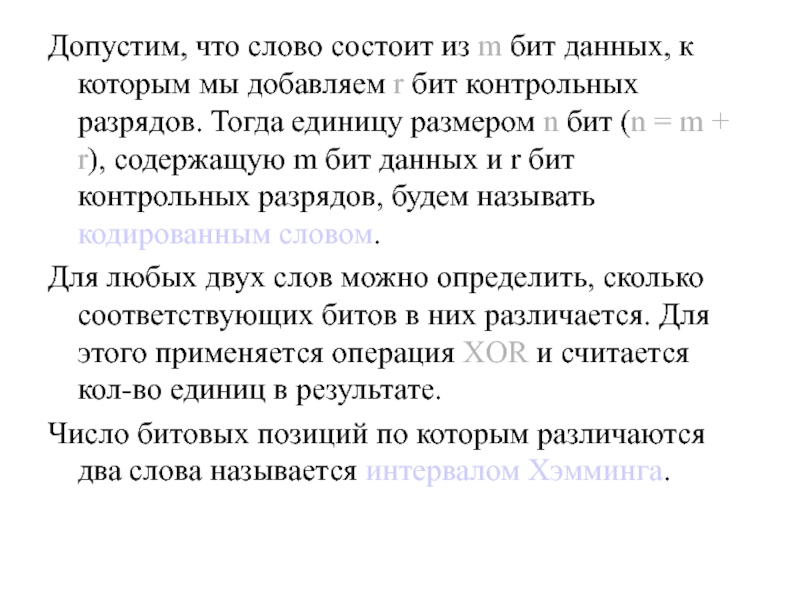

- 76. Допустим, что слово состоит из m бит

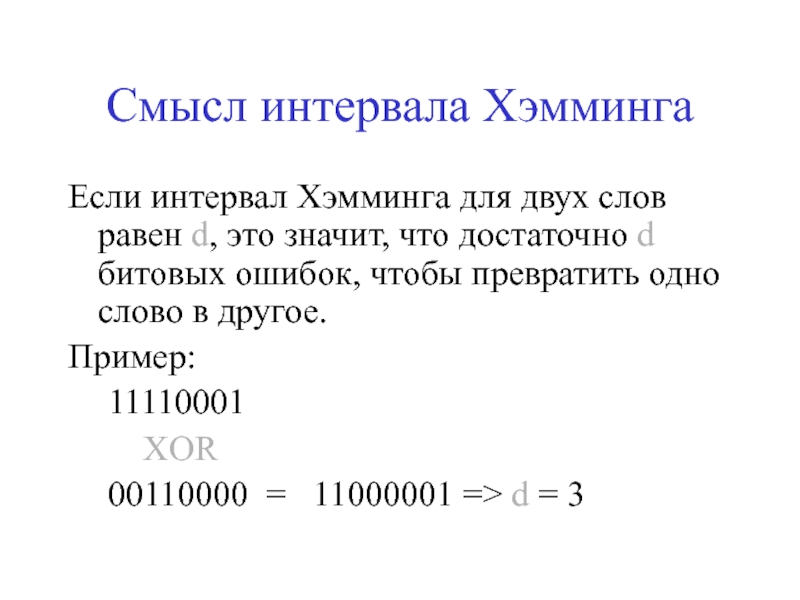

- 77. Смысл интервала ХэммингаЕсли интервал Хэмминга для двух

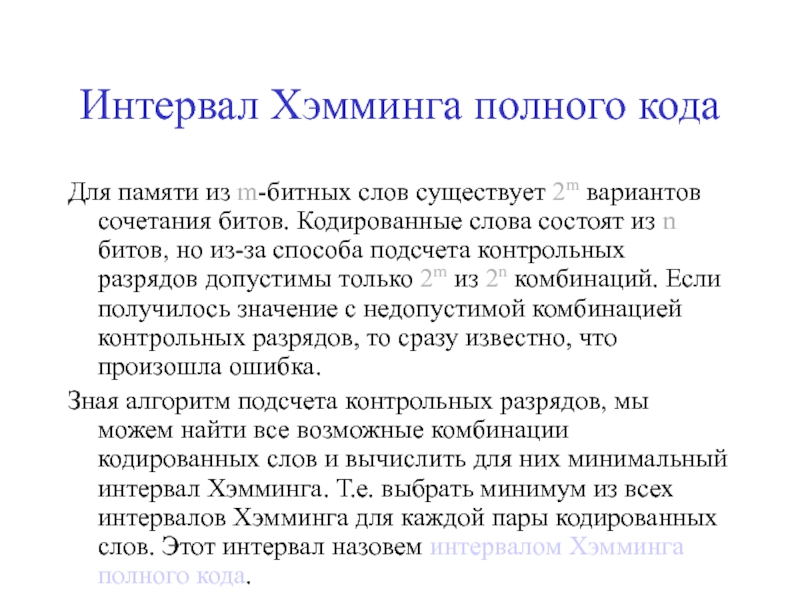

- 78. Интервал Хэмминга полного кодаДля памяти из m-битных

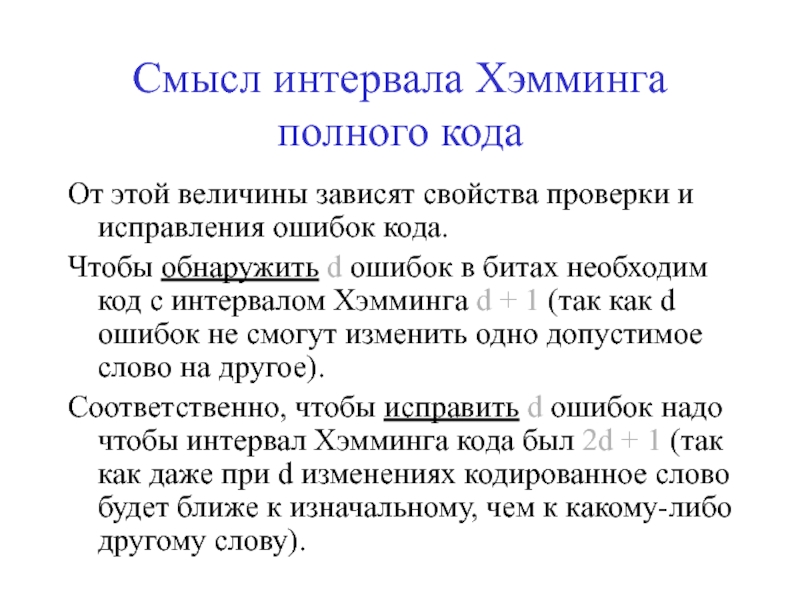

- 79. Смысл интервала Хэмминга полного кодаОт этой величины

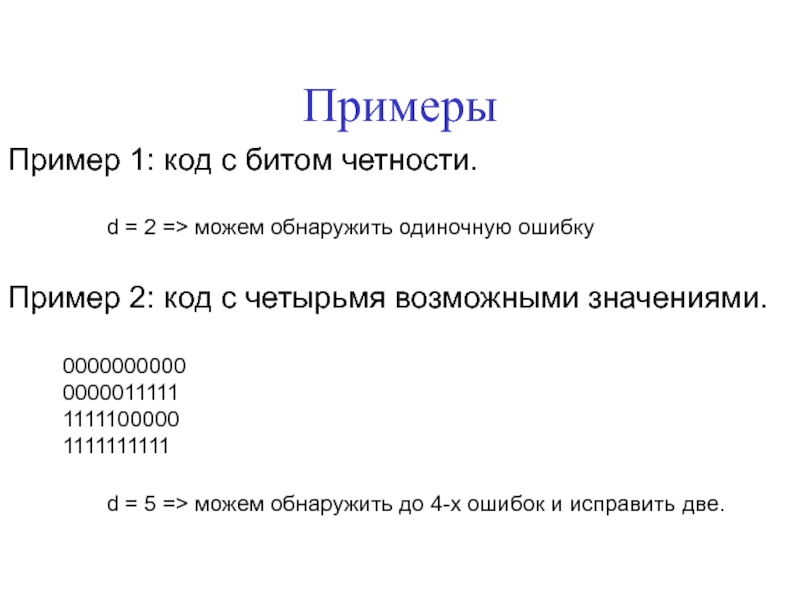

- 80. ПримерыПример 1: код с битом четности.Пример 2:

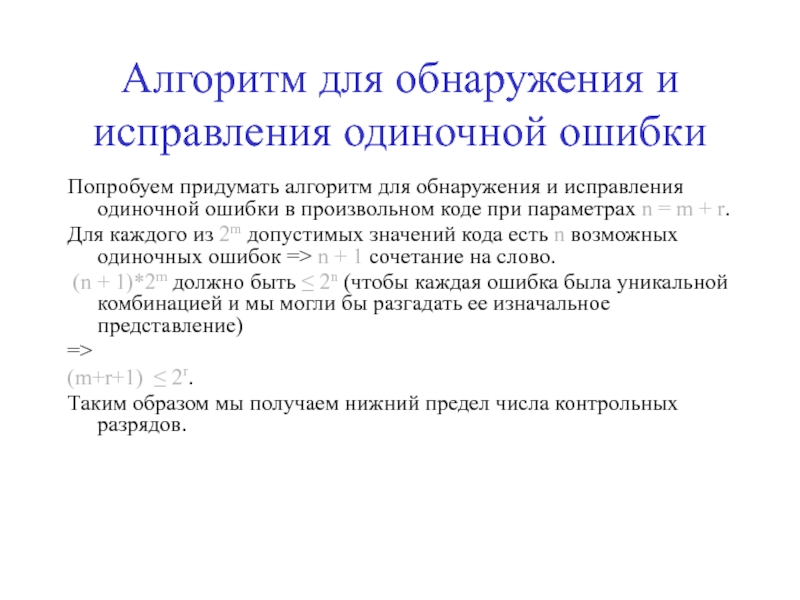

- 81. Алгоритм для обнаружения и исправления одиночной ошибкиПопробуем

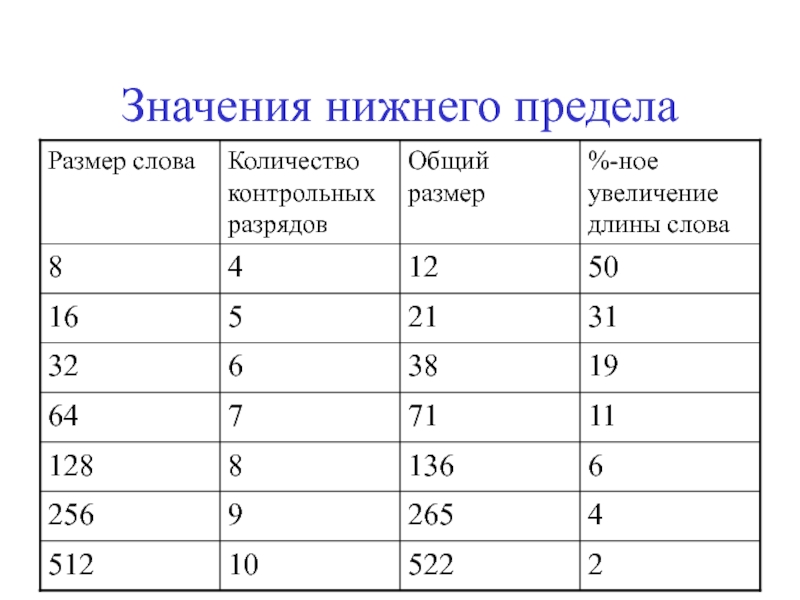

- 82. Значения нижнего предела

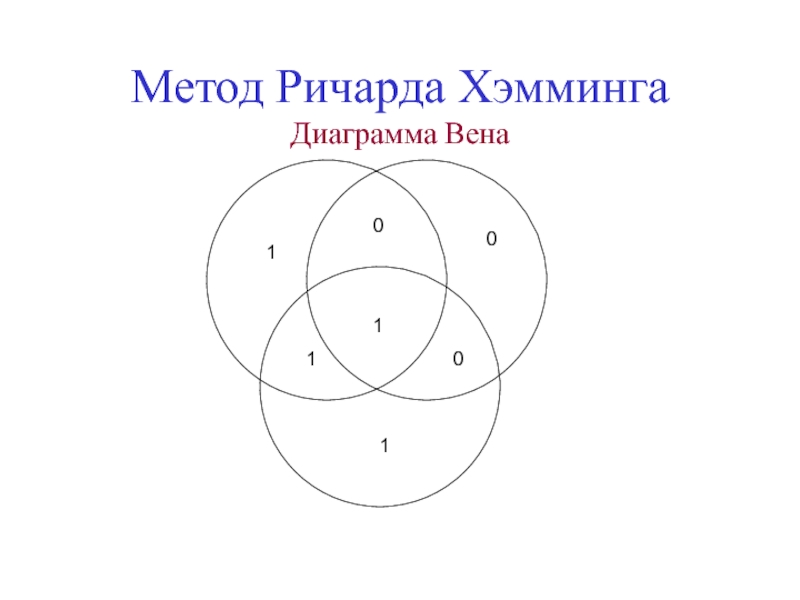

- 83. Метод Ричарда Хэмминга Диаграмма Вена1100101

- 84. Виртуальная память – воображаемая память, по объёму

- 85. Диск Страничная организация памятиАнализ страничной организацииБуфер быстрого преобразования адресаСегментная организация ВыводыДалее…

- 86. Скачать презентанцию

Слайды и текст этой презентации

Слайд 1Позвоночник компьютера

Каждое устройство имеет контроллер (например, контроллер жестких дисков)

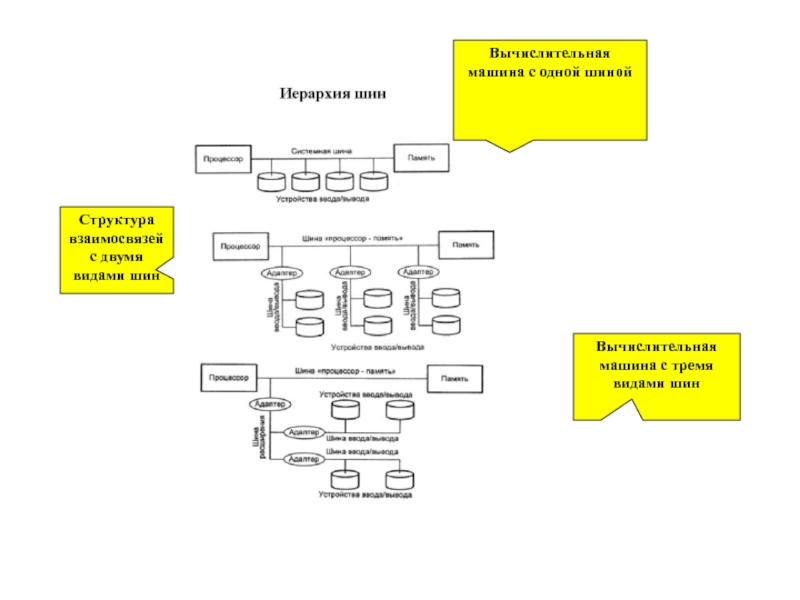

Слайд 2Вычислительная машина с одной шиной

Вычислительная машина с тремя видами шин

Структура

взаимосвязей с двумя видами шин

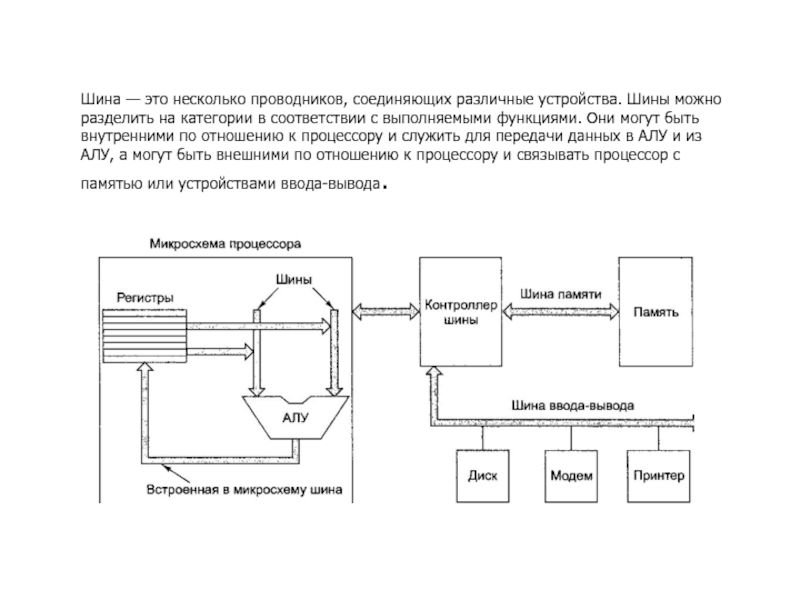

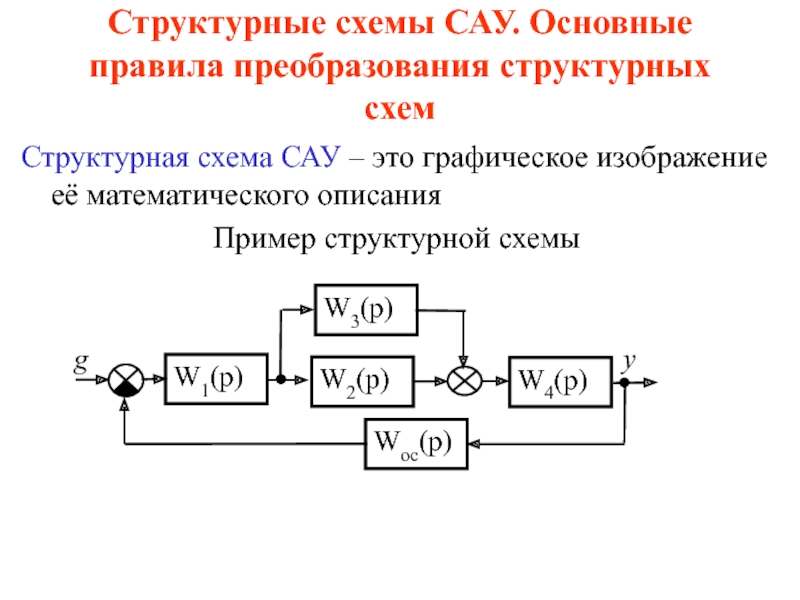

Слайд 3Шина — это несколько проводников, соединяющих различные устройства. Шины можно

разделить на категории в соответствии с выполняемыми функциями. Они могут

быть внутренними по отношению к процессору и служить для передачи данных в АЛУ и из АЛУ, а могут быть внешними по отношению к процессору и связывать процессор с памятью или устройствами ввода-вывода.

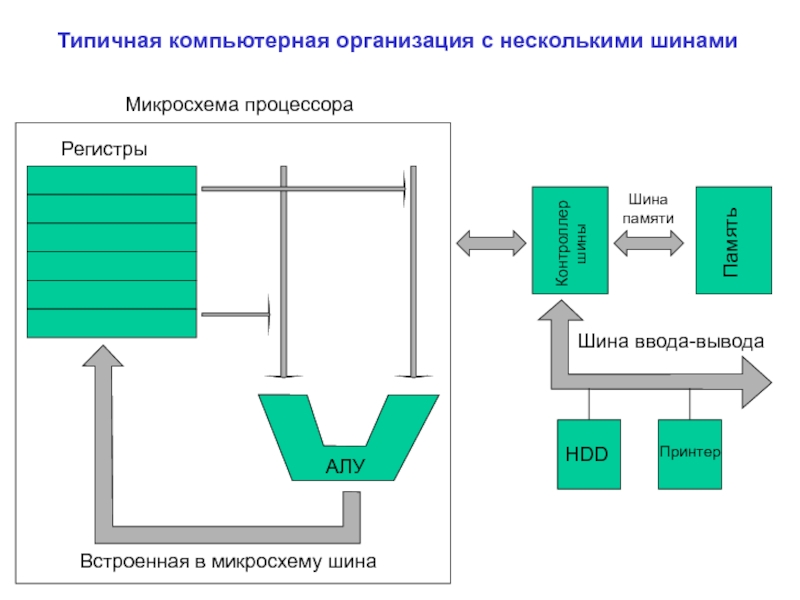

Слайд 4

АЛУ

Регистры

Микросхема процессора

Контроллер

шины

Память

Шина

памяти

HDD

Принтер

Шина ввода-вывода

Встроенная в микросхему шина

Типичная компьютерная организация с несколькими

шинами

Слайд 7Все устройства, связанные с шиной, должны подчиняться правилам, чтобы платы,

которые выпускаются сторонними производителями, подходили к системной шине. Эти правила

называются протоколом шины. Кроме того, должны существовать определенные технические требования, чтобы платы от сторонних производителей подходили к направляющим для печатных плат и имели разъемы, соответствующие материнской плате механически, с точки зрения напряжений, синхронизации и т. д.Omnibus (PDP-8), Unibus (PDP-11), Multibus (8086), IBM PC (PC/XT), ISA (PC/AT), EISA (80386), MicroChannel (PC/2), PCI (различные персональные компьютеры), SCSI (различные персональные компьютеры и рабочие станции), Nubus (Macintosh), Universal Serial Bus (современные персональные компьютеры), FireWire (бытовая электроника), VME (оборудование в кабинетах физики) и Сатас (физика высоких энергий).

Слайд 11Шины

Шина - это группа проводников, соединяющих различные устройства. Шины могут

быть внутренними по отношению к процессору и внешними. Внутренние служат

для передачи данных в АЛУ. Внешние связывают процессор с памятью или устройствами ввода-вывода.Слайд 12Все связанные с шиной устройства при взаимодействии с ней должны

придерживаться некоторого набора правил – называемого протоколом шины. Он необходим

для того чтобы к одной шине можно было подключать устройства разных производителей.Примеры известных шин:

PCI (Peripheral Component Interconnect),

USB (Universal Serial Bus),

ISA (Industry Standard Architecture).

Слайд 13В современном ПК довольно много шин периферийных устройств (USB, FireWare

и др.), работающих на разных скоростях, поэтому для оптимизации работы

ПК на материнской плате реализованы два моста: северный – для высокоскоростных периферийных устройств, таких как видеоадаптер, и южный – для низкоскоростных периферийных устройств, таких как SerialATA (не удивляйся, SATA считается низкоскоростным устройством), USB, FireWare. Северный мост подключен к шине процессора, а южный - к северному мосту по специальной шине.Слайд 14Зачем придумали шину

В 70-х годах, после изобретения первого микропроцессора и

создания первого персонального компьютера, встал вопрос о возможностях расширения компьютера

без замены материнской платы. Было решено использовать гнезда расширения, расположенные непосредственно на материнской плате, в которые подключались платы расширения. Первым компьютером, обладавшим гнездами расширения, был Apple II. Он получил большую популярность именно благодаря наличию в нем этих гнезд. Архитектура этого компьютера с незначительными изменениями легла в основу IBM PC. Такое устройство ПК, с возможностью вставлять в системный блок дополнительные платы, получило название "открытая архитектура". Благодаря открытой архитектуре сейчас мы можем выбирать видеокарту какого производителя нам покупать, через какой модем выходить в Интернет и каким звуком наслаждаться. А из-за того, что инженеры IBM подробно документировали спецификацию шины расширений и открыли свободный доступ к документации, заинтересованные фирмы получили возможность создавать собственные платы расширения, увеличивая популярность и возможности персонального компьютера.Слайд 15Одни устройства, связанные с шиной, являются активными и могут инициировать

передачу информации по шине. Их называют задающими устройствами. Другие устройства

являются пассивными и могут только ждать запросов. Их называют подчиненными устройствами. Одни и те же устройства могут быть как задающими, так и подчиненными.Пример:

Процессор запрашивает контроллер жестких дисков о чтении: процессор – задающее устройство, контроллер – подчиненное.

Жесткий диск произвел чтение и теперь его контроллер запрашивает память на запись: память – подчиненное устройство, контроллер – задающее.

P.S.: память никогда не может быть задающим устройством!

Слайд 16Обычно сами устройства не могут давать достаточно интенсивного сигнала, поэтому

они подключаются к шине через одно из специальных устройств (драйвер

шины для задающих, приемник шины для подчиненных или приемопередатчик шины для устройств, которые могут играть обе роли).Слайд 17Устройство шин

Обычно шина содержит набор адресных линий, набор информационных линий

и набор линий управления.

Ширина шины - общее количество линий.

Кол-во адресных задает максимальное адресуемое процессором пространство памяти.

Кол-во информационных линий влияет на скорость передачи данных.

Скорость передачи данных также можно повысить за счет сокращения времени цикла шины, т.е. сделать большее количество передач в секунду. Но чем больше скорость тем больше перекос шины (явление, когда по разным линиям данные передаются за разный промежуток времени разной скоростью).

Многие современные шины - мультиплексные, т.е. у них одни и те же линии используются как для данных, так и для адреса.

Слайд 18Синхронизация шины

Синхронные шины - шина, которая содержит линию синхронизации, запускаемую

кварцевым генератором. Любое действие занимает целое число циклов шины.

Асинхронная шина

не содержит задающего генератора. Циклы такой шины могут быть разной длины и необязательно одинаковыми для разных устройств.Слайд 19Пример

Пусть у нас есть синхронная шина с тактовым генератором, производящим

сигнал каждые 25 нс (40 МГц).

Время чтения из памяти пусть

занимает 40 нс.Посмотрим как будет работать такая синхронная шина, если понадобилось прочитать данные из памяти.

Нам понадобятся следующие линии (наборы линий):

Ф – синхронизирующий сигнал,

Aдрес – адресные линии,

Данные – информационные линии,

Mreq – сигнал обращения к памяти (а не к устройству ввода-вывода),

Rd – сигнал чтения (а не записи),

Wait – сигнал ожидания.

Слайд 20

Ф – синхронизирующий сигнал,

Aдрес – адресные линии,

Данные – информационные линии,

Mreq

– сигнал обращения к памяти (а не к устройству ввода-вывода),

Rd

– сигнал чтения (а не записи),Wait – сигнал ожидания.

См. документ «Цикл чтения-пример»

Слайд 22Что лучше?

Преимущества асинхронной шины очевидны. Но синхронную шину построить гораздо

легче. Более того, в разработку синхронных шин уже вложено большое

количество средств. Поэтому большинство современных шин – синхронные.Слайд 23Арбитраж шины

На одной шине может быть несколько задающих устройств. Чтобы

не было путаницы кому сейчас можно использовать шину, а кому

нет, вводится специальный механизм - арбитраж шины.Другими словами: Арбитраж шины -механизм выбора задающего устройства для следующего свободного цикла шины.

Слайд 24Централизованный арбитраж

1

2

3

4

Арбитр

Последовательный опрос

1

2

3

4

Арбитр

Двухуровневый централизованный арбитраж

Слайд 26Скорость передачи данных по шине зависит от частоты шины и

от ее разрядности. Естественно, чем больше частота, тем быстрее передаются

данные. И чем больше разрядность - тем больше данных шина может передать за один такт.Слайд 27PCI

Первую версию шины PCI (Peripheral Component Interconnect - взаимосвязь периферийных

компонентов) Intel закончила еще весной 1991 года. Перед инженерами компании

была поставлена задача разработать недорогое и производительное решение, которое позволит реализовать все возможности новых процессоров 486/Pentium/PPro. В 1992 году появилась первая версия шины PCI, Intel объявила, что стандарт шины будет открытым и создала PCI Special Interest Group. Благодаря этому любой заинтересованный разработчик получил возможность создавать устройства для шины PCI не тратя деньги на лицензию. Первая версия шины имела тактовую частоту 33 МГц, она могла быть 32 или 64 разрядной, и устройства могли работать с сигналами в 5 В или 3,3 В. Теоретически, пропускная способность шины 132 Мбайт/сек, однако в реальности пропускная способность около 80 Мбайт/сек.Год спустя, в 1993 году, появилась вторая версия шины, а в 1995 появилась версия PCI 2.1 (еще одно название - "параллельная шина PCI"), которая существует и по сей день. Она обеспечивает передачу данных по шине с частотой 66 МГц и максимальная скорость передачи 528 Мб/сек. Кроме этого, шина полностью поддерживает все возможности технологии Plug and Play (PnP).

Как и ISA, шина PCI так полюбилась различным разработчикам, что была перенесена на платформы с процессорами Alpha, MIPS, PowerPC, SPARC и т.д.

Слайд 29USB

USB (Universal Serial Bus - универсальная последовательная магистраль). Это одно

из последних нововведений в архитектурах материнских плат. Этот стандарт определяет

способ взаимодействия компьютера с периферийным оборудованием. Он позволяет подключать до 256 различных устройств, имеющих последовательный интерфейс. Устройства могут включаться цепочками (каждое следующее устройство подключается к предыдущему). Производительность шины USB относительно невелика и составляет до 1,5 Мбит/с, но для таких устройств, как клавиатура, мышь, модем, джойстик и т. п., этого достаточно. Удобство шины состоит в том, что она практически исключает конфликты между различным оборудованием, позволяет подключать и отключать устройства в «горячем режиме» (не выключая компьютер) и позволяет объединять несколько компьютеров в простейшую локальную сеть без применения специального оборудования и программного обеспечения.Слайд 30http://library.krasu.ru/ft/ft/b72/0227142/pdf/6/13a.pdf

Расскажите о тенденции развития шин передачи данных

Что такое «Hub »

(см.Архитектура и основные параметры шины USB определяются возложенными на нее

задачами)Что такое «открытая архитектура»?

Слайд 31Общение программы с "внешним миром" на компьютере с общей шиной

(глазами системного программиста)

Слайд 32Центральный процессор может обмениваться с портами байтами или словами (в

зависимости от вида порта). Для записи значения в некоторый порт

используется машинная командаout op1,op2

Здесь операнд op1 определяет номер нужного порта и может иметь формат i8 (если номер порта небольшой и известен заранее) или быть регистром dx (если номер больше 255 или становится известным только в процессе счёта программы). Второй операнд op2 должен задаваться регистром al (если производится запись в порт байта) или ax (если производится запись в порт слова). При выполнении такой команды значение регистра (байт или слово) посылается по общей шине в соответствующий порт.

Для чтения данных в регистр из порта служит команда

in op1,op2

Здесь уже второй операнд op2 определяет номер нужного порта и может иметь, как и в предыдущей команде, формат i8 или быть регистром dx. Первый операнд op1 должен задаваться регистром al (если производится чтение из порта байта) или ax (если производится чтение слова). При выполнении этой команды значение (байт или слово) читается из заданного порта и по общей шине по-ступает в центральный процессор на указанный регистр. Итак, на нашем компьютере есть только очень простые команды для обмена байтом или словом между регистром центрального процессора и портом внешнего устройства. Почему же в архитектуре нашего компьютера команды ввода/вывода такие примитивные и неудобные для программиста? Ответ на этот вопрос легко понять, если вспомнить, что общая шина связывает между собой очень разные устройства, для которых было необходимо найти общий и приемлемый для всех их формат передаваемых данных. Ясно, что таким форматом может быть только один байт или одно слово – те минимальные порции данных, с которыми оперирует наш центральный процессор. Вот и приходится, например, для ввода целого числа с помощью команд in и out выполнять достаточно сложную программу

Слайд 33Программный ввод-вывод

.

В этом случае всю работу выполняет центральный процессор.

Рассмотрим процесс

печати строки ABCDEFGH этим способом.

Этапы печати строки ABCDEFGH

Алгоритм печати:

Строка

для печати собирается в пространстве пользователя.Обращаясь к системному вызову, процесс получает принтер.

Обращаясь к системному вызову, процесс просит распечатать строку на принтере.

Операционная система копирует строку в массив, расположенный в режиме ядра.

ОС копирует первый символ в регистр данных принтера, который отображен на памяти.

Символ печатается на бумаге.

Указатель устанавливается на следующий символ.

Процессор ждет, когда бит готовности принтера выставится в готовность.

Все повторяется.

При использовании буфера принтера, сначала вся строка копируется в буфер, после этого начинается печать

Слайд 46

Главная задача компьютерной системы – выполнять программы. Программы вместе с

данными, к которым они имеют доступ, в процессе выполнения должны

(по крайней мере частично) находиться в оперативной памяти. Операционной системе приходится решать задачу распределения памяти между пользовательскими процессами и компонентами ОС. Эта деятельность называется управлением памятью. Таким образом, память (storage, memory) является важнейшим ресурсом, требующим тщательного управления. В недавнем прошлом память была самым дорогим ресурсом.Часть ОС, которая отвечает за управление памятью, называется менеджером памяти.

Слайд 47Память - совокупность отдельных устройств, которые запоминают, хранят, выдают информацию.

Отдельные

устройства памяти называют запоминающими устройствами. Производительность вычислительных систем в значительной

мере определяется составом и характеристиками отдельных запоминающих устройств, которые различают по принципу действия, техническим характеристикам, назначениям. Основные операции с памятью - процедура записи, процедура чтения (выборки). Процедуры записи и чтения также называют обращением к памяти. За одно обращение к памяти «обрабатывается» для различных устройств различные единицы данных (байт, слово, двойное слово, блок). Основные технические характеристики памяти - емкость (Е), быстродействие (время обращения к запоминающему устройству).Слайд 48В некоторых запоминающих устройствах считывание данных сопровождается их разрушением. В

этом случае цикл обращения к памяти всегда должен содержать регенерацию

данных (ЗУ динамического типа). Этот цикл состоит из трех шагов:время от начала операции обращения до того момента, как данные станут доступны(время доступа)

считывание

3)регенерация Процедура записи:

Время доступа

Время подготовки (приведение в исходное состояние поверхности магнитного диска при записи)

Запись

Слайд 49Запоминающие устройства с произвольным доступом. Цикл обращения таких устройств не

зависит от того, в каком физическом месте ЗУ находятся требуемые

данные. Такой способ доступа характерен для полупроводниковых ЗУ. Число записанных одновременно битов данных за одно обращение называют шириной выборки (доступа). Запоминающие устройства с прямым доступом. В таких устройствах носитель информации непрерывно вращается. В результате требуемые данные доступны для чтения-записи через некоторый фиксированный промежуток времени. Такие ЗУ называют ЗУ циклического типа. Запоминающие устройства с последовательным доступом. При последовательном доступе, прежде чем найти нужный участок ЗУ, нужно «просмотреть» либо все предыдущие участки памяти, либо предыдущий последовательно один за другим (накопитель на магнитной ленте). Требования, которые предъявляются к емкости и быстродействию памяти, являются противоположными с точки зрения технического исполнения (т.е. если память быстрая, то емкость мала и наоборот). Поэтому в современных ЭВМ память строится в виде некоторой иерархической структуры. На разных уровнях иерархии распределяются ЗУ, которые обладают разными характеристиками.Слайд 51Параллельность работы и иерархия памяти

Быстродействие компьютерной системы в целом существенно

зависит от объема оперативной памяти и частоты, на которой она

способна работать без сбоев. Интересно заметить, что первый фактор намного важнее второго. Чем больше памяти, тем больше данных в ней можно хранить одновременно и тем реже требуется подгружать их с более медленных носителей, таких как жесткие диски, диски DVD, CD-ROM и другие.Есть 2 идеи, позволяющие строить компьютеры с памятью большей ёмкости, по быстродействию близкой к самым дорогим образцам и с умеренной стоимостью. Первая – построение памяти с иерархической структурой, вторая – исключение простоев центрального процессора за счёт организации параллельных действий различных устройств.

Слайд 52Регистры – самая быстрая память. В регистрах располагаются наиболее часто

используемые данные. Команды располагаться в них не могут.

Размеры кэш-памяти –

от нескольких килобайт до нескольких мегабайт. Кэш-память – скрытая память. В ней как команды, так и данные.Существует 2 или 3 уровня кэшей.

Основная память, «оперативная» -- от1-2 гбайт.

В основании – вторичная память.

Эффективность иерархической организации памяти связана с пространственной и временной локальностью данных и команд.

Слайд 55Идея использования иерархичечской памяти

Пусть в среднем каждый байт вызывается N

раз. Пусть время выборки из памяти нижнего уровня – T,

а из верхнего – t. Среднее время τ=t+T/Nt

T

Слайд 56Четыре верхних уровня иерархии образуют внутреннюю память ВМ, а все

нижние уровни — это внешняя или вторичная память. По мере

движения вниз по иерархической структуре:1.Уменьшается соотношение «стоимость/бит».

2.Возрастает емкость.

3.Растет время доступа.

4.Уменьшается частота обращения к памяти со стороны центрального процессора.

Вывод: иерархическая организация памяти ведет к уменьшению общей стоимости при заданном уровне производительности.

Слайд 57На каждом уровне иерархии информация разбивается на блоки, выступающие в

качестве наименьшей информационной единицы, пересылаемой между двумя соседними уровнями иерархии.

Размер блоков может быть фиксированным либо переменным. При фиксированном размере блока емкость памяти обычно кратна его размеру. Размер блоков на каждом уровне иерархии чаще всего различен и увеличивается от верхних уровней книжним.

При доступе к командам и данным, например, для их считывания, сначала производится поиск в памяти верхнего уровня. Факт обнаружения нужной информации называют попаданием (hit), в противном случае говорят о промахе (miss). При промахе производится поиск в ЗУ следующего более низкого уровня, где также возможны попадание или промах. После обнаружении необходимой информации выполняется последовательная пересылка блока, содержащего искомую информацию, с нижних уровней на верхние. Следует отметить, что независимо от числа уровней иерархии пересылка информации может осуществляться только между двумя соседними уровнями.

Слайд 58Параллельность работы. Идея

Параллельная работа разных уровней памяти, устройств ввода.вывода обеспечивается

комплексом программных и аппаратных средств.

Буфер – это запоминающее устройство небольшой

ёмкости.(принцип FIFO)Контроллер – специализированный процессор.

Слайд 59Буфер и Кэш

Эти термины не являются взаимоисключающими, и их

функции часто смешиваются, но существует различие в их предназначении. Буфер

— временное хранилище, где большие блоки данных сливаются или разбиваются на части. Это необходимо для взаимодействия с запоминающим устройством, которое работает с большими блоками данных, или когда данные передаются в другом порядке чем тот, в котором они формируются, и лишь желательно — в том случае, когда использование мелких блоков неэффективно. Использование буфера приносит пользу, даже если буферизуемые данные пишутся в буфер и читаются из него однократно.В свою очередь, использование Кэша предполагает, что данные будут читаться из кэша чаще, чем записываться туда. Его назначение — уменьшить число обращений к запоминающему устройству, а не сделать их более эффективными.

Слайд 60Основная память удовлетворяет запросы кэш-памяти и служит в качестве интерфейса

ввода/вывода, поскольку является местом назначения для ввода и источником для

вывода.Основная память современных компьютеров реализуется на микросхемах статических и динамических ЗУПВ (Запоминающее Устройство с Произвольной Выборкой). Микросхемы статических ЗУПВ (СЗУПВ) имеют меньшее время доступа и не требуют циклов регенерации. Микросхемы динамических ЗУПВ (ДЗУПВ) характеризуются большей емкостью и меньшей

Слайд 63Итак, напомним, что вся современная оперативная память относится к синхронной

динамической памяти с произвольным доступом (Synchronous Dynamic Random Access Memory,

SDRAM). Под синхронностью в данном случае понимают тот факт, что все управляющие сигналы и сами данные на шине памяти синхронизированы с некоторой опорной частотой (тактирующими импульсами). Динамической память является в том смысле, что информация в ней сохраняется только при включенном питании, а кроме того, содержимое этой памяти (в отличие от статической памяти) необходимо периодически обновлять (производить регенерацию памяти).Ядро микросхемы SDRAM-памяти принято рассматривать как некий двумерный массив (матрицу) ячеек памяти, находящихся на пересечении строк (Row) и столбцов (Column) (столбцы матрицы памяти также иногда называют страницами (Page)). По сути, ячейки памяти подсоединены к линиям строк и линиям столбцов

Слайд 64На элементарном уровне запоминающая ячейка SDRAM-памяти, способная запомнить 1 бит

информации, представляет собой конденсатор, который выполняет функцию хранителя заряда. Наличие

заряда на конденсаторе можно ассоциировать с единичным битом информации, а его отсутствие — с нулевым битом.Однако одного лишь конденсатора недостаточно для формирования ячейки памяти. Дело в том, что если конденсатор соединить с линией строк и линией столбцов, то он мгновенно разрядится, то есть не сможет сохранять информацию. Поэтому в паре с конденсатором в элементарной ячейке памяти применяется транзистор, выполняющий функцию электронного ключа. Затвор транзистора (управляющий электрод) подключается к линии строк, а остальные два электрода (сток и исток) подключены к одной из обкладок конденсатора и линии столбцов. Если на затвор транзистора не подается напряжение, то транзистор находится в запертом состоянии и конденсатор физически отсоединен от линии столбцов.

Слайд 66На системной плате и платах памяти их компоненты (DIP, SIMM,

SIPP) организуются в банки. Важно представлять себе распределение памяти между

банками и их расположение на плате, например, в том случае, если вы соберетесь устанавливать в свой компьютер дополнительное ОЗУ. Кроме того, диагностические программы выводят адреса байта и бита дефектной ячейки, и по этим данным вам придется определять неисправный банк памяти.http://www.xpvista7.ru/hard/index.php?id=ram_1

Слайд 72Концепция виртуальной памяти

В любой момент времени компьютер выполняет множество процессов

или задач, каждая из которых располагает своим адресным пространством. Было

бы слишком накладно отдавать всю физическую память какой-то одной задаче тем более, что многие задачи реально используют только небольшую часть своего адресного пространства. Поэтому необходим механизм разделения небольшой физической памяти между различными задачами. Виртуальная память является одним из способов реализации такой возможности. Она делит физическую память на блоки и распределяет их между различными задачами. При этом она предусматривает также некоторую схему защиты, которая ограничивает задачу теми блоками, которые ей принадлежат. Большинство типов виртуальной памяти сокращают также время начального запуска программы на процессоре, поскольку не весь программный код и данные требуются ей в физической памяти, чтобы начать выполнение.Другой вопрос, тесно связанный с реализацией концепции виртуальной памяти, касается организации вычислений на компьютере задач очень большого объема. Если программа становилась слишком большой для физической памяти, часть ее необходимо было хранить во внешней памяти (на диске) и задача приспособить ее для решения на компьютере ложилась на программиста. Программисты делили программы на части и затем определяли те из них, которые можно было бы выполнять независимо, организуя оверлейные структуры, которые загружались в основную память и выгружались из нее под управлением программы пользователя. Программист должен был следить за тем, чтобы программа не обращалась вне отведенного ей пространства физической памяти. Виртуальная память освободила программистов от этого бремени. Она автоматически управляет двумя уровнями иерархии памяти: основной памятью и внешней (дисковой) памятью.

Кроме того, виртуальная память упрощает также загрузку программ, обеспечивая механизм автоматического перемещения программ, позволяющий выполнять одну и ту же программу в произвольном месте физической памяти.

Системы виртуальной памяти можно разделить на два класса: системы с фиксированным размером блоков, называемых страницами, и системы с переменным размером блоков, называемых сегментами.

Слайд 73Нумерация справа налево

Нумерация слева направо

(прямой порядок)

Попробуем представить как будет храниться

фраза “школа номер 495” в памяти.

При этом пусть число 495

представлено в виде int:(00000000 00000000 00000001 11101111)

Слайд 74Проблема

Если мы попробуем скопировать такие данные по одному байту с

одной машины на другую, то вместо номера 495 получится номер

4009820160(11101111 00000001 00000000 00000000). Простого решения у этой проблемы не существует!

Слайд 75Ошибки

Память компьютера время от времени может делать ошибки из-за всплесков

напряжения на линии электропередачи или по другим причинам. Для борьбы

с такими ошибками используются коды с обнаружением и исправлением ошибок. При этом к каждому слову в памяти особым образом добавляются дополнительные биты. Когда слово считывается из памяти, эти биты проверяются на наличие ошибок.Слайд 76Допустим, что слово состоит из m бит данных, к которым

мы добавляем r бит контрольных разрядов. Тогда единицу размером n

бит (n = m + r), содержащую m бит данных и r бит контрольных разрядов, будем называть кодированным словом.Для любых двух слов можно определить, сколько соответствующих битов в них различается. Для этого применяется операция XOR и считается кол-во единиц в результате.

Число битовых позиций по которым различаются два слова называется интервалом Хэмминга.

Слайд 77Смысл интервала Хэмминга

Если интервал Хэмминга для двух слов равен d,

это значит, что достаточно d битовых ошибок, чтобы превратить одно

слово в другое.Пример:

11110001

XOR

00110000 = 11000001 => d = 3

Слайд 78Интервал Хэмминга полного кода

Для памяти из m-битных слов существует 2m

вариантов сочетания битов. Кодированные слова состоят из n битов, но

из-за способа подсчета контрольных разрядов допустимы только 2m из 2n комбинаций. Если получилось значение с недопустимой комбинацией контрольных разрядов, то сразу известно, что произошла ошибка.Зная алгоритм подсчета контрольных разрядов, мы можем найти все возможные комбинации кодированных слов и вычислить для них минимальный интервал Хэмминга. Т.е. выбрать минимум из всех интервалов Хэмминга для каждой пары кодированных слов. Этот интервал назовем интервалом Хэмминга полного кода.

Слайд 79Смысл интервала Хэмминга полного кода

От этой величины зависят свойства проверки

и исправления ошибок кода.

Чтобы обнаружить d ошибок в битах

необходим код с интервалом Хэмминга d + 1 (так как d ошибок не смогут изменить одно допустимое слово на другое). Соответственно, чтобы исправить d ошибок надо чтобы интервал Хэмминга кода был 2d + 1 (так как даже при d изменениях кодированное слово будет ближе к изначальному, чем к какому-либо другому слову).

Слайд 80Примеры

Пример 1: код с битом четности.

Пример 2: код с четырьмя

возможными значениями.

0000000000

0000011111

1111100000

1111111111

d = 2 => можем обнаружить одиночную ошибку

d

= 5 => можем обнаружить до 4-х ошибок и исправить две.Слайд 81Алгоритм для обнаружения и исправления одиночной ошибки

Попробуем придумать алгоритм для

обнаружения и исправления одиночной ошибки в произвольном коде при параметрах

n = m + r.Для каждого из 2m допустимых значений кода есть n возможных одиночных ошибок => n + 1 сочетание на слово.

(n + 1)*2m должно быть ≤ 2n (чтобы каждая ошибка была уникальной комбинацией и мы могли бы разгадать ее изначальное представление)

=>

(m+r+1) ≤ 2r.

Таким образом мы получаем нижний предел числа контрольных разрядов.