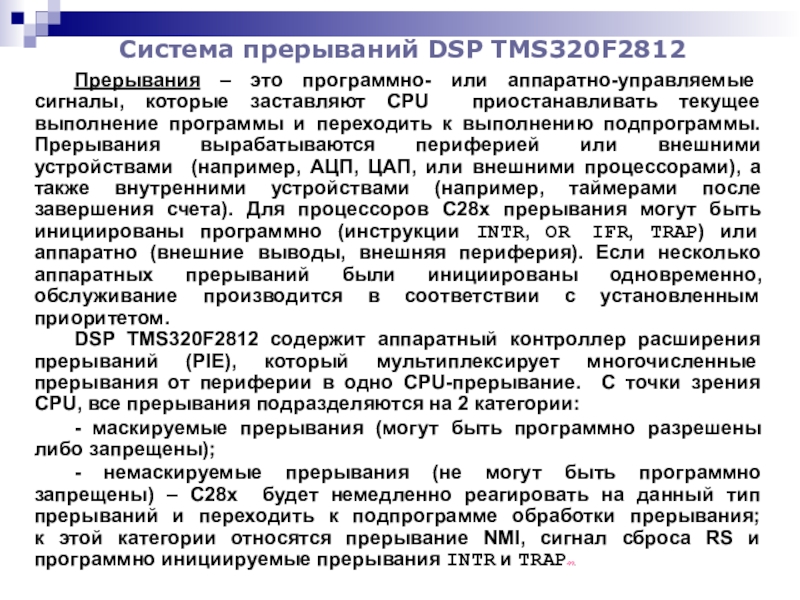

Слайд 1Система прерываний DSP TMS320F2812

Прерывания – это программно- или аппаратно-управляемые

сигналы, которые заставляют CPU приостанавливать текущее выполнение программы и переходить

к выполнению подпрограммы. Прерывания вырабатываются периферией или внешними устройствами (например, АЦП, ЦАП, или внешними процессорами), а также внутренними устройствами (например, таймерами после завершения счета). Для процессоров C28x прерывания могут быть инициированы программно (инструкции INTR, OR IFR, TRAP) или аппаратно (внешние выводы, внешняя периферия). Если несколько аппаратных прерываний были инициированы одновременно, обслуживание производится в соответствии с установленным приоритетом.

DSP TMS320F2812 содержит аппаратный контроллер расширения прерываний (PIE), который мультиплексирует многочисленные прерывания от периферии в одно CPU-прерывание. С точки зрения CPU, все прерывания подразделяются на 2 категории:

- маскируемые прерывания (могут быть программно разрешены либо запрещены);

- немаскируемые прерывания (не могут быть программно запрещены) – C28x будет немедленно реагировать на данный тип прерываний и переходить к подпрограмме обработки прерывания;

к этой категории относятся прерывание NMI, сигнал сброса RS и программно инициируемые прерывания INTR и TRAP-??.

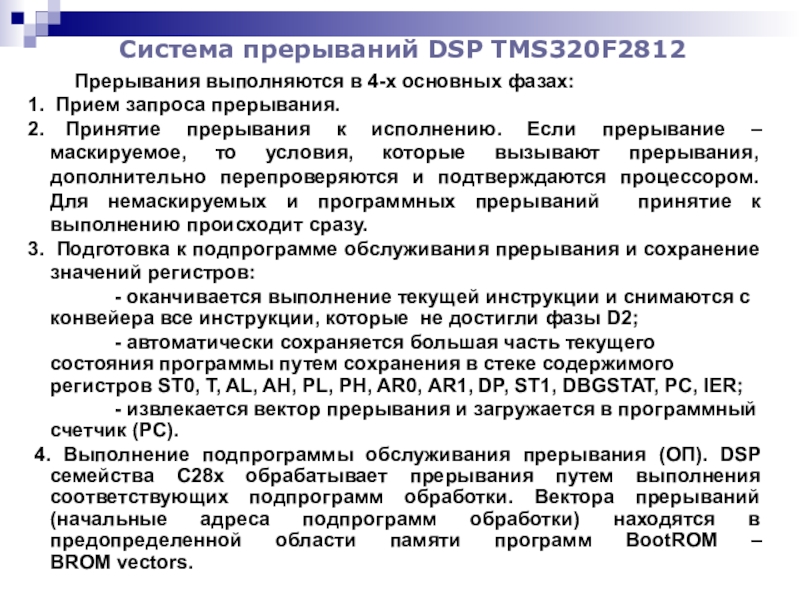

Слайд 2Система прерываний DSP TMS320F2812

Прерывания выполняются в 4-х основных фазах:

Прием запроса прерывания.

Принятие прерывания к исполнению. Если прерывание –

маскируемое, то условия, которые вызывают прерывания, дополнительно перепроверяются и подтверждаются процессором. Для немаскируемых и программных прерываний принятие к выполнению происходит сразу.

Подготовка к подпрограмме обслуживания прерывания и сохранение значений регистров:

- оканчивается выполнение текущей инструкции и снимаются с конвейера все инструкции, которые не достигли фазы D2;

- автоматически сохраняется большая часть текущего состояния программы путем сохранения в стеке содержимого регистров ST0, T, AL, AH, PL, PH, AR0, AR1, DP, ST1, DBGSTAT, PC, IER;

- извлекается вектор прерывания и загружается в программный счетчик (PC).

4. Выполнение подпрограммы обслуживания прерывания (ОП). DSP семейства C28x обрабатывает прерывания путем выполнения соответствующих подпрограмм обработки. Вектора прерываний (начальные адреса подпрограмм обработки) находятся в предопределенной области памяти программ BootROM –

BROM vectors.

Слайд 3Система прерываний DSP TMS320F2812

Слайд 4Система прерываний DSP TMS320F2812

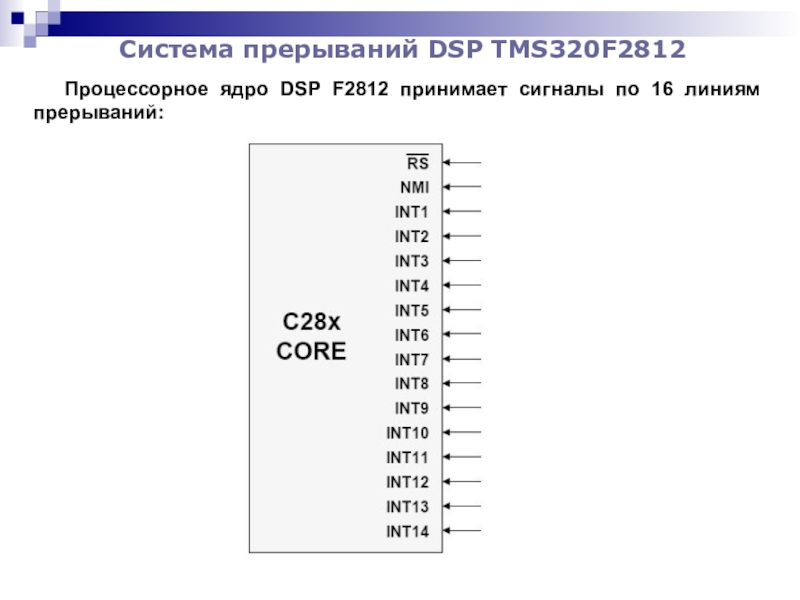

Процессорное ядро DSP F2812 принимает сигналы

по 16 линиям прерываний:

Слайд 5Система прерываний DSP TMS320F2812

Источники прерываний в DSP F2812:

Слайд 632-битные таймеры ядра ЦСП TMS320F28x

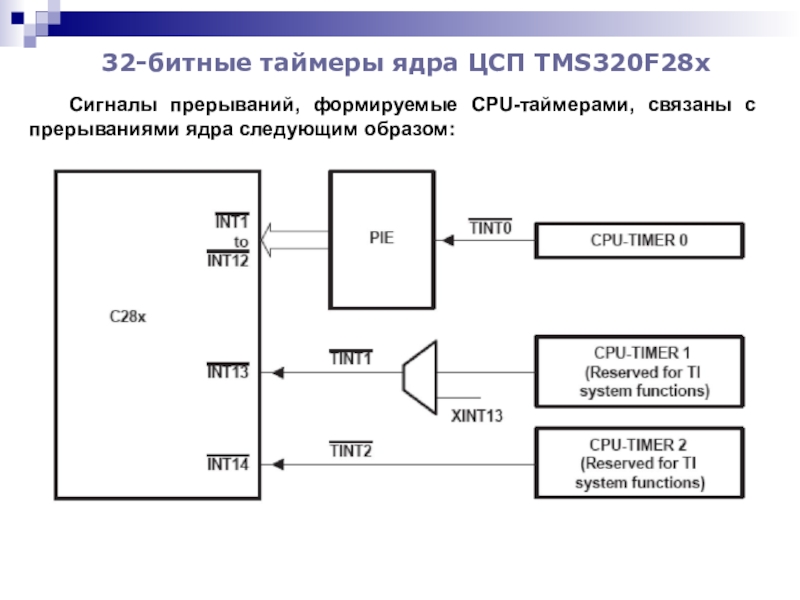

Сигналы прерываний, формируемые CPU-таймерами, связаны

с прерываниями ядра следующим образом:

Слайд 7Система прерываний DSP TMS320F2812

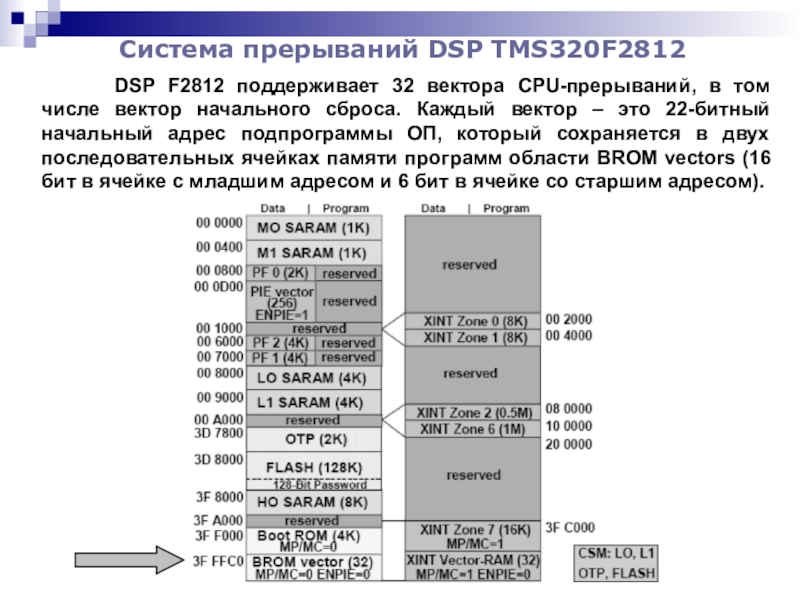

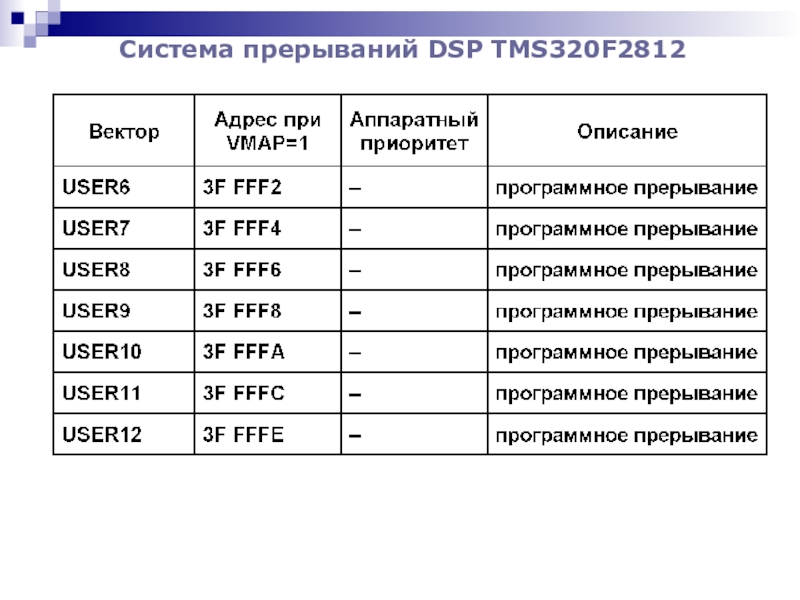

DSP F2812 поддерживает 32 вектора CPU-прерываний,

в том числе вектор начального сброса. Каждый вектор – это

22-битный начальный адрес подпрограммы ОП, который сохраняется в двух последовательных ячейках памяти программ области BROM vectors (16 бит в ячейке с младшим адресом и 6 бит в ячейке со старшим адресом).

Слайд 8Система прерываний DSP TMS320F2812

Слайд 9Система прерываний DSP TMS320F2812

Слайд 10Система прерываний DSP TMS320F2812

Слайд 11Система прерываний DSP TMS320F2812

Слайд 12Система прерываний DSP TMS320F2812

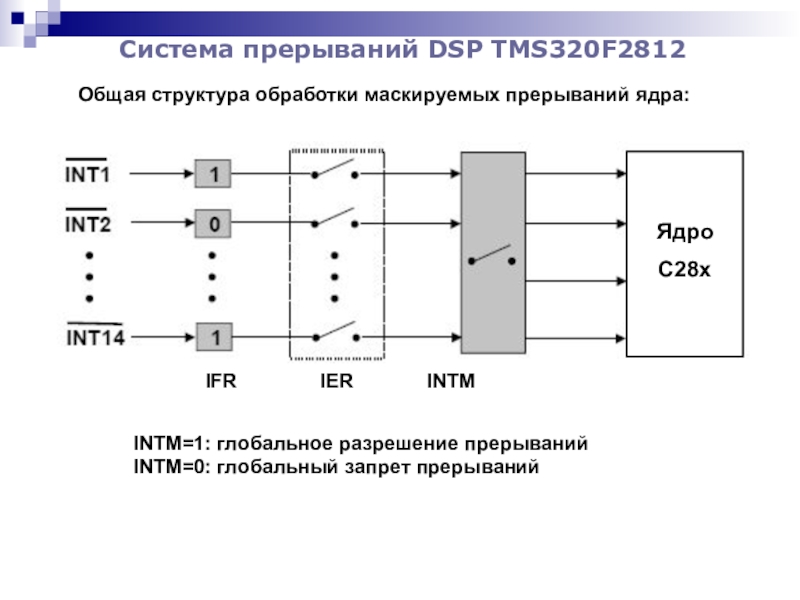

Общая структура обработки маскируемых прерываний

ядра:

INTM=1: глобальное разрешение прерываний

INTM=0: глобальный запрет прерываний

Слайд 13Система прерываний DSP TMS320F2812

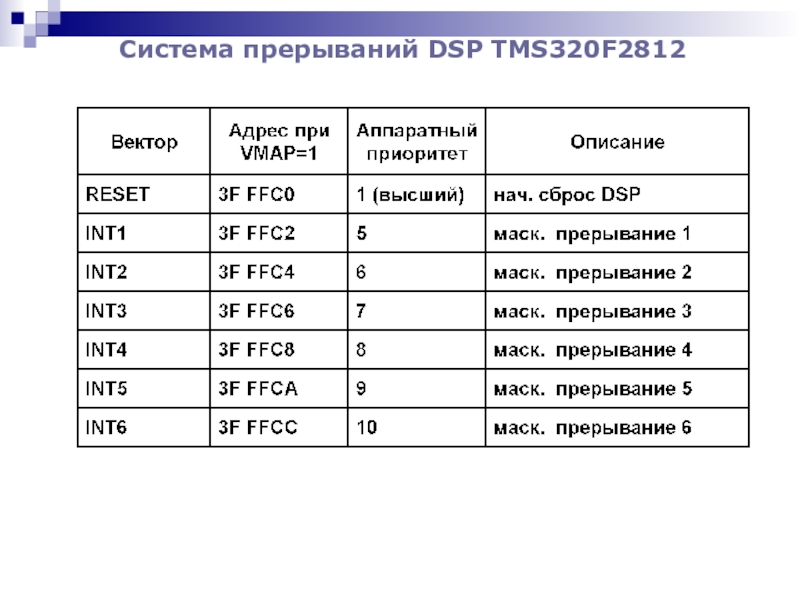

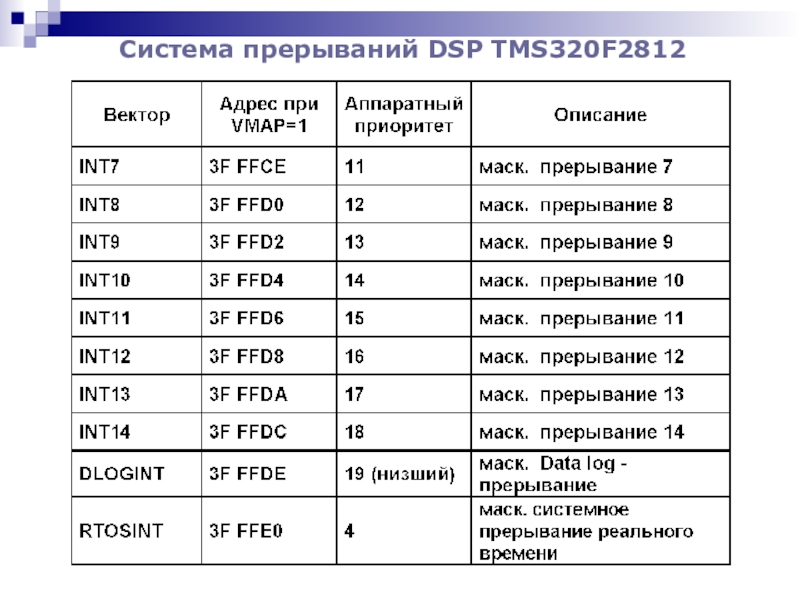

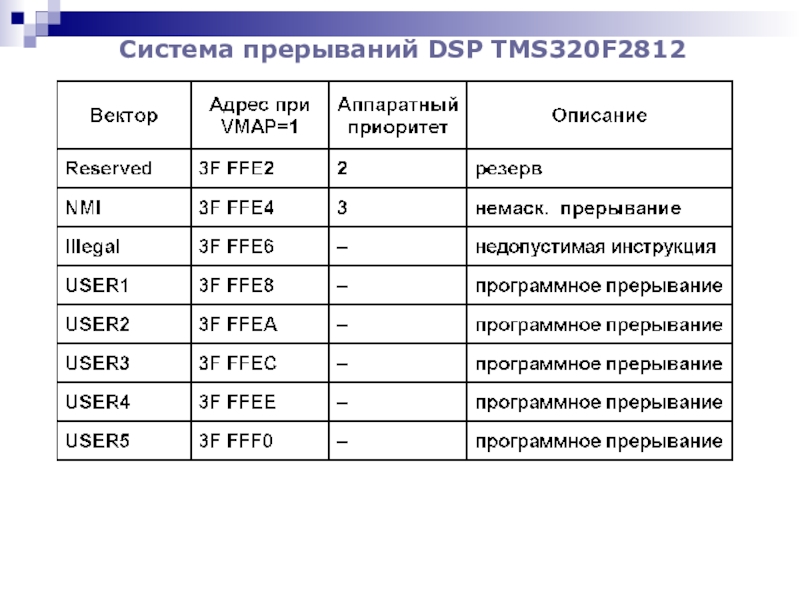

INT1… INT14 – 14 основных

прерываний. Прерывания DLOGINT и RTOSINT используются при эмуляции.

C28x имеет

три регистра, выделенных для управления прерываниями:

− регистр флагов прерываний (IFR);

− регистр разрешения прерываний (IER);

− регистр разрешения отладки прерываний (DBGIER).

16-битный регистр IFR содержит биты флагов для маскируемых прерываний (которые можно разрешать и запрещать программно).

Слайд 14Система прерываний DSP TMS320F2812

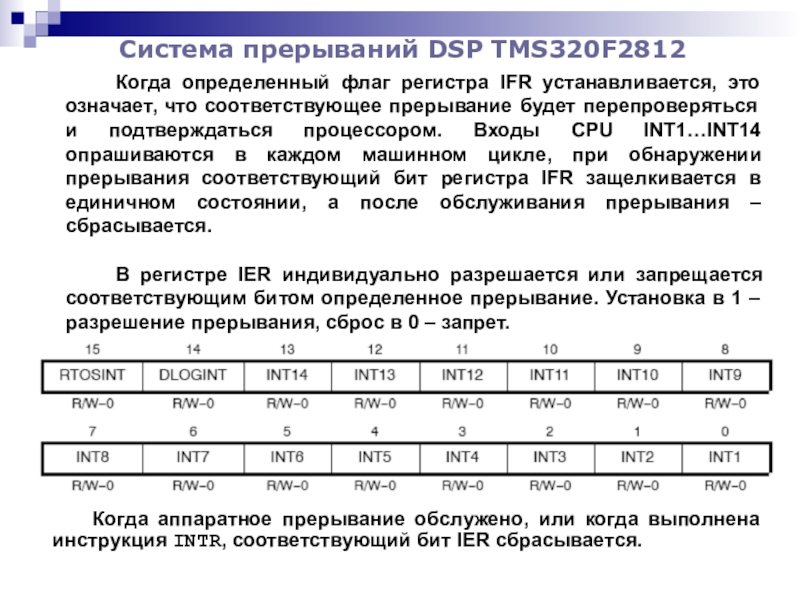

Когда определенный флаг регистра IFR устанавливается,

это означает, что соответствующее прерывание будет перепроверяться и подтверждаться процессором.

Входы CPU INT1…INT14 опрашиваются в каждом машинном цикле, при обнаружении прерывания соответствующий бит регистра IFR защелкивается в единичном состоянии, а после обслуживания прерывания – сбрасывается.

В регистре IER индивидуально разрешается или запрещается соответствующим битом определенное прерывание. Установка в 1 – разрешение прерывания, сброс в 0 – запрет.

Когда аппаратное прерывание обслужено, или когда выполнена инструкция INTR, соответствующий бит IER сбрасывается.

Слайд 15Система прерываний DSP TMS320F2812

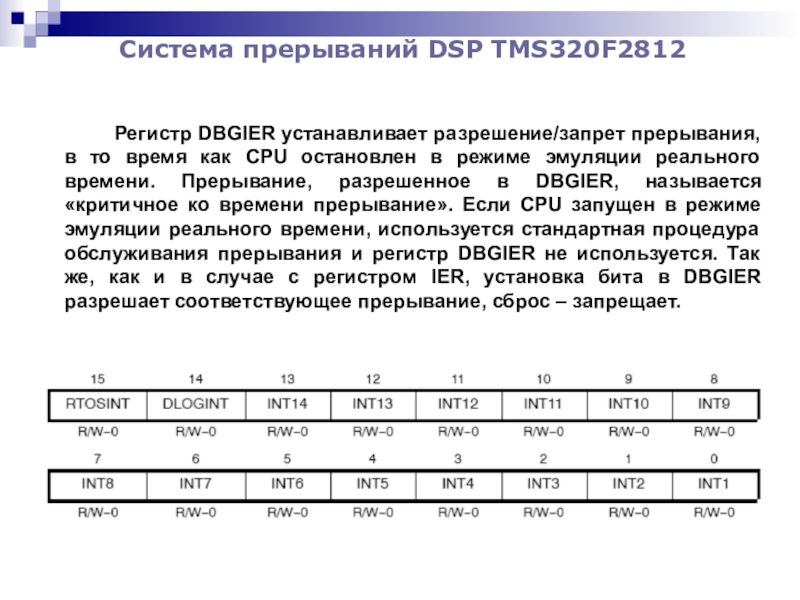

Регистр DBGIER устанавливает разрешение/запрет прерывания, в

то время как CPU остановлен в режиме эмуляции реального времени.

Прерывание, разрешенное в DBGIER, называется «критичное ко времени прерывание». Если CPU запущен в режиме эмуляции реального времени, используется стандартная процедура обслуживания прерывания и регистр DBGIER не используется. Так же, как и в случае с регистром IER, установка бита в DBGIER разрешает соответствующее прерывание, сброс – запрещает.

Слайд 16Система прерываний DSP TMS320F2812

Стандартная процедура выполнения маскируемого прерывания:

Слайд 17Система прерываний DSP TMS320F2812

В случае использования PIE-контроллера, таблица адресов

векторов прерываний расширяется. PIE-контроллер может поддерживать 96 прерываний, которые сгруппированы

в 12 групп по 8 прерываний.

Слайд 18Система прерываний DSP TMS320F2812

Таблица источников прерываний в PIE-контроллере:

Приоритет

Слайд 19Система прерываний DSP TMS320F2812

Каждая группа (строка из 8 элементов)

мультиплексируется в одно из прерываний ядра INT1…INT12:

Слайд 20Система прерываний DSP TMS320F2812

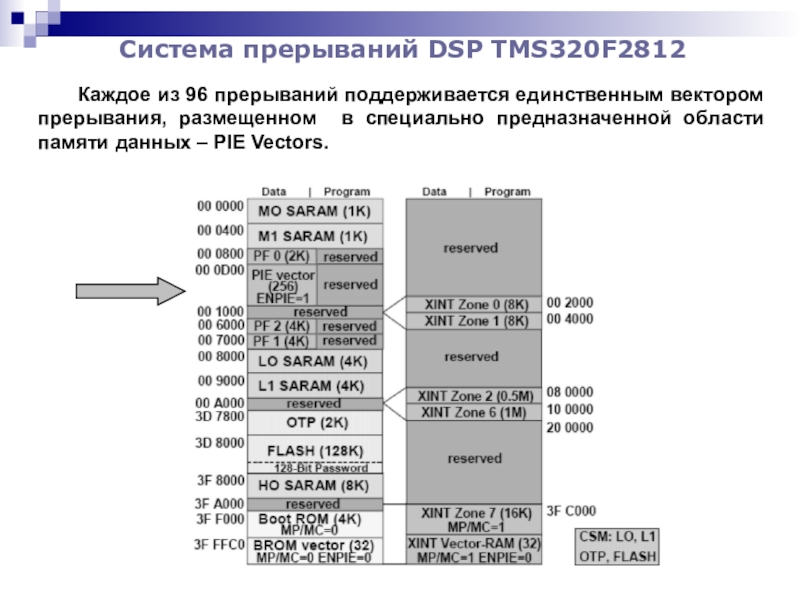

Каждое из 96 прерываний поддерживается единственным

вектором прерывания, размещенном в специально предназначенной области памяти данных –

PIE Vectors.

Слайд 21Система прерываний DSP TMS320F2812

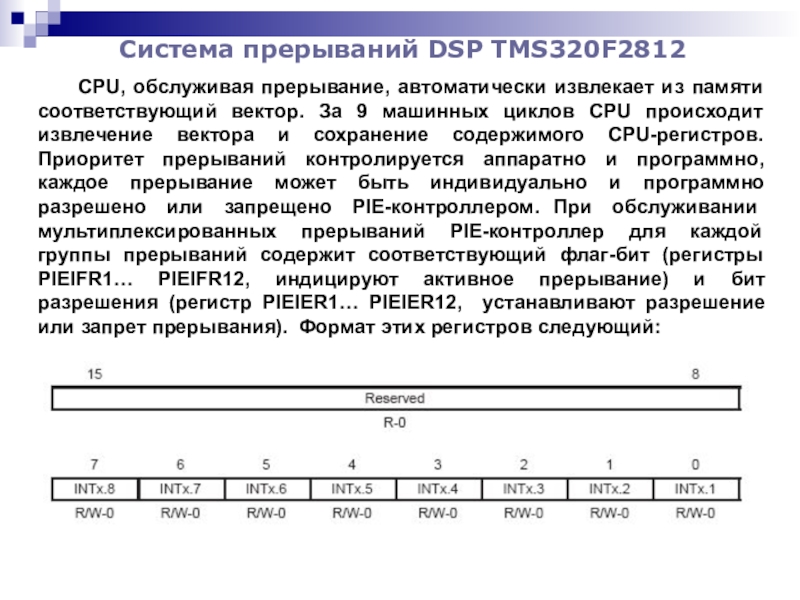

CPU, обслуживая прерывание, автоматически извлекает из

памяти соответствующий вектор. За 9 машинных циклов CPU происходит извлечение

вектора и сохранение содержимого CPU-регистров. Приоритет прерываний контролируется аппаратно и программно, каждое прерывание может быть индивидуально и программно разрешено или запрещено PIE-контроллером. При обслуживании мультиплексированных прерываний PIE-контроллер для каждой группы прерываний содержит соответствующий флаг-бит (регистры PIEIFR1… PIEIFR12, индицируют активное прерывание) и бит разрешения (регистр PIEIER1… PIEIER12, устанавливают разрешение или запрет прерывания). Формат этих регистров следующий:

Слайд 22Система прерываний DSP TMS320F2812

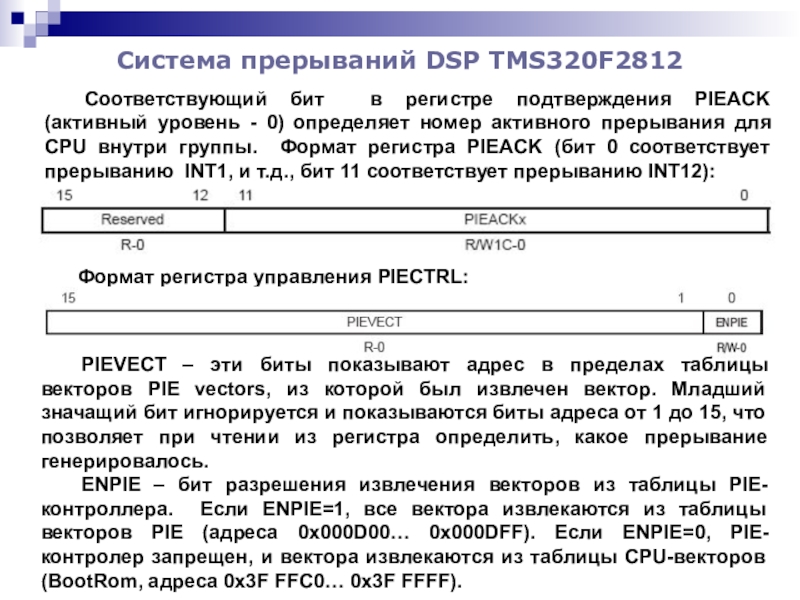

Соответствующий бит в регистре подтверждения PIEACK

(активный уровень - 0) определяет номер активного прерывания для CPU

внутри группы. Формат регистра PIEACK (бит 0 соответствует прерыванию INT1, и т.д., бит 11 соответствует прерыванию INT12):

Формат регистра управления PIECTRL:

PIEVECT – эти биты показывают адрес в пределах таблицы векторов PIE vectors, из которой был извлечен вектор. Младший значащий бит игнорируется и показываются биты адреса от 1 до 15, что позволяет при чтении из регистра определить, какое прерывание генерировалось.

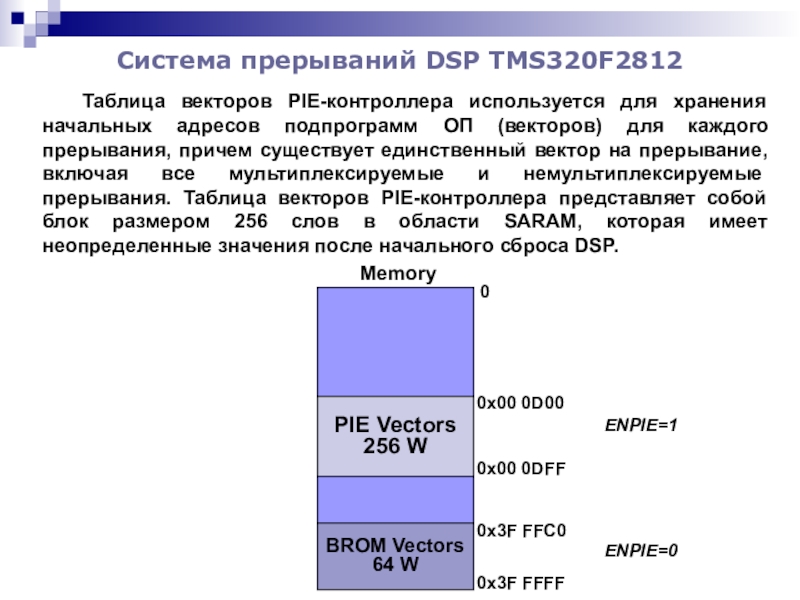

ENPIE – бит разрешения извлечения векторов из таблицы PIE-контроллера. Если ENPIE=1, все вектора извлекаются из таблицы векторов PIE (адреса 0x000D00… 0x000DFF). Если ENPIE=0, PIE-контролер запрещен, и вектора извлекаются из таблицы CPU-векторов (BootRom, адреса 0x3F FFC0… 0x3F FFFF).

Слайд 23Система прерываний DSP TMS320F2812

Слайд 24Система прерываний DSP TMS320F2812

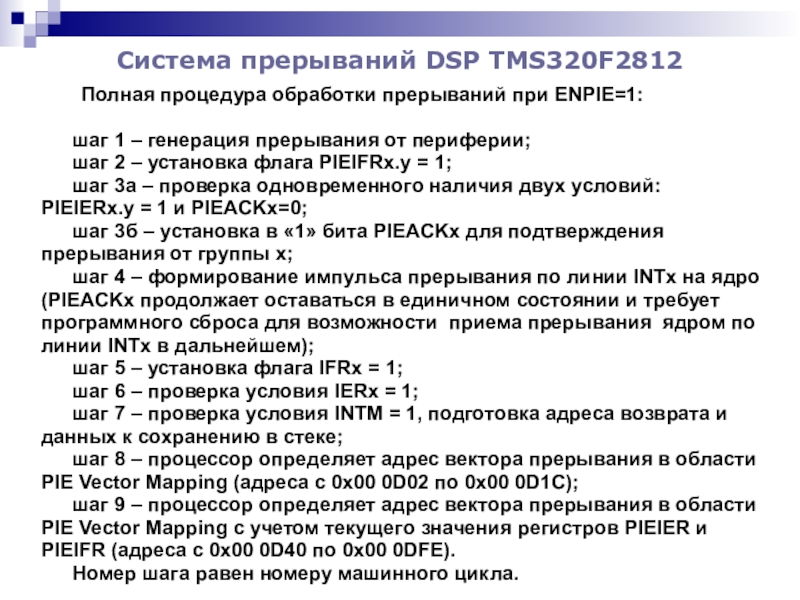

Полная процедура обработки прерываний при ENPIE=1:

шаг 1 – генерация прерывания от периферии;

шаг 2 –

установка флага PIEIFRx.y = 1;

шаг 3а – проверка одновременного наличия двух условий:

PIEIERx.y = 1 и PIEACKx=0;

шаг 3б – установка в «1» бита PIEACKx для подтверждения прерывания от группы x;

шаг 4 – формирование импульса прерывания по линии INTx на ядро (PIEACKx продолжает оставаться в единичном состоянии и требует программного сброса для возможности приема прерывания ядром по линии INTx в дальнейшем);

шаг 5 – установка флага IFRx = 1;

шаг 6 – проверка условия IERx = 1;

шаг 7 – проверка условия INTM = 1, подготовка адреса возврата и данных к сохранению в стеке;

шаг 8 – процессор определяет адрес вектора прерывания в области PIE Vector Mapping (адреса с 0x00 0D02 по 0x00 0D1C);

шаг 9 – процессор определяет адрес вектора прерывания в области PIE Vector Mapping с учетом текущего значения регистров PIEIER и PIEIFR (адреса с 0x00 0D40 по 0x00 0DFE).

Номер шага равен номеру машинного цикла.

Слайд 25Система прерываний DSP TMS320F2812

Таблица векторов PIE-контроллера используется для хранения

начальных адресов подпрограмм ОП (векторов) для каждого прерывания, причем существует

единственный вектор на прерывание, включая все мультиплексируемые и немультиплексируемые прерывания. Таблица векторов PIE-контроллера представляет собой блок размером 256 слов в области SARAM, которая имеет неопределенные значения после начального сброса DSP.

0x00 0D00

0x00 0DFF

Слайд 26Система прерываний DSP TMS320F2812

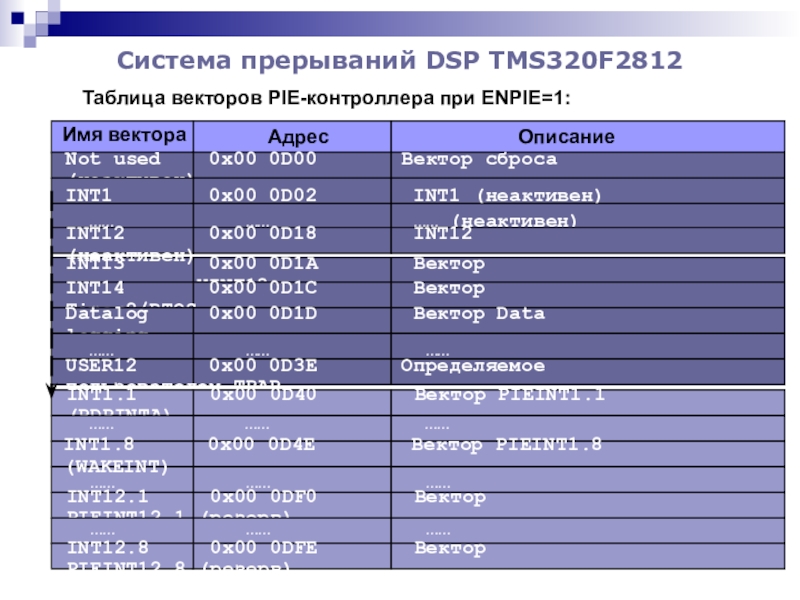

Таблица векторов PIE-контроллера при ENPIE=1: