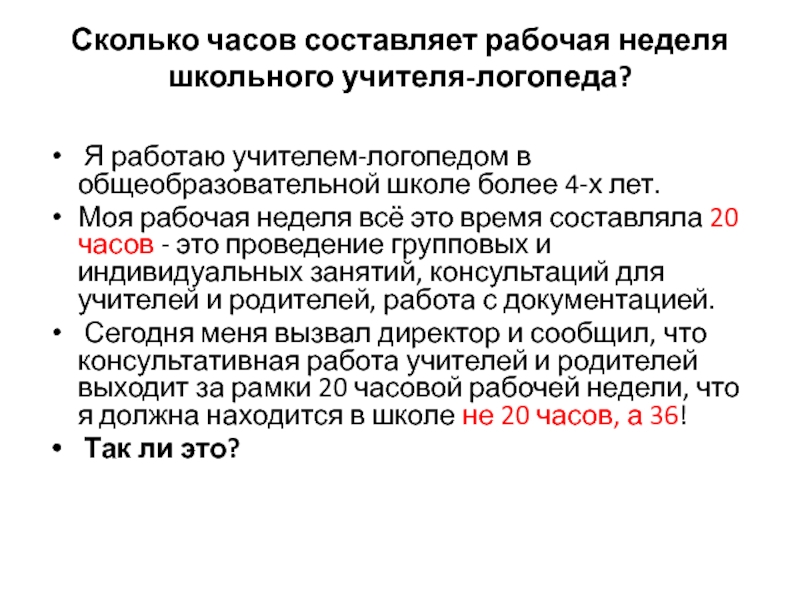

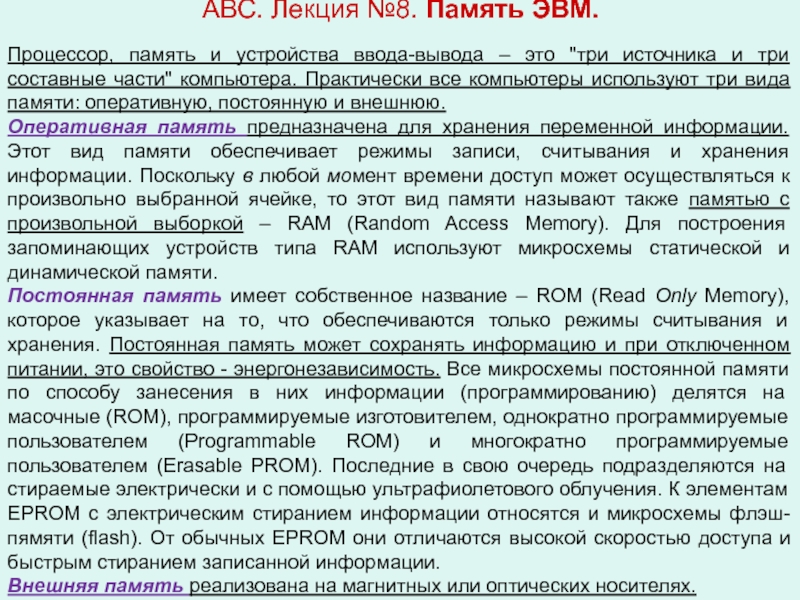

Слайд 1АВС. Лекция №8. Память ЭВМ.

Процессор, память и устройства ввода-вывода

– это "три источника и три составные части" компьютера. Практически

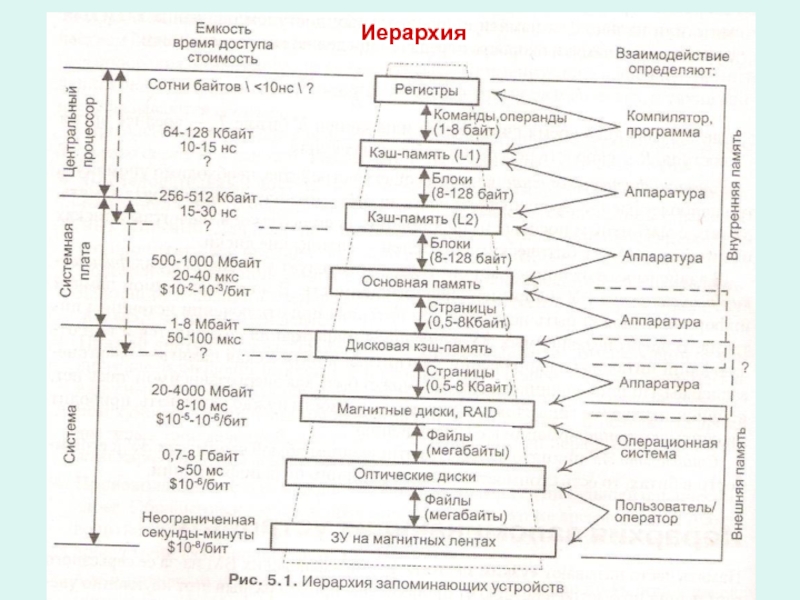

все компьютеры используют три вида памяти: оперативную, постоянную и внешнюю.

Оперативная память предназначена для хранения переменной информации. Этот вид памяти обеспечивает режимы записи, считывания и хранения информации. Поскольку в любой момент времени доступ может осуществляться к произвольно выбранной ячейке, то этот вид памяти называют также памятью с произвольной выборкой – RAM (Random Access Memory). Для построения запоминающих устройств типа RAM используют микросхемы статической и динамической памяти.

Постоянная память имеет собственное название – ROM (Read Only Memory), которое указывает на то, что обеспечиваются только режимы считывания и хранения. Постоянная память может сохранять информацию и при отключенном питании, это свойство - энергонезависимость. Все микросхемы постоянной памяти по способу занесения в них информации (программированию) делятся на масочные (ROM), программируемые изготовителем, однократно программируемые пользователем (Programmable ROM) и многократно программируемые пользователем (Erasable PROM). Последние в свою очередь подразделяются на стираемые электрически и с помощью ультрафиолетового облучения. К элементам EPROM с электрическим стиранием информации относятся и микросхемы флэш-пямяти (flash). От обычных EPROM они отличаются высокой скоростью доступа и быстрым стиранием записанной информации.

Внешняя память реализована на магнитных или оптических носителях.

Слайд 3 Оперативная память.

Если от типа процессора зависит количество адресуемой памяти,

то быстродействие используемой оперативной памяти в свою очередь во многом

определяет скорость работы процессора, а в конечном итоге влияет и на производительность всей системы.

Компьютер оснащен оперативной памятью, выполненной на микросхемах динамического типа (DRAM). Каждый бит такой памяти представляется в виде наличия (или отсутствия) заряда на конденсаторе, образованном в структуре полупроводникового кристалла.

Другой тип памяти – статический (SRAM, Static RAM) – в качестве элементарной ячейки памяти использует так называемый статический триггер. Если для реализации одного запоминающего элемента динамической памяти требуется 1 – 2 транзистора, то для статической их число возрастает до 4 – 6. Статический тип памяти обладает высоким быстродействием и, как правило, используется в самых "узких" местах системы, например для организации кэш памяти.

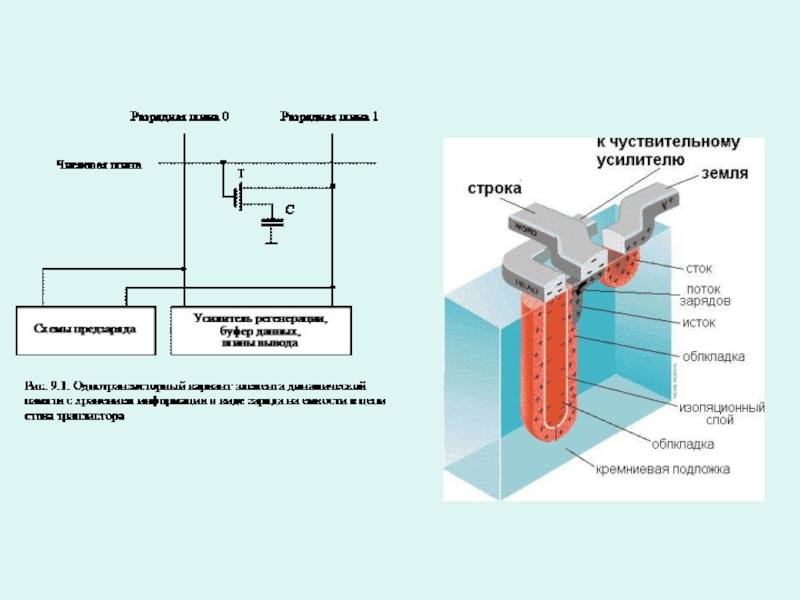

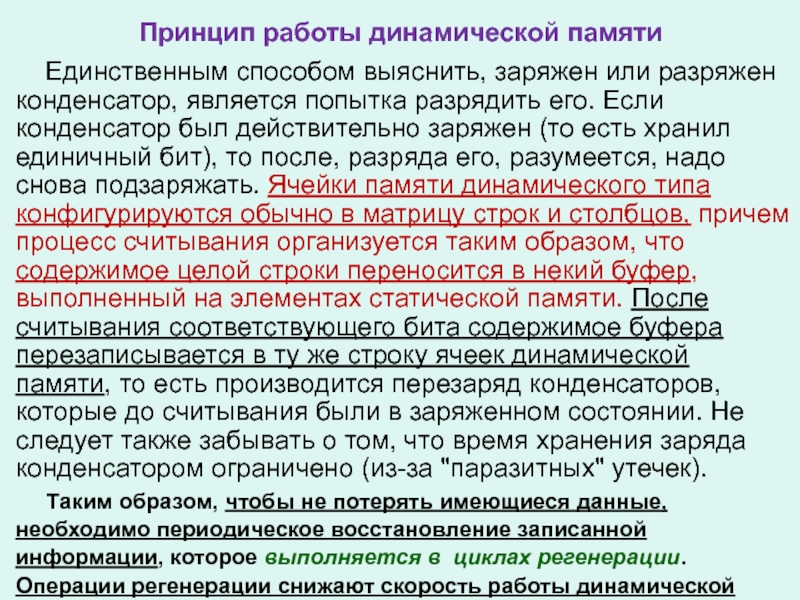

Слайд 4Принцип работы динамической памяти

Единственным способом выяснить, заряжен

или разряжен конденсатор, является попытка разрядить его. Если конденсатор был

действительно заряжен (то есть хранил единичный бит), то после, разряда его, разумеется, надо снова подзаряжать. Ячейки памяти динамического типа конфигурируются обычно в матрицу строк и столбцов, причем процесс считывания организуется таким образом, что содержимое целой строки переносится в некий буфер, выполненный на элементах статической памяти. После считывания соответствующего бита содержимое буфера перезаписывается в ту же строку ячеек динамической памяти, то есть производится перезаряд конденсаторов, которые до считывания были в заряженном состоянии. Не следует также забывать о том, что время хранения заряда конденсатором ограничено (из-за "паразитных" утечек).

Таким образом, чтобы не потерять имеющиеся данные, необходимо периодическое восстановление записанной информации, которое выполняется в циклах регенерации. Операции регенерации снижают скорость работы динамической памяти. Это является одним из основных недостатков динамической памяти, так как по критерию, учитывающему информационную емкость, стоимость и энергопотребление, этот тип памяти во многих случаях предпочтительнее статической.

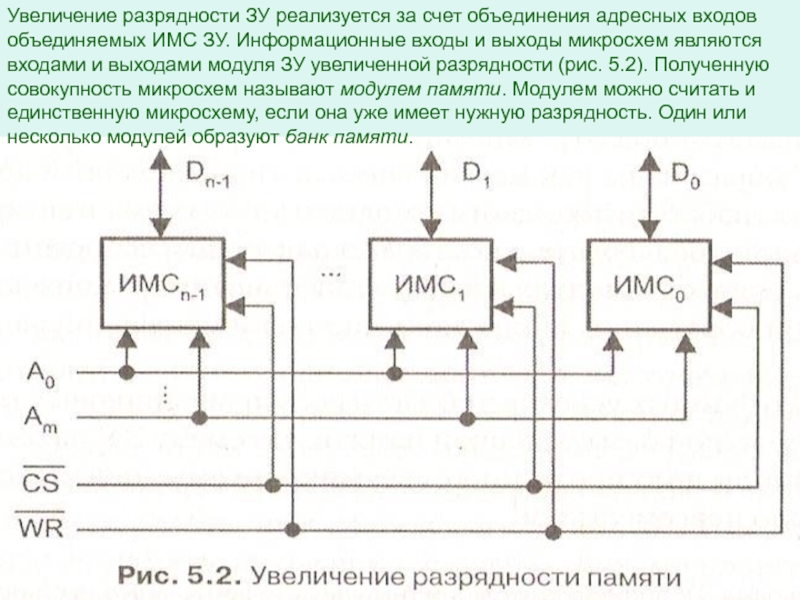

Слайд 6Увеличение разрядности ЗУ реализуется за счет объединения адресных входов объединяемых

ИМС ЗУ. Информационные входы и выходы микросхем являются входами и

выходами модуля ЗУ увеличенной разрядности (рис. 5.2). Полученную совокупность микросхем называют модулем памяти. Модулем можно считать и единственную микросхему, если она уже имеет нужную разрядность. Один или несколько модулей образуют банк памяти.

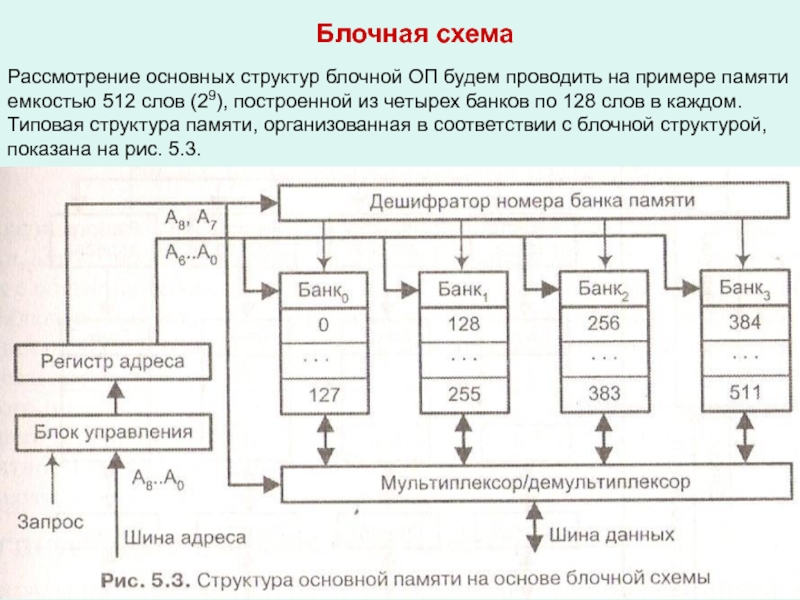

Слайд 7Рассмотрение основных структур блочной ОП будем проводить на примере памяти

емкостью 512 слов (29), построенной из четырех банков по 128

слов в каждом. Типовая структура памяти, организованная в соответствии с блочной структурой, показана на рис. 5.3.

Блочная схема

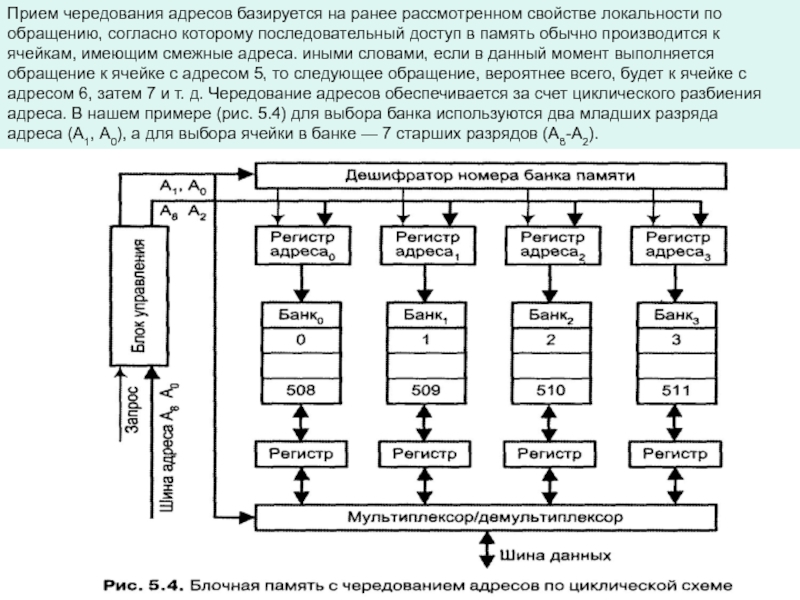

Слайд 8Прием чередования адресов базируется на ранее рассмотренном свойстве локальности по

обращению, согласно которому последовательный доступ в память обычно производится к

ячейкам, имеющим смежные адреса. иными словами, если в данный момент выполняется обращение к ячейке с адресом 5, то следующее обращение, вероятнее всего, будет к ячейке с адресом 6, затем 7 и т. д. Чередование адресов обеспечивается за счет циклического разбиения адреса. В нашем примере (рис. 5.4) для выбора банка используются два младших разряда адреса (А1, А0), а для выбора ячейки в банке — 7 старших разрядов (А8-А2).

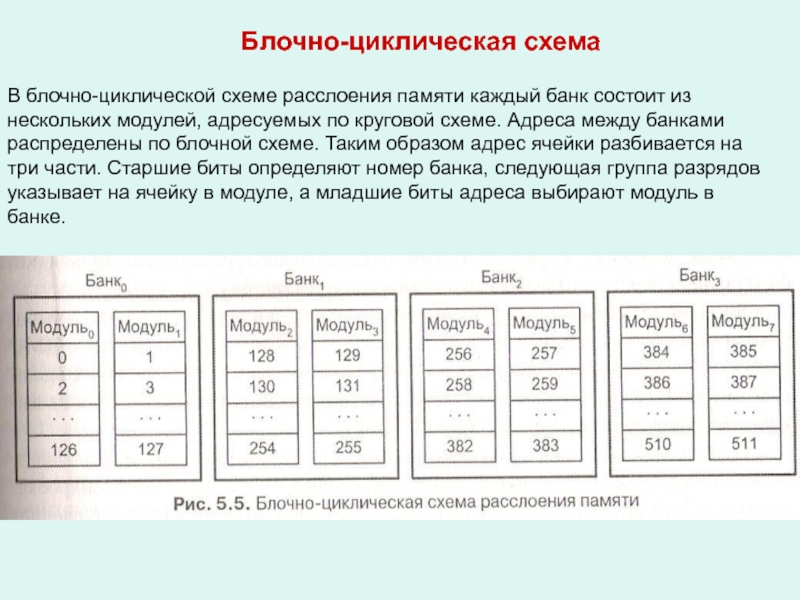

Слайд 9В блочно-циклической схеме расслоения памяти каждый банк состоит из нескольких

модулей, адресуемых по круговой схеме. Адреса между банками распределены по

блочной схеме. Таким образом адрес ячейки разбивается на три части. Старшие биты определяют номер банка, следующая группа разрядов указывает на ячейку в модуле, а младшие биты адреса выбирают модуль в банке.

Блочно-циклическая схема

Слайд 10Корпуса микросхем ОП.

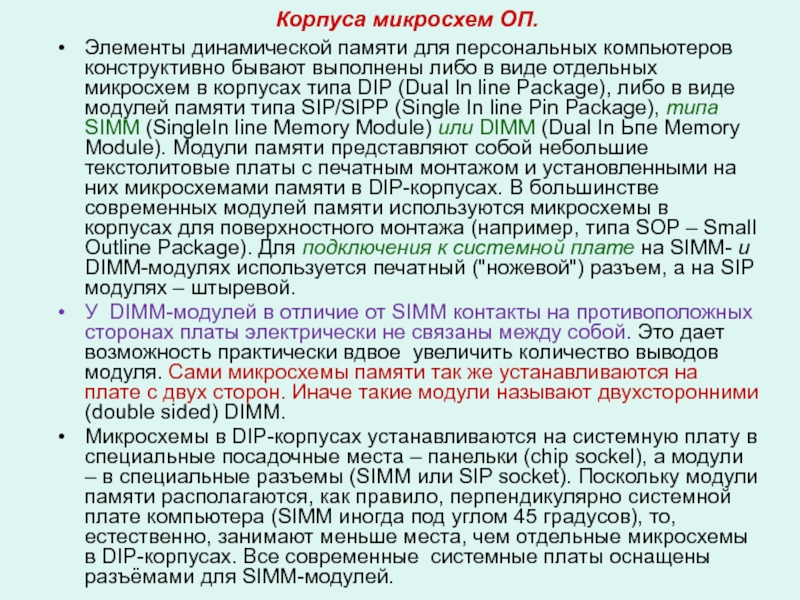

Элементы динамической памяти для персональных компьютеров конструктивно бывают

выполнены либо в виде отдельных микросхем в корпусах типа DIP

(Dual In line Package), либо в виде модулей памяти типа SIP/SIPP (Single In line Pin Package), типа SIMM (SingleIn line Memory Module) или DIMM (Dual In Ьпе Memory Module). Модули памяти представляют собой небольшие текстолитовые платы с печатным монтажом и установленными на них микросхемами памяти в DIP-корпусах. В большинстве современных модулей памяти используются микросхемы в корпусах для поверхностного монтажа (например, типа SOP – Small Outline Package). Для подключения к системной плате на SIMM- и DIMM-модулях используется печатный ("ножевой") разъем, а на SIP модулях – штыревой.

У DIMM-модулей в отличие от SIMM контакты на противоположных сторонах платы электрически не связаны между собой. Это дает возможность практически вдвое увеличить количество выводов модуля. Сами микросхемы памяти так же устанавливаются на плате с двух сторон. Иначе такие модули называют двухсторонними (double sided) DIMM.

Микросхемы в DIP-кopпycax устанавливаются на системную плату в специальные посадочные места – панельки (chip sockel), а модули – в специальные разъемы (SIMM или SIP socket). Поскольку модули памяти располагаются, как правило, перпендикулярно системной плате компьютера (SIMM иногда под углом 45 градусов), то, естественно, занимают меньше места, чем отдельные микросхемы в DIP-корпусах. Все современные системные платы оснащены разъёмами для SIMM-модулей.

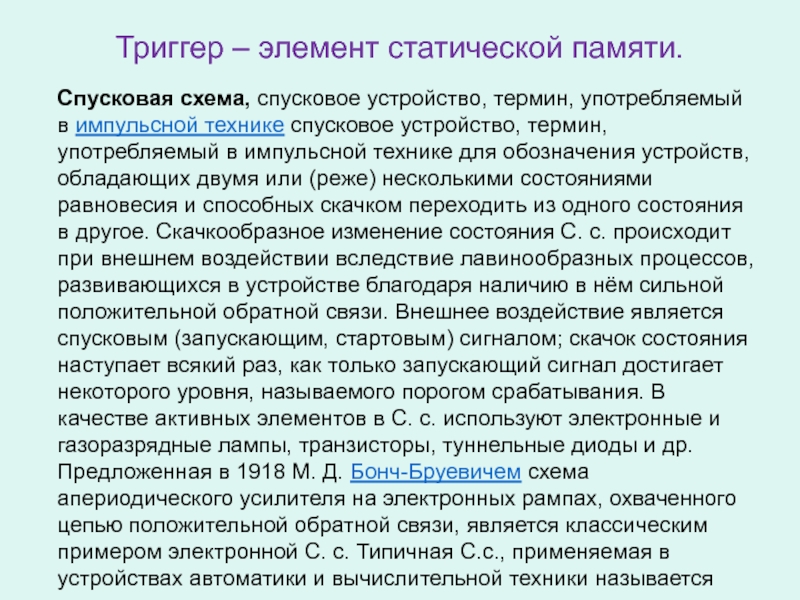

Слайд 12Триггер – элемент статической памяти.

Спусковая схема, спусковое устройство, термин, употребляемый

в импульсной технике спусковое устройство, термин, употребляемый в импульсной технике

для обозначения устройств, обладающих двумя или (реже) несколькими состояниями равновесия и способных скачком переходить из одного состояния в другое. Скачкообразное изменение состояния С. с. происходит при внешнем воздействии вследствие лавинообразных процессов, развивающихся в устройстве благодаря наличию в нём сильной положительной обратной связи. Внешнее воздействие является спусковым (запускающим, стартовым) сигналом; скачок состояния наступает всякий раз, как только запускающий сигнал достигает некоторого уровня, называемого порогом срабатывания. В качестве активных элементов в С. с. используют электронные и газоразрядные лампы, транзисторы, туннельные диоды и др. Предложенная в 1918 М. Д. Бонч-Бруевичем схема апериодического усилителя на электронных рампах, охваченного цепью положительной обратной связи, является классическим примером электронной С. с. Типичная С.с., применяемая в устройствах автоматики и вычислительной техники называется триггер.

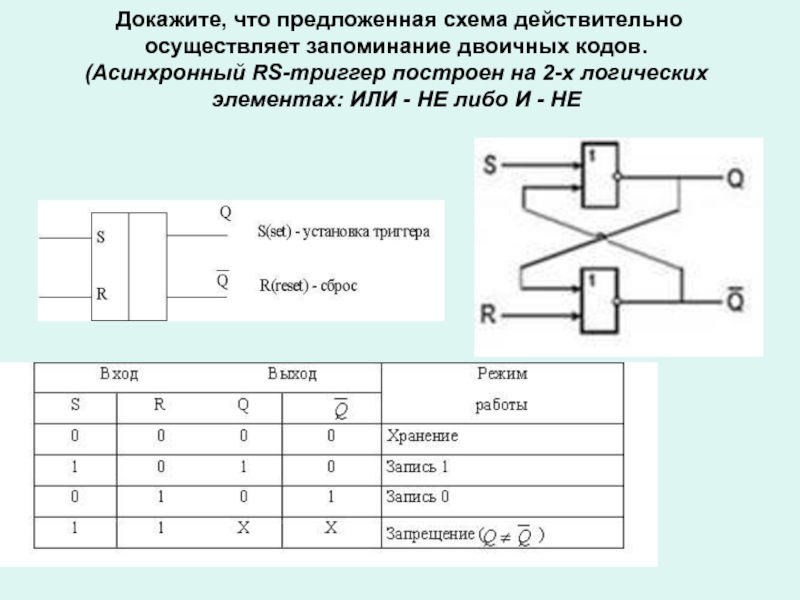

Слайд 13 Докажите, что предложенная схема действительно осуществляет запоминание двоичных кодов.

(Асинхронный

RS-триггер построен на 2-х логических элементах: ИЛИ - НЕ либо

И - НЕ

Слайд 15

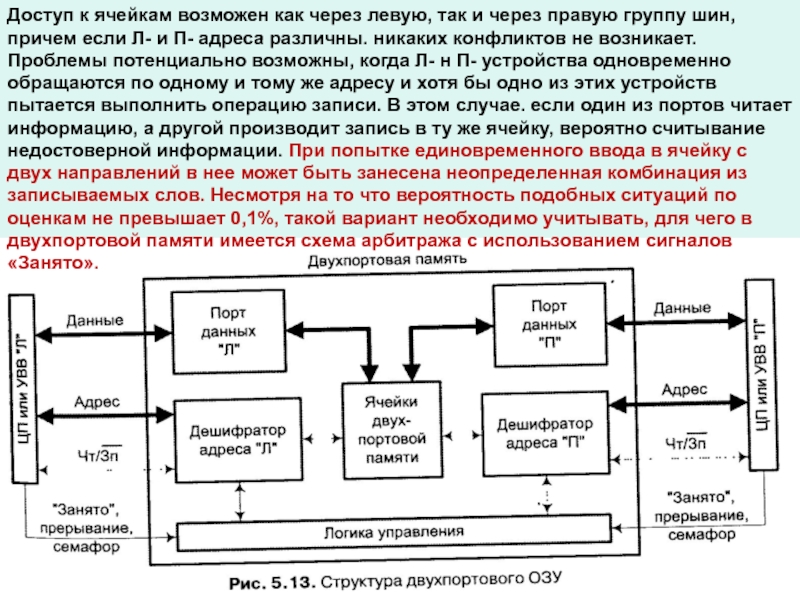

Доступ к ячейкам возможен как через левую, так и через

правую группу шин, причем если Л- и П- адреса различны.

никаких конфликтов не возникает. Проблемы потенциально возможны, когда Л- н П- устройства одновременно обращаются по одному и тому же адресу и хотя бы одно из этих устройств пытается выполнить операцию записи. В этом случае. если один из портов читает информацию, а другой производит запись в ту же ячейку, вероятно считывание недостоверной информации. При попытке единовременного ввода в ячейку с двух направлений в нее может быть занесена неопределенная комбинация из записываемых слов. Несмотря на то что вероятность подобных ситуаций по оценкам не превышает 0,1%, такой вариант необходимо учитывать, для чего в двухпортовой памяти имеется схема арбитража с использованием сигналов «Занято».

Слайд 18Маркировка микросхем памяти.

Корпус микросхемы или модуль памяти имеют специальные обозначения,

включающие, например, наименование (или знак) фирмы- изготовителя, дату выпуска и

т.п. Наибольший интерес для пользователя представляют, конечно, такие параметры, как информационная емкость и время выборки, то есть скорость доступа к хранимой информации. Обычно информация о микросхеме в ее названии состоит из трех полей: префикса, корня и суффикса. В поле корня одна из цифр обычно говорит о том, что это микросхема ОЗУ. Следующая за ней цифра, как правило, характеризует количество информационных разрядов: 1 – один разряд, 4 – четыре разряда. Группа цифр, следующая за ней, обозначает емкость в килобитах каждого информационного разряда (64 – 64 Кбит, 256 – 256 Кбит, 1000 – 1 Мбит). В поле суффикса буквой указывается тип корпуса (например, Р – пластмассовый, хотя тип может быть и не указан) и через дефис – время выборки в наносекундах (70 – 70 нс, 80 – 80 нс, 100 или 10 – 100 нс и т.д.).

Таким образом, по обозначению MK44256P-80 легко определить, что это микросхема памяти емкостью 4 разряда по 256 Кбит каждый и временем выборки 80 нс. Разумеется, форма записи параметров может отличаться от приведенных.

Слайд 19Раньше наиболее распространенными были 30-контактные SIMM-модули с байтовой организацией и

контролем четности (256Kx9, 1Мх9, 4Мх9, 16Мх9, соответственно емкостью 256 Кбайт,

1 Мбайт, 4 Мбайта и 16 Мбайт) (табл. 7, рис. 16). Кстати, на современных SIMM-модулях могут использоваться микросхемы емкостью 16 и даже 64 Мбит. Здесь стоит, видимо, сказать несколько слов о контроле четности.

В последнее время, особенно с появлением Pentium, все чаще начинают применяться 72-контактные З6-битовые, модули (32 бита – длина слова и по биту контроля четности на каждый байт). Они обозначаются как 256Кх36, 512Кх36, 1Мх36, 2Мх36, 4Мх36, 8МХ36, 16Мх36, что соответствует емкости 1, 2, 4, 8, 16, 32 и 64 Мбайта . Понятно, что такие модули для 486-х микропроцессоров могут уже устанавливаться и по одному. Максимально достижимый и этом случае объем памяти может быть разным, что зависит не только от количества разъемов под модули, но и от того, модули с какой максимальной емкостью поддерживаются контроллером памяти. На ряде системных плат установлены одновременно 30 и 72-контактные разъёмы для соответствующих SIMM-модулей.

Слайд 20Блоки памяти

Обычно вся оперативная память персонального компьютера делится на несколько

блоков, причём вид и тип элементов, используемых в них, зависят

от конструкции системной платы и приводятся в ее техническом описании. Банк определяет наименьшее количество памяти, которое может быть адресовано процессором за один раз и соответствует разрядности шины данных этого процессора. Например, микропроцессор i8088 за один раз может адресовать только один байт, i80286 – 16 бит, i80386 – 32, Pentium – 64. В том случае, если используется память с чередованием адресов (об этом чуть ниже), разрядность банка увеличивается вдвое.

Объем информации каждого банка памяти может быть различным, однако он, как правило, должен быть кратен девяти (8 бит данных плюс бит четности). На 30-контактных модулях памяти поэтому используется обычно либо три, либо девять микросхем (так называемые трех- и девятичиповые модули). Дело в том, что микросхемы динамической памяти имеют либо 1-, либо 4-разрядную организацию данных. На 72-контактных модулях размешено обычно 12

Слайд 211.2. Режимы работы памяти.

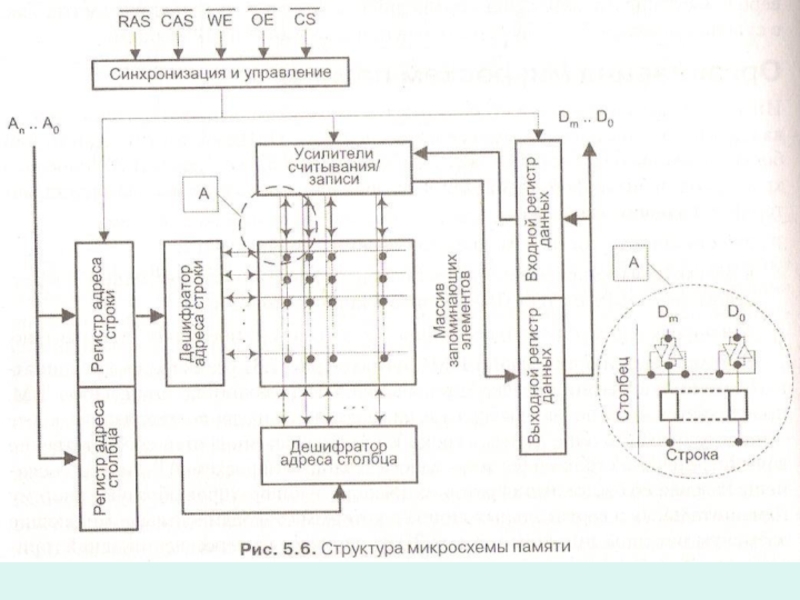

Напомним, что для адресации к любому биту,

например, 1-Мбитной микросхемы требуются 20 адресных линий, в то время

как корпус такой микросхемы имеет только 18 выводов. Дело в том, что для этой цели используется так называемое мультиплексирование адресов. Полный адрес ячейки данных делится на два компонента: – адрес строки (row address) и адрес столбца (column addrcss). Для сопровождения первого компонента служит сигнал RAS (Row Address Strobe), а второго – сигнал CAS (Colunm Ad-dress Slrobc). Вообще говоря, под временем выборки для микросхемы памяти понимается длительность именно сигнала RAS. В процессе обращения к микросхеме DRAM для записи или считывания информации необходимо сначала подать на ее адресные входы код адреса строки и одновременно с ним (или с некоторой ненормируемой задержкой) сигнал RAS, затем через нормированное время задержки должен 6ытъ подан код адреса столбца, сопровождаемый сигналом CAS. Следующее обращение к этой микросхеме возможно только после промежутка времени, в течение которого происходит восстановление (перезарядка) внутренних цепей микросхемы. Это время называют временем перезаряда (precharge time), причем оно составляет почти 90 % от общего времени выборки.

Слайд 22Способы повышения быстродействия.

Одним из способов повышения быстродействия динамической памяти является

метод управления памятью с чередованием адресов (intcrlcnviny mode). Дело и

том, что, используя даже обычные микросхемы DRAM, задержки, связанной со временем перезаряда, можно избежать, если каждые последовательно выбираемые ячейки памяти будут относиться к разным блокам памяти. Таким образом, метод чередования адресов предусматривает деление памяти на блоки (банки), из которых процессор должен считывать данные попеременно. То есть пока считываются данные из одной группы микросхем, другая группа получает время на перезарядку.

Другим способом повышения быстродействия, требующим, как правило, небольших архитектурных добавок, является метод страничной выборки (paging mode). Он базируется на том, что повторения сигнала RAS также можно избежать, если адреса строк выбираемых ячеек памяти лежат в пределах одной страницы, то есть адрес их строк неизменен. Напомним, что в микросхеме динамической памяти считывание в статический буфер происходит для всей строки целиком, конкретный же бит выбирается уже адресом столбца. Понятно, что если следующий подлежащий считыванию бит находится в той же строке, то нет смысла читать ее в буфер еще раз. Наиболее распространены две разновидности подобного режима: с повторением сигнала стробирования CAS при изменении младшей части адреса и без повторения. В последнем случае быстродействие, естественно, увеличивается. Заметим, что микросхемы BRAM, реализующие страничный режим, часто называют FPM (Fast Page Mode).

Слайд 23Для доступа к памяти реализован так называемый пакетный (burst) режим.

Он заключается в том, что при необходимости чтения одного слова

процессор вместе с ним считывает еще три, расположенных рядом. Обычно время пересылки измеряют в тактах и записывают, например, так 6-3-3-3. Это означает, что если на первую пересылку данных из памяти потребовалось 6 тактов работы процессора, то на каждую последующую – только по 3.

Например, Pentium, работающий на внутренней тактовой частоте 90 МГц, с внешней кэш-памятью (время доступа 15 нс) может обеспечить пакетный режим 3-2-2-2. Для обмена с динамической памятью параметры будут в два-три раза хуже, например 7-3-3-3.

В настоящее время можно выделить два основных схемотехнических решения, используемых для увеличения быстродействия динамической памяти. Одно из них основано на синхронной работе памяти и процессора, что достигается использованием внутренней конвейерной архитектуры и чередованием адресов. Другое решение предполагает включение в структуру динамической памяти определенного количества быстрой статической памяти, которая в данном случае работает примерно как встроенный кэш.

Слайд 24В качестве примеров технических решений можно привести технологии CDRAM (Cache

DRAM) и EDRAM (Enhanced DRAM). Обе они основаны на интеграции

небольшого количества ячеек быстрой SRAM (12 – 15 нс) к относительно медленной DRAM (35 – 40 нс). Например, на одном кристалле могут находиться 4 Мбайта HRAM и всего 16 Кбайт SRAM. Заметим, что статическая память выполнена либо как кэш прямого отображения, либо как наборно-ассоциативный кэш. Подобные микросхемы производят фирмы Mitsubishi, Samsung и Ramtron. По опубликованным данным, использование подобного типа памяти позволяет увеличить быстродействие по сравнению с классической архитектурой "память плюс кэш второго уровня".

SDRAM (Synchronous DRAM), основанная на подходе конвейерной архитектуры и чередовании адресов, позволяет еще больше поднять быстродействие оперативной памяти. Подобные микросхемы используют трехступенчатую конвейерную архитектуру и, кроме того, внутренний доступ типа "пинг-понг" к двум блокам памяти с чередованием адресов. Тактирование микросхем осуществляется внешней частотой для микропроцессоров. Современные SDRAM могут работать на тактовых частотах 66, 75, 83 и 100 МГц. Пионерами в разработке подобных устройств являются фирмы Samsung и NEC.

Одним из наиболее быстродействующих типов памяти является RDRAM (Rambus DRAM). Тактируемая частотой 250 Мгц. 9-разрядная RDRAM достигает пиковой скорости передачи 500 Мб/с.

Слайд 25Тем не менее, по оценкам экспертов, в ближайшее время следует

ожидать массового использования в персональных компьютерах так называемой EDO (Extended

Data Out) DRAM или ее разновидности BEDO (Burst EDO) DRAM. Во-первых, она обеспечивает более высокую скорость передачи (особенно в пакетном режиме), а во-вторых, полностью совместима по выводам с современными SIММ-модулями DRAM. В отличие от обычных микросхем DRAM в EDO DRAM добавлен набор регистров-"защелок", благодаря которым данные на выходе могут удерживаться даже в течение следующего запроса к микросхеме. Такого эффекта можно добиться на обыкновенных DRAM только в режиме чередования адресов. Напомним, что в любом обращении к памяти можно выделить три фазы: начало доступа; период, когда данные становятся действительными и непосредственно передача. Эти фазы повторяются последовательно для каждой ячейки в считываемой строке. В случае с EDO-памятью временные параметры (а следовательно, и быстродействие) улучшаются за счет исключения циклов ожидания в фазе готовности данных. В BEDO DRAM выборка четырех операндов, требуемых для передачи, происходит автоматически. Здесь добавлен специальный счетчик слов. Так, по некоторым данным, на частоте 66 МГц параметры пакетного режима для FРМ составляют 7-3-3-3, для EDO – 7-2-2-2), a для BEDO – 7-1-1-1.

Слайд 26 Кэш-память.

Функционально кэш-память предназначена для согласования скорости работы сравнительно медленных

устройств, таких как динамическая память с относительно быстрым микропроцессором. Дело

в том, что работа большинства элементов, на которых построен процессор, во многом похожа на работу ячеек статической памяти – триггеров. Поэтому их быстродействие существенно выше, нежели элементов динамической памяти. Использование кэш-памяти позволяет избежать циклов ожидания в его работе, которые снижают производительность всей.

По этому центральный процессор вынужден простаивать 2 – 3 периода тактовой частоты (то есть имеет 2 – 3 цикла ожидания), пока информация из соответствующих микросхем памяти установится на системной шине данных компьютера. Понятно, что в это время процессор не может выполнять никакую другую работу. Такая ситуация приводит к снижению общей производительности системы, что, разумеется, крайне нежелательно. Таким образом, узким местом системы становится оперативная динамическая память. С помощью технологии обработки, использующей кэш-память, найден определенный компромисс между стоимостью и производительностью системы.

Слайд 27Архитектура кэш-памяти

Прежде чем говорить об архитектуре кэш-памяти, введем такое

понятие, как длина строки-кеша (cache-line). Если при oбмeне данными между

устройствами речь обычно идет о блоке информации, то для кэш-памяти существует некий набор данных, называемых строкой.

Итак, архитектура кэш-памяти определяется тем, каким образом достаточно большая по размеру основная память отображается на сравнительно небольшой кэш. Существуют, вообще говоря, три разновидности отображения: кэш-память с прямым отображением (dircct-mappcd cachc), частично, или наборно-ассоциативная (set-associative cache) и полностью ассоциативная (fully associative cache). Все эти архитектуры так или иначе используются для построения кэш-памяти современных микропроцессоров.

Слайд 28 Кэш-память с прямым отображением.

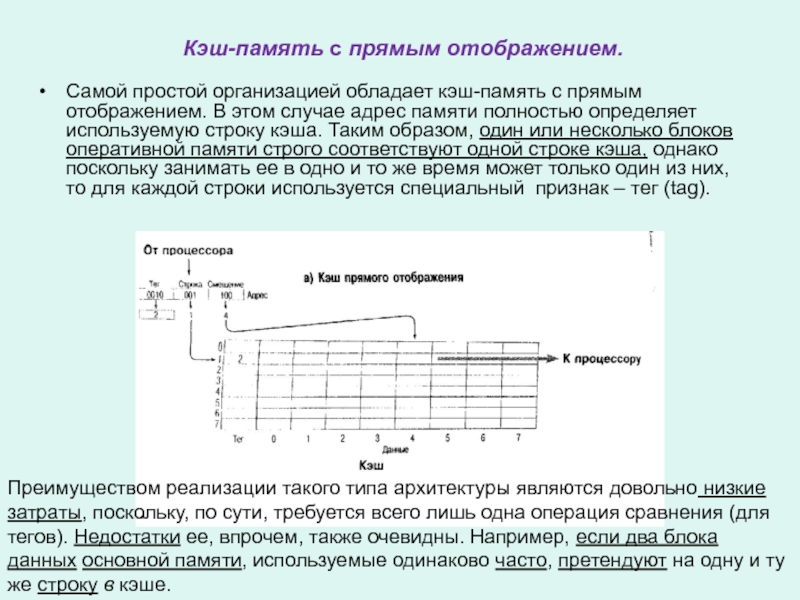

Самой простой организацией обладает кэш-память

с прямым отображением. В этом случае адрес памяти полностью определяет

используемую строку кэша. Таким образом, один или несколько блоков оперативной памяти строго соответствуют одной строке кэша, однако поскольку занимать ее в одно и то же время может только один из них, то для каждой строки используется специальный признак – тег (tag).

Преимуществом реализации такого типа архитектуры являются довольно низкие затраты, поскольку, по сути, требуется всего лишь одна операция сравнения (для тегов). Недостатки ее, впрочем, также очевидны. Например, если два блока данных основной памяти, используемые одинаково часто, претендуют на одну и ту же строку в кэше.

Слайд 29Полностью ассоциативная архитектура.

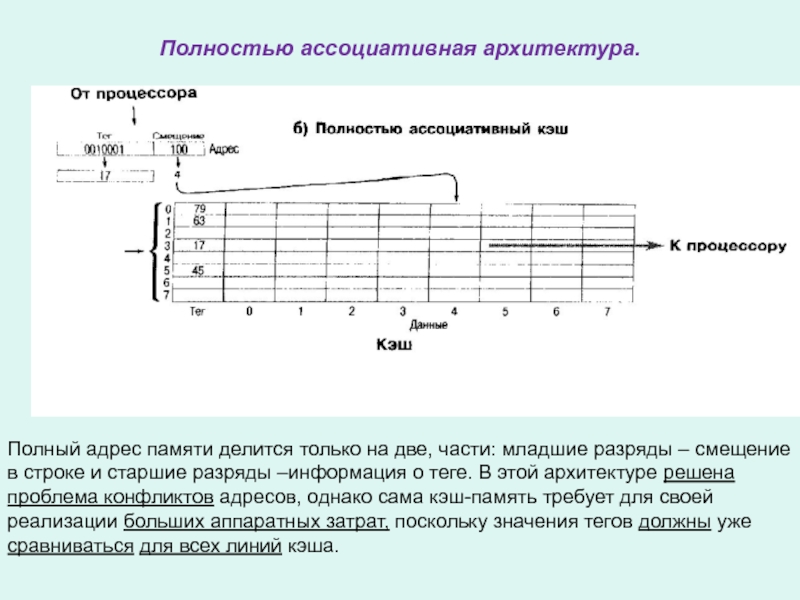

Полный адрес памяти делится только на две,

части: младшие разряды – смещение в строке и старшие разряды

–информация о теге. В этой архитектуре решена проблема конфликтов адресов, однако сама кэш-память требует для своей реализации больших аппаратных затрат, поскольку значения тегов должны уже сравниваться для всех линий кэша.

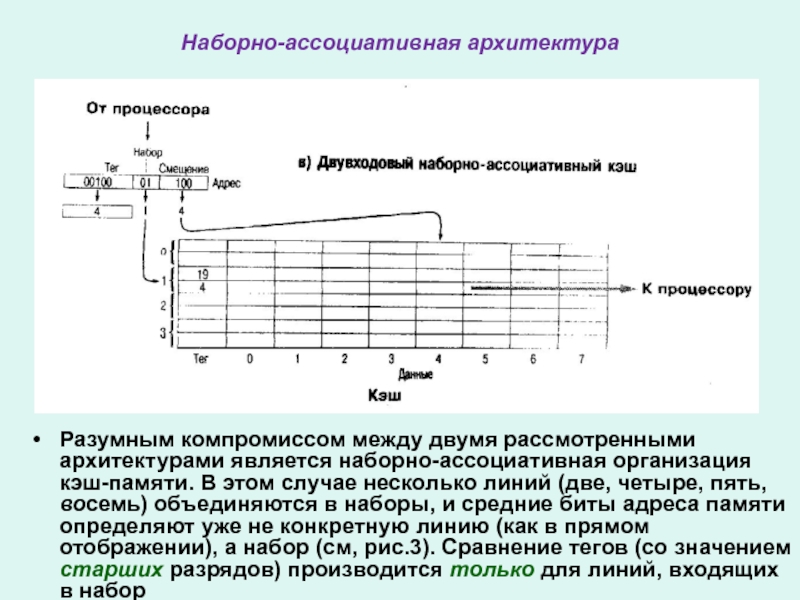

Слайд 30Наборно-ассоциативная архитектура

Разумным компромиссом между двумя рассмотренными архитектурами является наборно-ассоциативная

организация кэш-памяти. В этом случае несколько линий (две, четыре, пять,

восемь) объединяются в наборы, и средние биты адреса памяти определяют уже не конкретную линию (как в прямом отображении), а набор (см, рис.3). Сравнение тегов (со значением старших разрядов) производится только для линий, входящих в набор

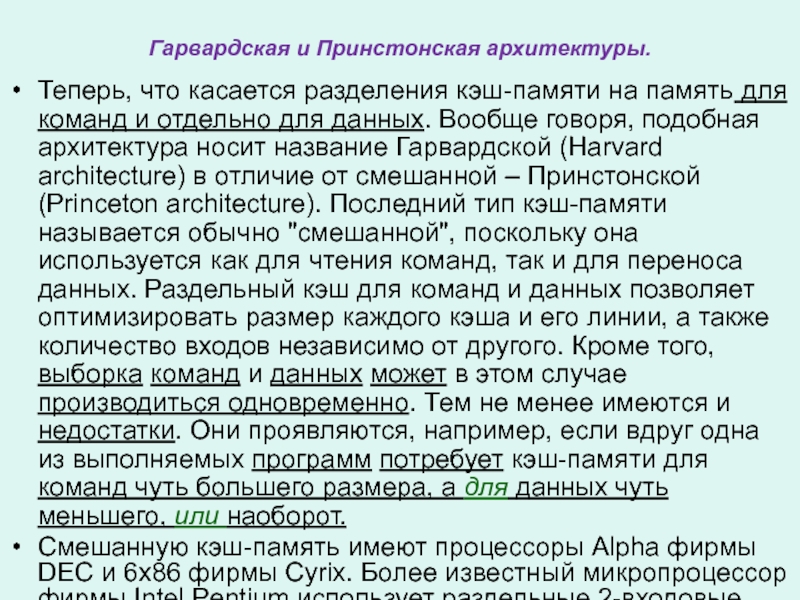

Слайд 31Гарвардская и Принстонская архитектуры.

Теперь, что касается разделения кэш-памяти на

память для команд и отдельно для данных. Вообще говоря, подобная

архитектура носит название Гарвардской (Harvard architecture) в отличие от смешанной – Принстонской (Princeton architecture). Последний тип кэш-памяти называется обычно "смешанной", поскольку она используется как для чтения команд, так и для переноса данных. Раздельный кэш для команд и данных позволяет оптимизировать размер каждого кэша и его линии, а также количество входов независимо от другого. Кроме того, выборка команд и данных может в этом случае производиться одновременно. Тем не менее имеются и недостатки. Они проявляются, например, если вдруг одна из выполняемых программ потребует кэш-памяти для команд чуть большего размера, а для данных чуть меньшего, или наоборот.

Смешанную кэш-память имеют процессоры Alpha фирмы DEC и 6х86 фирмы Cyrix. Более известный микропроцессор фирмы Intel Pentium использует раздельные 2-входовые наборно-ассоциативные кэши для команд и данных размером по 8 Кбайт.

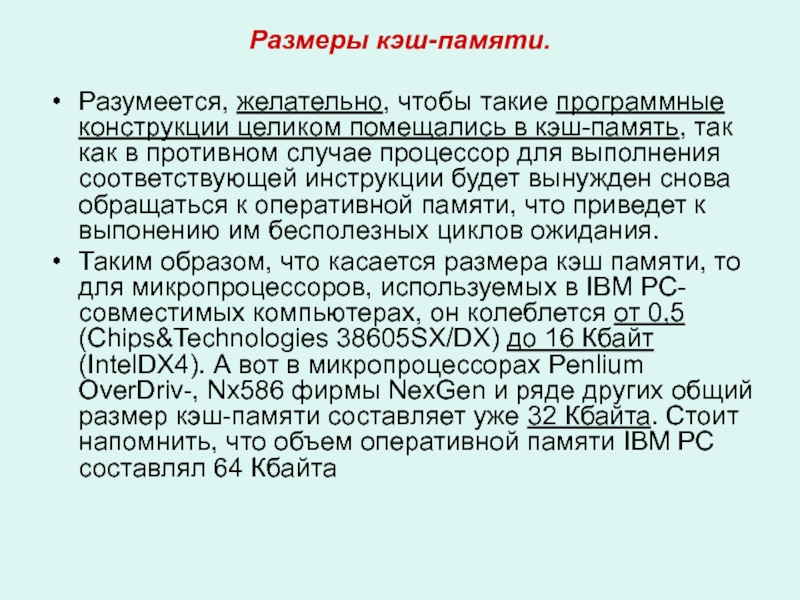

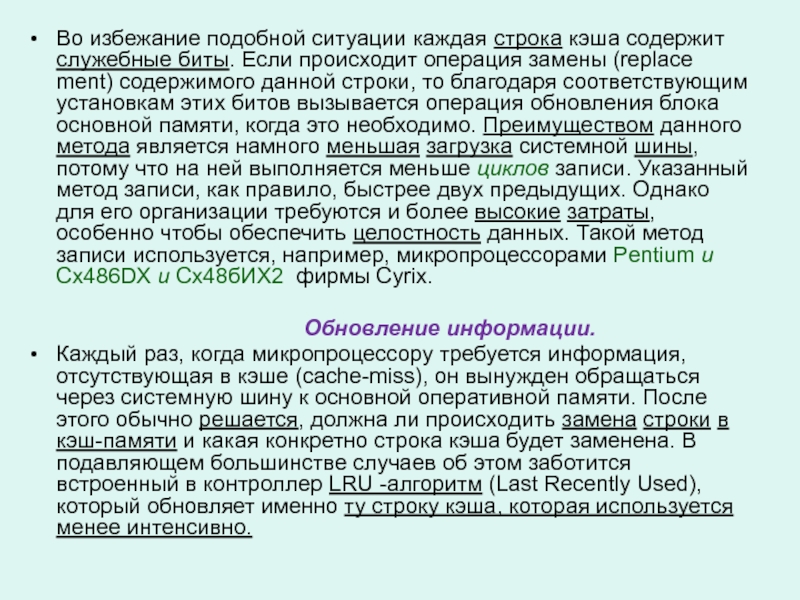

Слайд 32Размеры кэш-памяти.

Разумеется, желательно, чтобы такие программные конструкции целиком помещались

в кэш-память, так как в противном случае процессор для выполнения

соответствующей инструкции будет вынужден снова обращаться к оперативной памяти, что приведет к выпонению им бесполезных циклов ожидания.

Таким образом, что касается размера кэш памяти, то для микропроцессоров, используемых в IBM РС-совместимых компьютерах, он колеблется от 0,5 (Chips&Technologies 38605SX/DX) до 16 Кбайт (IntelDX4). А вот в микропроцессорах Penlium OverDriv-, Nx586 фирмы NexGen и ряде других общий размер кэш-памяти составляет уже 32 Кбайта. Стоит напомнить, что объем оперативной памяти IBM РС составлял 64 Кбайта

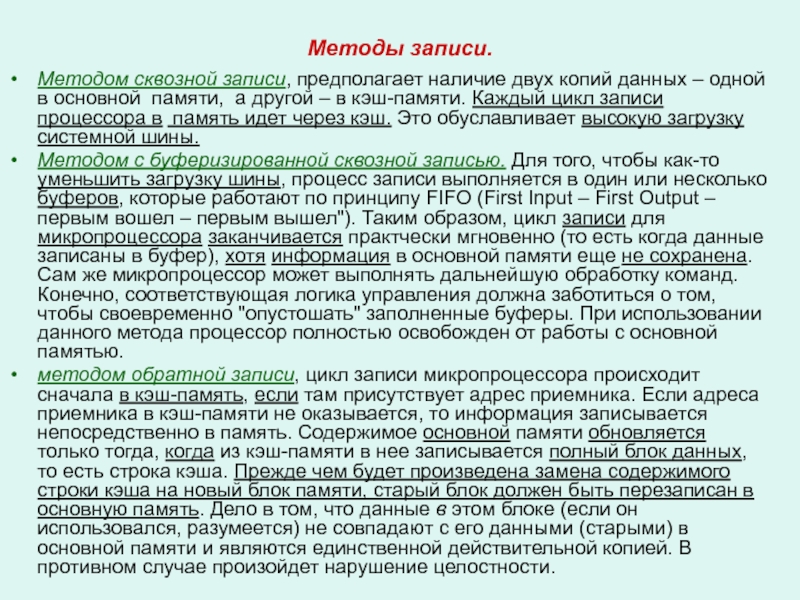

Слайд 34Методы записи.

Методом сквозной записи, предполагает наличие двух копий данных

– одной в основной памяти, а другой – в кэш-памяти.

Каждый цикл записи процессора в память идет через кэш. Это обуславливает высокую загрузку системной шины.

Методом с буферизированной сквозной записью. Для того, чтобы как-то уменьшить загрузку шины, процесс записи выполняется в один или несколько буферов, которые работают по принципу FIFO (First Input – First Output – первым вошел – первым вышел"). Таким образом, цикл записи для микропроцессора заканчивается практчески мгновенно (то есть когда данные записаны в буфер), хотя информация в основной памяти eщe не сохранена. Сам же микропроцессор может выполнять дальнейшую обработку команд. Конечно, соответствующая логика управления должна заботиться о том, чтобы своевременно "опустошать" заполненные буферы. При использовании данного метода процессор полностью освобожден от работы с основной памятью.

методом обратной записи, цикл записи микропроцессора происходит сначала в кэш-память, если там присутствует адрес приемника. Если адреса приемника в кэш-памяти не оказывается, то информация записывается непосредственно в память. Содержимое основной памяти обновляется только тогда, когда из кэш-памяти в нее записывается полный блок данных, то есть строка кэша. Прежде чем будет произведена замена содержимого строки кэша на новый блок памяти, старый блок должен быть перезаписан в основную память. Дело в том, что данные в этом блоке (если он использовался, разумеется) не совпадают с его данными (старыми) в основной памяти и являются единственной действительной копией. В противном случае произойдет нарушение целостности.

Слайд 35Во избежание подобной ситуации каждая строка кэша содержит служебные биты.

Если происходит операция замены (replace ment) содержимого данной строки, то

благодаря соответствующим установкам этих битов вызывается операция обновления блока основной памяти, когда это необходимо. Преимуществом данного метода является намного меньшая загрузка системной шины, потому что на ней выполняется меньше циклов записи. Указанный метод записи, как правило, быстрее двух предыдущих. Однако для его организации требуются и более высокие затраты, особенно чтобы обеспечить целостность данных. Такой метод записи используется, например, микропроцессорами Pentium и Cx486DX и Сх48бИХ2 фирмы Cyrix.

Обновление информации.

Каждый раз, когда микропроцессору требуется информация, отсутствующая в кэше (cache-miss), он вынужден обращаться через системную шину к основной оперативной памяти. После этого обычно решается, должна ли происходить замена строки в кэш-памяти и какая конкретно строка кэша будет заменена. В подавляющем большинстве случаев об этом заботится встроенный в контроллер LRU -алгоритм (Last Recently Used), который обновляет именно ту строку кэша, которая используется менее интенсивно.

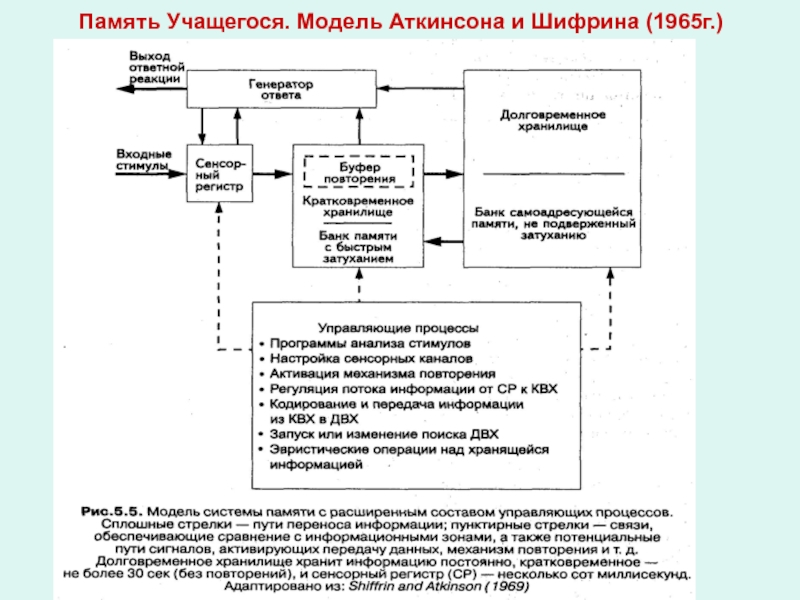

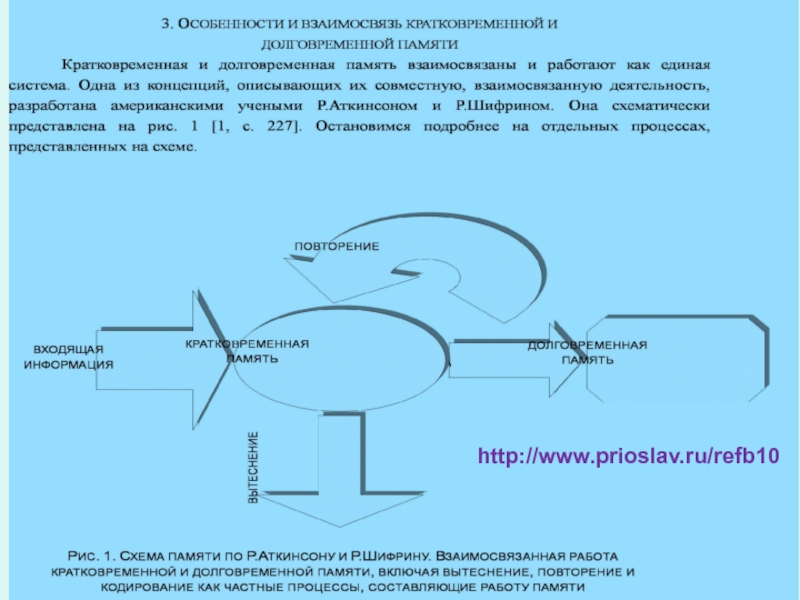

Слайд 37Память Учащегося. Модель Аткинсона и Шифрина (1965г.)

Слайд 41МЫ - ЧАСТЬ ПРОСТРАНСТВА

Вы чувствуете в жизни только

небольшую частицу себя, только свое физическое тело. Вы видите из

окошечка своего внутреннего мира только кусочек планеты, этот крошечный кусочек мироздания. Вы ограничены своим мышлением, своими понятиями, своим представлением. Каждый из вас видит, чувствует и понимает очень маленькую часть мира и только часть того, что вы на самом деле собой представляете. Ведь ваша искра духа, отлетевшая от Космического магнита, путешествуя по Пространству, видела очень много, и вы храните в себе знания Пространства.

Каждый человек знает все, об этом говорят мудрецы Востока. Каждый человек является огромной и полноправной частью Пространства. Ваша аура бесконечна; энергия, окружающая вас, уходит в Пространство на огромные расстояния, и ваша мысль слышна на далеких планетах. Вы тревожите эти планеты, тревожите саму нашу планету совершенно неконтролируемыми мыслями, сопровождающимися отрицательными сильными эмоциями; сотрясаете мир, сотрясаете Пространство, не находя выхода из своего маленького жизненного тупика.

Пространство пронизывает нас, пронизывает мир, мы в нем растворяемся и при желании ощущаем его силу и мудрость, накопленную на протяжении веков, тысячелетий, миллионов лет... Нам надо только уметь соединяться с ним, чтобы эта мудрость была ваша. Все в мире есть - только откройтесь миру.

http://samlib.ru/p/peunowa_s_m/azbuka1.shtml

Слайд 42О, Память, сохрани

Лишь То, что всем полезно!

Мир знаньем освяти

И вечно

и мгновенно.

Дай радость испытать

Всегда, в любое время

И жизни передать

Любви благое

семя.

О, Память, чистой стань

От негатива тьмы.

Наш целостный подход

Тогда освоим мы.

МВД 23.10.13.