Слайд 1Архитектура системы команд

Н. В. Горбунов

Системой команд ЭВМ называют полный перечень

команд, которые способна выполнять данная ЭВМ.

Под архитектурой системы команд

принято определять те средства ЭВМ, которые доступны программисту.

Архитектуру истемы команд можно рассматривать как средство согласования требований программного обеспечения с возможностями аппаратуры ЭВМ

Слайд 2Архитектура системы команд

Н. В. Горбунов

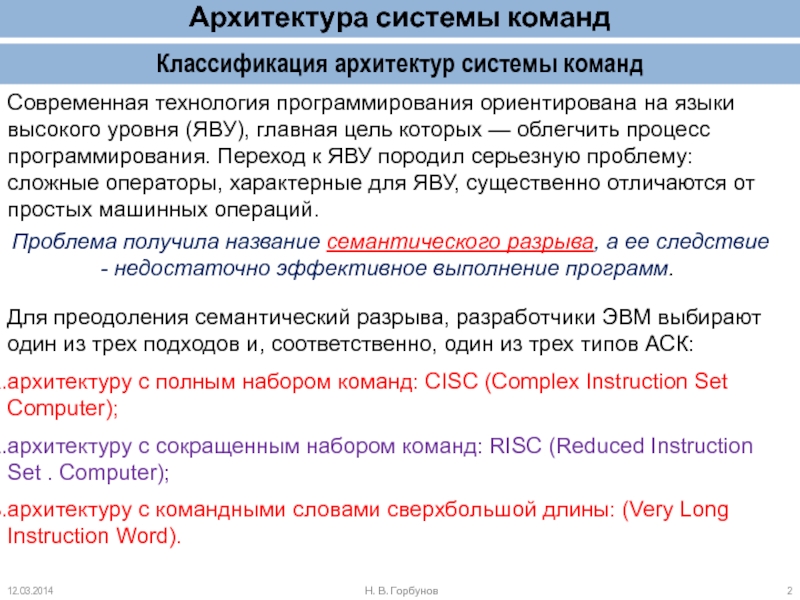

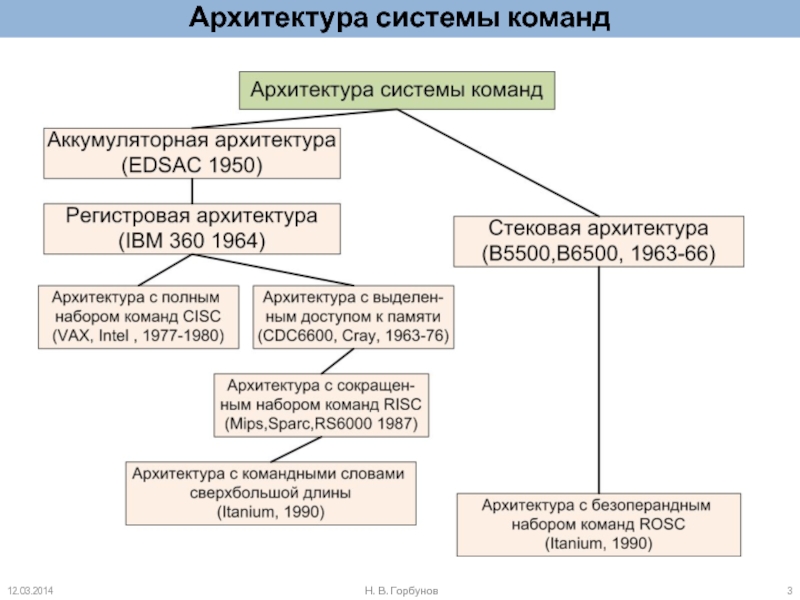

Классификация архитектур системы команд

Современная технология программирования

ориентирована на языки высокого уровня (ЯВУ), главная цель которых —

облегчить процесс программирования. Переход к ЯВУ породил серьезную проблему: сложные операторы, характерные для ЯВУ, существенно отличаются от простых машинных операций.

Проблема получила название семантического разрыва, а ее следствие - недостаточно эффективное выполнение программ.

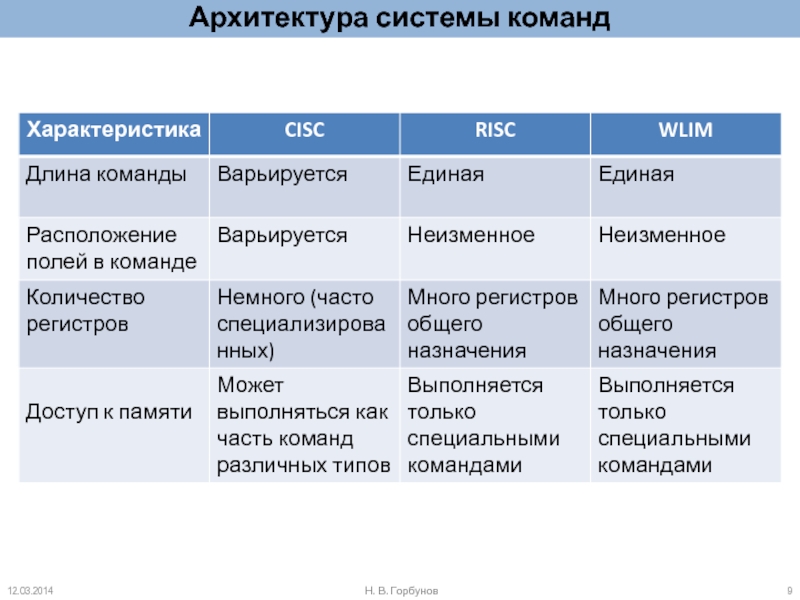

Для преодоления семантический разрыва, разработчики ЭВМ выбирают один из трех подходов и, соответственно, один из трех типов АСК:

архитектуру с полным набором команд: CISC (Complex Instruction Set Computer);

архитектуру с сокращенным набором команд: RISC (Reduced Instruction Set . Computer);

архитектуру с командными словами сверхбольшой длины: (Very Long Instruction Word).

Слайд 3Архитектура системы команд

Н. В. Горбунов

Слайд 4Архитектура системы команд

Н. В. Горбунов

Для CISC-архитектуры типичны:

• наличие в

процессоре сравнительно небольшого числа регистров общего назначения;

• большое количество

машинных команд, некоторые из них аппаратно реализуют сложные операторы ЯВУ;

• разнообразие способов адресации операндов;

• множество форматов команд различной разрядности;

• наличие команд, где обработка совмещается с обращением к памяти.

К типу CISC можно отнести практически все ЭВМ, выпускавшиеся до середины 1980-х годов, и значительную часть производящихся в настоящее время.

Этот способ решения проблемы семантического разрыва ведет

к усложнению аппаратуры ЭВМ, главным образом устройства

управления, что негативно сказывается на производительности ЭВМ.

Слайд 5CISC, Архитектура системы команд

Н. В. Горбунов

Были проведены исследования и обнаружилось,

что доля дополнительных команд, эквивалентных операторам ЯВУ, в общем объеме

программ не превышает 10-20%, а для некоторых наиболее сложных команд даже 0,2%.

А объем аппаратурных средств, требуемых для реализации дополнительных команд, возрастает весьма существенно.

Так, емкость микропрограммной памяти при поддержании сложных команд может увеличиваться на 60%.

В результате появилась архитектура RISC

Слайд 6RISC, Архитектура системы команд

Н. В. Горбунов

Термин RISC впервые использовал Д.

Паттерсон и Д. Дитцель в 1980 г.

Идея в ограничении

списка команд ВМ наиболее часто используемыми простейшими командами, оперирующими данными, размещенными только в регистрах процессорах.

Обращение к памяти допускается с помощью специальных команд чтения/записи.

Резко уменьшено количество форматов команд и способов указания адресов операндов.

Сокращение числа форматов команд и их простота, использование ограниченного количества способов адресации, отделение операций обработки данных от операций обращения к памяти позволяет существенно упростить аппаратурные средства ЭВМ и повысить их быстродействие.

Реализация сложных команд за счет последовательности из простых, но быстрых RISC-команд оказывается не менее эффективной, чем аппаратный вариант сложных команд

в CISC-архитектуре.

Слайд 7RISC, Архитектура системы команд

Н. В. Горбунов

Элементы RISC-архитектуры впервые появились в

вычислительных машинах CDC 6600 и суперЭВМ компании Cray Research.

Успешно

реализуется RISC-архитектура в современных ЭВМ, например в процессорах Alpha фирмы DEC, серии РА фирмы Hewlett-Packard, семействе PowerPC и т. п.

Отметим, что в последних микропроцессорах фирмы Intel и AMD широко используются идеи, свойственные RISC-архитектуре, так что многие различия между CISC и RISC постепенно стираются.

Слайд 8VLIW, Архитектура системы команд

Н. В. Горбунов

Кроме CISC- и RISC-архитектур есть

еще один тип - архитектура с командными словами сверхбольшой длины

(VLIW).

Концепция VLIW базируется на RISC-архитектуре, где несколько простых RISC-команд объединяются в одну сверхдлинную команду и выполняются параллельно.

Архитектура VLIW сравнительно мало отличается от RISC. Появился лишь дополнительный уровень параллелизма вычислений, в силу чего архитектуру VLIW логичнее адресовать не к вычислительным машинам, а к вычислительным системам.

Слайд 9Архитектура системы команд

Н. В. Горбунов

Слайд 10Архитектура системы команд

Н. В. Горбунов

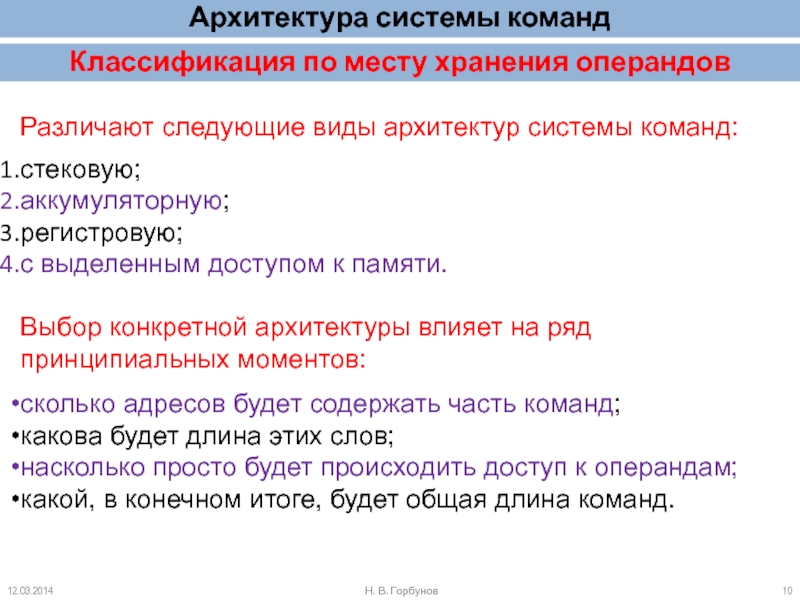

Классификация по месту хранения операндов

Различают следующие

виды архитектур системы команд:

стековую;

аккумуляторную;

регистровую;

с выделенным доступом к

памяти.

Выбор конкретной архитектуры влияет на ряд принципиальных моментов:

сколько адресов будет содержать часть команд;

какова будет длина этих слов;

насколько просто будет происходить доступ к операндам;

какой, в конечном итоге, будет общая длина команд.

Слайд 11Архитектура системы команд

Н. В. Горбунов

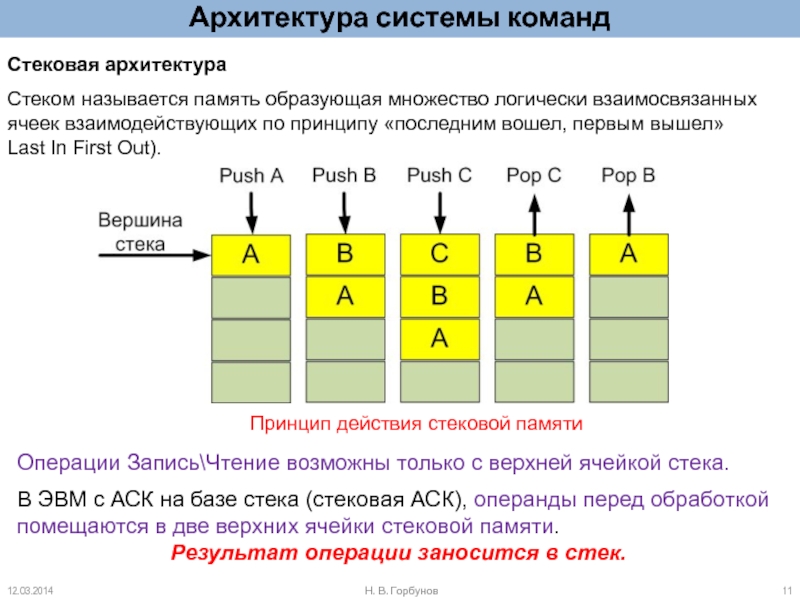

Стековая архитектура

Стеком называется память образующая множество

логически взаимосвязанных ячеек взаимодействующих по принципу «последним вошел, первым вышел»

Last In First Out).

Принцип действия стековой памяти

Операции Запись\Чтение возможны только с верхней ячейкой стека.

В ЭВМ с АСК на базе стека (стековая АСК), операнды перед обработкой помещаются в две верхних ячейки стековой памяти.

Результат операции заносится в стек.

Слайд 12Архитектура системы команд

Н. В. Горбунов

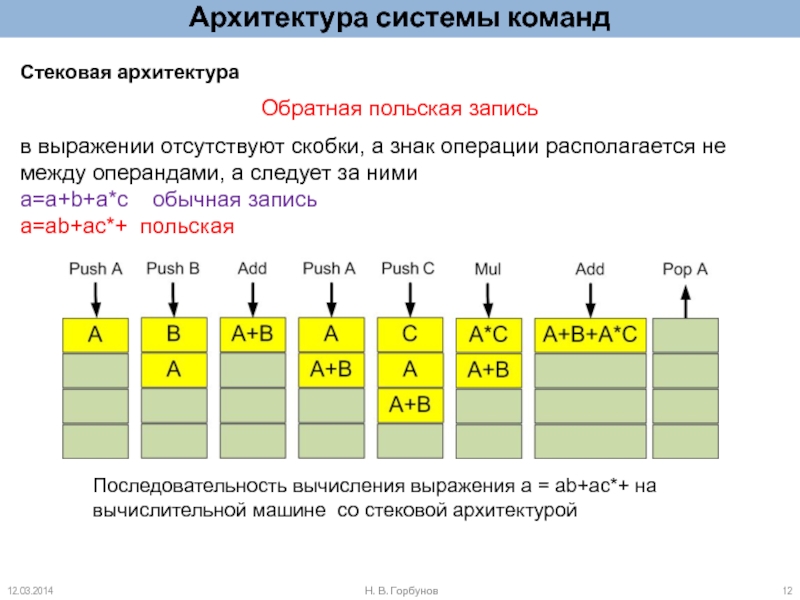

Стековая архитектура

Обратная польская запись

в выражении отсутствуют

скобки, а знак операции располагается не между операндами, а следует

за ними

a=a+b+a*c обычная запись

a=ab+ac*+ польская

Последовательность вычисления выражения а = ab+ac*+ на вычислительной машине со стековой архитектурой

Слайд 13Архитектура системы команд

Н. В. Горбунов

Стековая архитектура

К достоинствам АСК на базе

стека следует отнести возможность сокращения части команд, поскольку все операции

производятся через вершину стека то есть адреса операндов и результата в командах арифметической и логической обработки информации указывать не нужно. Код программы получается компактным. Достаточно просто реализуется декодирование команд.

Стек становится «узким местом» при повышении производительности.

Стековая архитектура долгое время считалась неперспективной, применялась в ЭВМ 1960-х годов, (Burroughs (B5500, В6500) или фирмы Hewlett-Packard HP 3000/70).

Последние события в области ЭВМ свидетельствуют о возрождении интереса к стековой архитектуре. Связано это с популярностью языка Java и расширением сферы применения языка Forth, семантике которых наиболее близка именно стековая архитектура.

Слайд 14Архитектура системы команд

Н. В. Горбунов

Аккумуляторная архитектура - одна из первых.

В ней для хранения одного из операндов арифметической или логической

операции в процессоре имеется выделенный регистр — аккумулятор. В этот же регистр заносится и результат операции.

Адрес одного из операндов предопределен (аккумулятор), в командах нужно указать местоположение только второго операнда.

Изначально оба операнда хранятся в основной памяти, и до выполнения операции один из них нужно загрузить в аккумулятор.

После выполнения команды обработки результат находится в аккумуляторе и, если он не является операндом для последующей команды, его требуется сохранить в ячейке памяти.

Слайд 15Архитектура системы команд

Н. В. Горбунов

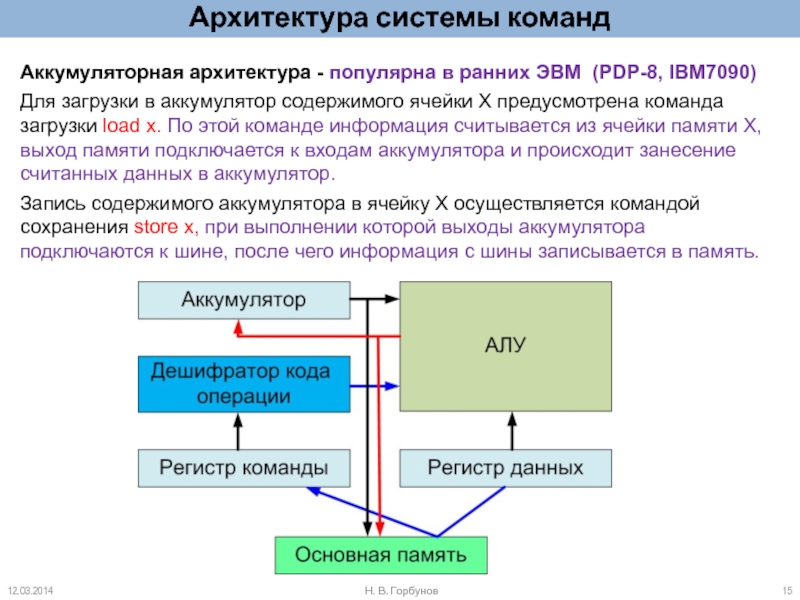

Аккумуляторная архитектура - популярна в ранних

ЭВМ (PDP-8, IBM7090)

Для загрузки в аккумулятор содержимого ячейки Х предусмотрена

команда загрузки load х. По этой команде информация считывается из ячейки памяти Х, выход памяти подключается к входам аккумулятора и происходит занесение считанных данных в аккумулятор.

Запись содержимого аккумулятора в ячейку Х осуществляется командой сохранения store х, при выполнении которой выходы аккумулятора подключаются к шине, после чего информация с шины записывается в память.

Слайд 16Архитектура системы команд

Н. В. Горбунов

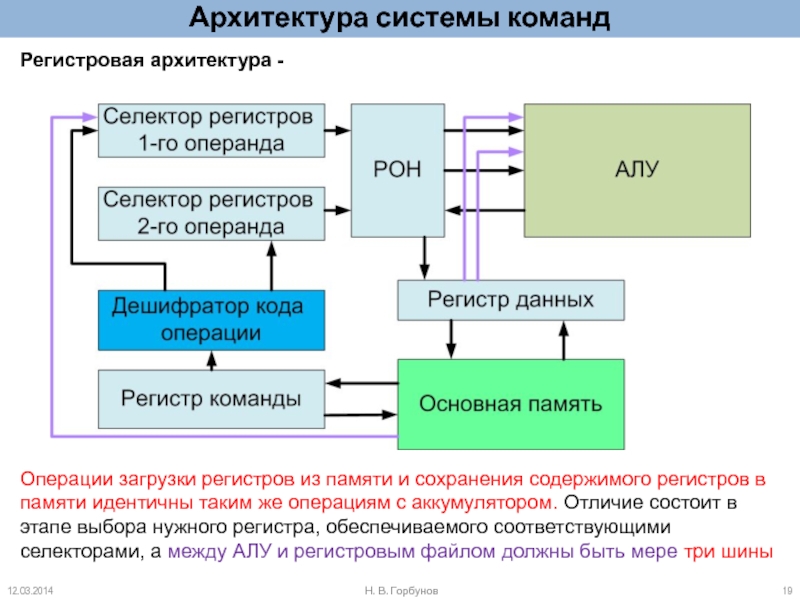

Регистровая архитектура - CDC 6600, IBM

360/370, PDP-11

Процессор включает в себя массив регистров общего назначения (РОН).

Эти регистры, в каком-то смысле, можно рассматривать как явно управляемый кэш для хранения недавно использовавшихся данных.

Размер регистров обычно совпадает с размером машинного слова.

К регистру можно обратиться, указав его номер.

Количество РОН в архитектурах типа CISC обычно невелико (от 8 до 32), и для их адресации необходимо не более пяти разрядов, поэтому в команд можно указать номера двух, а зачастую и трех регистров (двух регистров операндов и регистра результата).

Регистровая архитектура допускает расположение операндов как в основной памяти так и в РОН.

В рамках регистровых АСК выделяют три подвида команд обработки:

регистр-регистр;

регистр-память;

память-память.

Слайд 17Архитектура системы команд

Н. В. Горбунов

Оценка вариантов размещения операндов

Слайд 18Архитектура системы команд

Н. В. Горбунов

Вариант «регистр-регистр» является основным в вычислительных

машинах типа RISC.

Команды типа «регистр-память» характерны для CISC-машин.

Вариант

«память-память» считается неэффективным, хотя и остается в наиболее сложных моделях машин класса CISC.

Операции загрузки регистров из памяти и сохранения содержимого регистров в памяти идентичны таким же операциям с аккумулятором.

Отличие состоит в этапе выбора нужного регистра, обеспечиваемого соответствующими селекторами.

Слайд 19Архитектура системы команд

Н. В. Горбунов

Регистровая архитектура -

Операции загрузки регистров

из памяти и сохранения содержимого регистров в памяти идентичны таким

же операциям с аккумулятором. Отличие состоит в этапе выбора нужного регистра, обеспечиваемого соответствующими селекторами, а между АЛУ и регистровым файлом должны быть мере три шины

Слайд 20Архитектура системы команд

Н. В. Горбунов

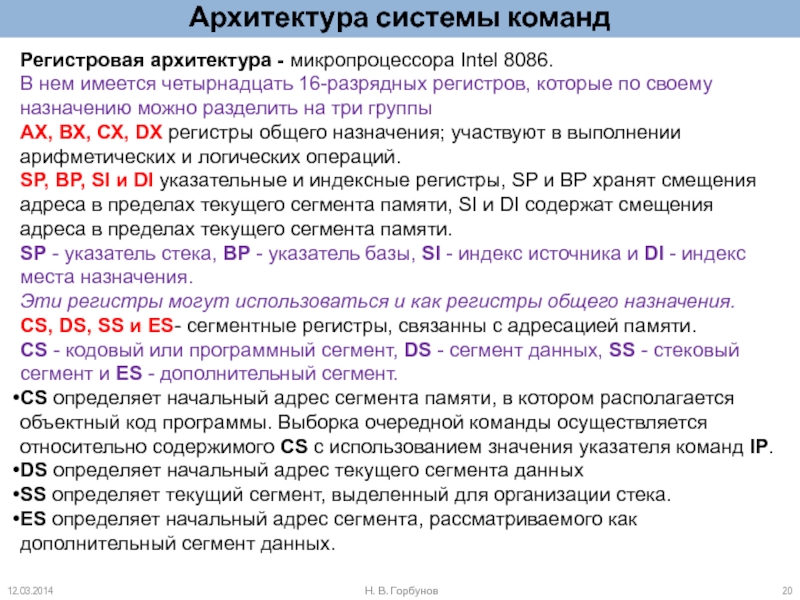

Регистровая архитектура - микропроцессора Intel 8086.

В нем имеется четырнадцать 16-разрядных регистров, которые по своему назначению

можно разделить на три группы

АХ, ВХ, СХ, DX регистры общего назначения; участвуют в выполнении арифметических и логических операций.

SP, BP, SI и DI указательные и индексные регистры, SP и ВР хранят смещения адреса в пределах текущего сегмента памяти, SI и DI содержат смещения адреса в пределах текущего сегмента памяти.

SP - указатель стека, ВР - указатель базы, SI - индекс источника и DI - индекс места назначения.

Эти регистры могут использоваться и как регистры общего назначения.

CS, DS, SS и ES- сегментные регистры, связанны с адресацией памяти.

CS - кодовый или программный сегмент, DS - сегмент данных, SS - стековый сегмент и ES - дополнительный сегмент.

CS определяет начальный адрес сегмента памяти, в котором располагается объектный код программы. Выборка очередной команды осуществляется относительно содержимого CS с использованием значения указателя команд IP.

DS определяет начальный адрес текущего сегмента данных

SS определяет текущий сегмент, выделенный для организации стека.

ES определяет начальный адрес сегмента, рассматриваемого как дополнительный сегмент данных.

Слайд 21Архитектура системы команд

Н. В. Горбунов

Регистровая архитектура - микропроцессора Intel 8086.

Кроме перечисленных регистров имеются два 16-разрядных регистра:

IP - указатель

команд и F - регистр флагов.

В регистре IP формируется относительный (относительно CS) адрес команды, подлежащей исполнению.

В регистре F (используются следующие девять разрядов:

C - перенос,

P - четность,

A - вспомогательный перенос,

Z - нулевой результат,

S - знак,

T - пошаговый режим,

I - разрешение прерывания,

D - направление,

O - переполнение.

Неиспользованные разряды на рисунке заштрихованы.

Слайд 22Архитектура системы команд

Н. В. Горбунов

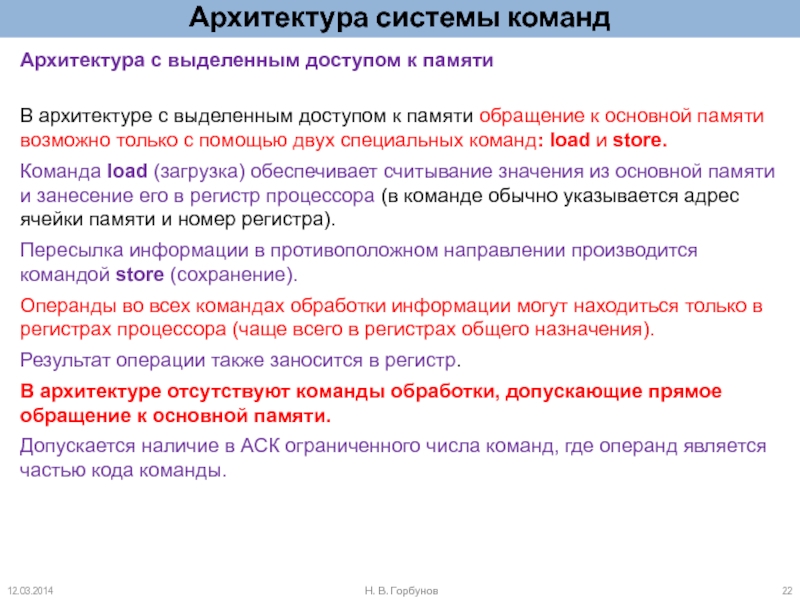

Архитектура с выделенным доступом к памяти

В архитектуре с выделенным доступом к памяти обращение к основной

памяти возможно только с помощью двух специальных команд: load и store.

Команда load (загрузка) обеспечивает считывание значения из основной памяти и занесение его в регистр процессора (в команде обычно указывается адрес ячейки памяти и номер регистра).

Пересылка информации в противоположном направлении производится командой store (сохранение).

Операнды во всех командах обработки информации могут находиться только в регистрах процессора (чаще всего в регистрах общего назначения).

Результат операции также заносится в регистр.

В архитектуре отсутствуют команды обработки, допускающие прямое обращение к основной памяти.

Допускается наличие в АСК ограниченного числа команд, где операнд является частью кода команды.

Слайд 23Архитектура системы команд

Н. В. Горбунов

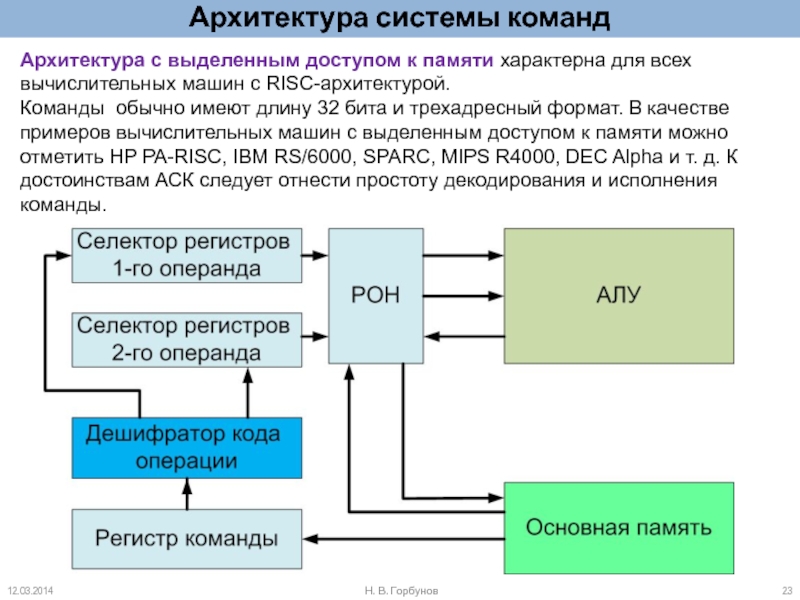

Архитектура с выделенным доступом к памяти

характерна для всех вычислительных машин с RISC-архитектурой.

Команды обычно имеют

длину 32 бита и трехадресный формат. В качестве примеров вычислительных машин с выделенным доступом к памяти можно отметить HP PA-RISC, IBM RS/6000, SPARC, MIPS R4000, DEC Alpha и т. д. К достоинствам АСК следует отнести простоту декодирования и исполнения команды.

Слайд 24Адресация INTEL – x86

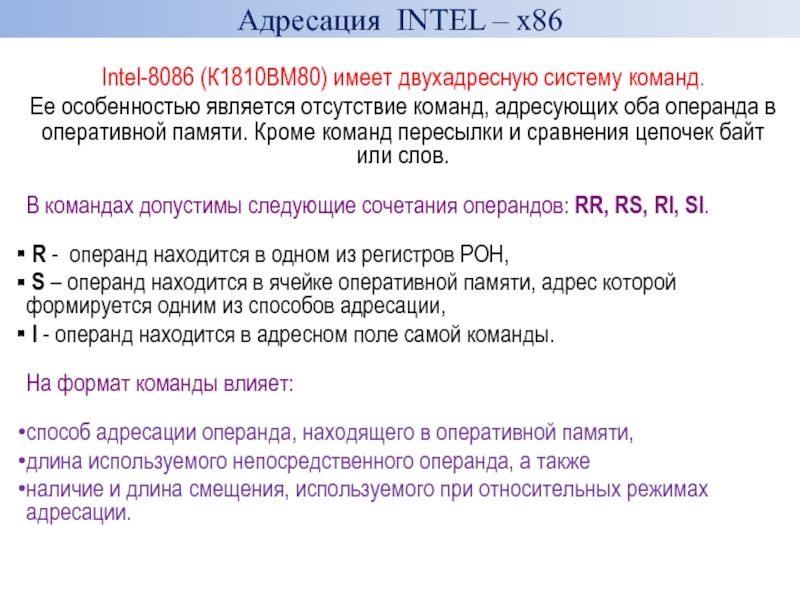

Intel-8086 (К1810ВМ80) имеет двухадресную систему команд.

Ее

особенностью является отсутствие команд, адресующих оба операнда в оперативной памяти.

Кроме команд пересылки и сравнения цепочек байт или слов.

В командах допустимы следующие сочетания операндов: RR, RS, RI, SI.

R - операнд находится в одном из регистров РОН,

S – операнд находится в ячейке оперативной памяти, адрес которой формируется одним из способов адресации,

I - операнд находится в адресном поле самой команды.

На формат команды влияет:

способ адресации операнда, находящего в оперативной памяти,

длина используемого непосредственного операнда, а также

наличие и длина смещения, используемого при относительных режимах адресации.

Слайд 25Адресация INTEL – x86

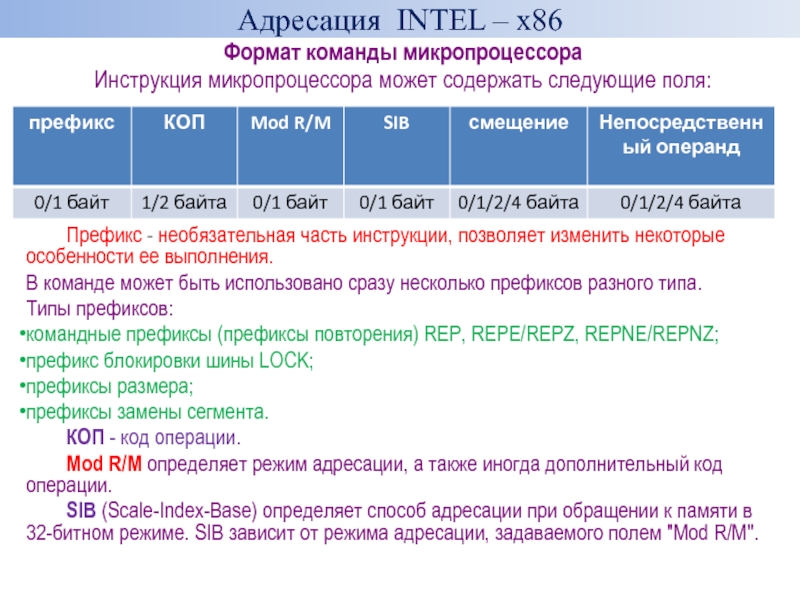

Формат команды микропроцессора

Инструкция микропроцессора может содержать

следующие поля:

Префикс - необязательная часть инструкции, позволяет изменить некоторые

особенности ее выполнения.

В команде может быть использовано сразу несколько префиксов разного типа.

Типы префиксов:

командные префиксы (префиксы повторения) REP, REPE/REPZ, REPNE/REPNZ;

префикс блокировки шины LOCK;

префиксы размера;

префиксы замены сегмента.

КОП - код операции.

Mod R/M определяет режим адресации, а также иногда дополнительный код операции.

SIB (Scale-Index-Base) определяет способ адресации при обращении к памяти в 32-битном режиме. SIB зависит от режима адресации, задаваемого полем "Mod R/M".

Слайд 26Адресация INTEL – x86

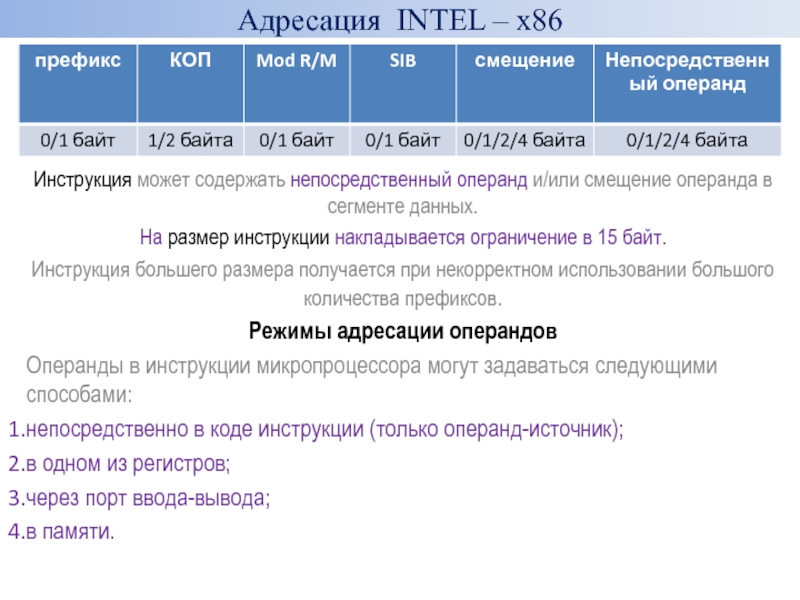

Инструкция может содержать непосредственный операнд и/или смещение

операнда в сегменте данных.

На размер инструкции накладывается ограничение в

15 байт.

Инструкция большего размера получается при некорректном использовании большого количества префиксов.

Режимы адресации операндов

Операнды в инструкции микропроцессора могут задаваться следующими способами:

непосредственно в коде инструкции (только операнд-источник);

в одном из регистров;

через порт ввода-вывода;

в памяти.

Слайд 27Адресация INTEL – x86

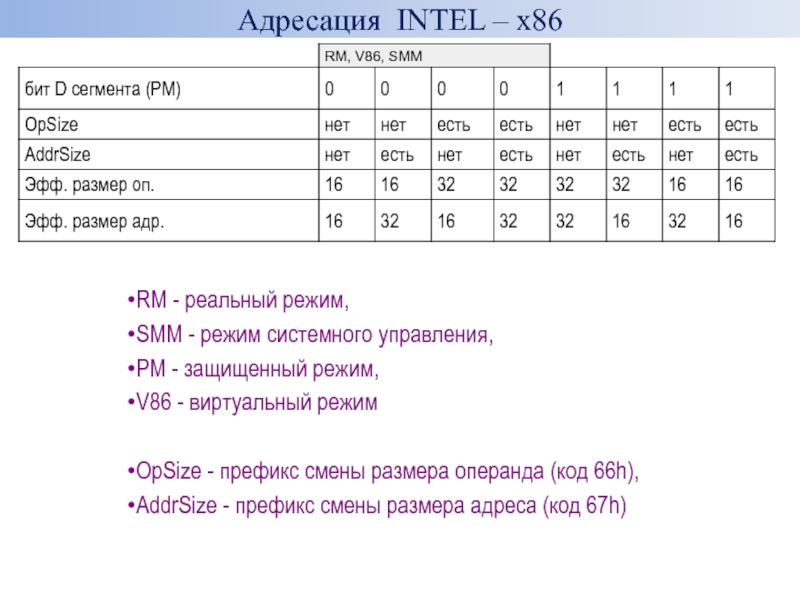

Для совместимости с 16-битными процессорами архитектура IA-32

использует одинаковые коды для инструкций, оперирующих как с 16-битными, так

и 32-битными операндами.

Новая архитектура предусматривает также новые возможности при указании адреса для операнда в памяти.

Как процессор будет считать операнд или его адрес, зависит от эффективного размера операнда и эффективного размера адреса для данной команды.

Эти значения определяются на основе режима работы, бита D дескриптора используемого сегмента и наличия в инструкции определенных префиксов.

Слайд 28Адресация INTEL – x86

RM - реальный режим,

SMM - режим

системного управления,

PM - защищенный режим,

V86 - виртуальный режим

OpSize

- префикс смены размера операнда (код 66h),

AddrSize - префикс смены размера адреса (код 67h)

Слайд 29Адресация INTEL – x86

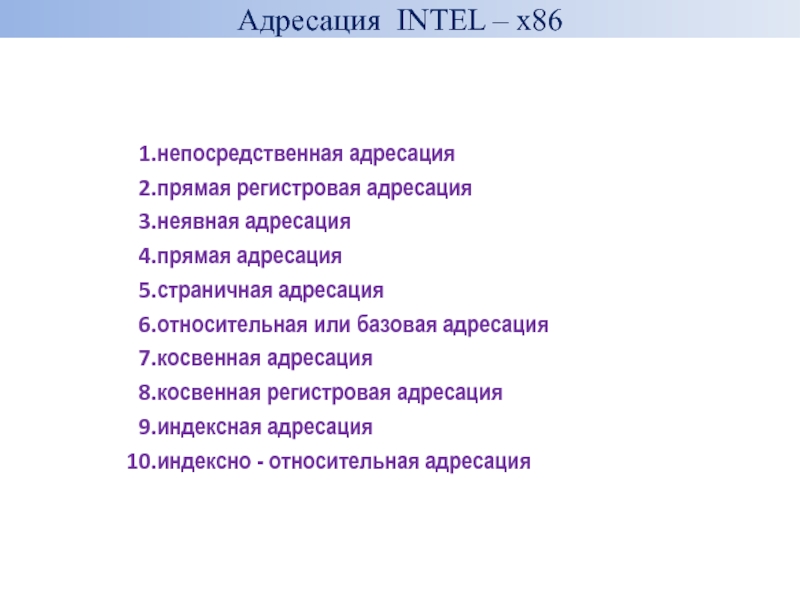

непосредственная адресация

прямая регистровая адресация

неявная адресация

прямая адресация

страничная адресация

относительная или базовая адресация

косвенная адресация

косвенная регистровая

адресация

индексная адресация

индексно - относительная адресация

Слайд 30Адресация INTEL – x86

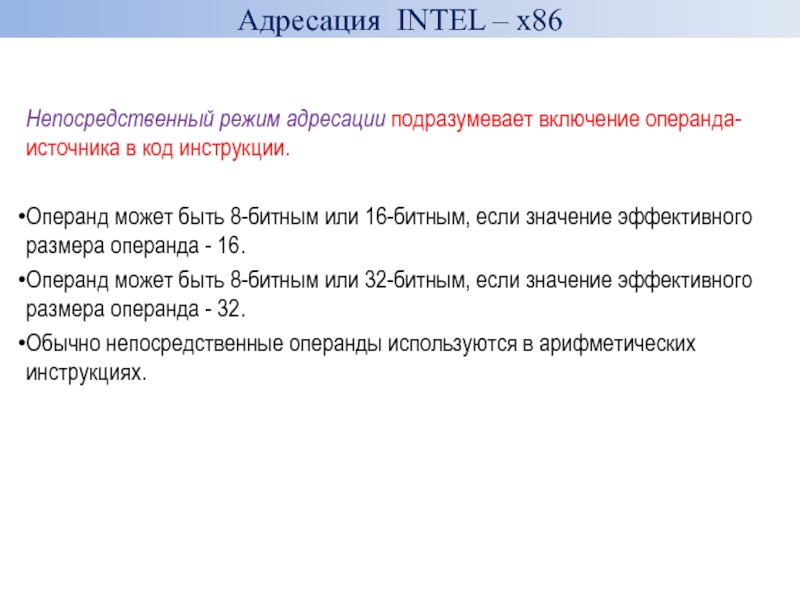

Непосредственный режим адресации подразумевает включение операнда-источника в

код инструкции.

Операнд может быть 8-битным или 16-битным, если значение

эффективного размера операнда - 16.

Операнд может быть 8-битным или 32-битным, если значение эффективного размера операнда - 32.

Обычно непосредственные операнды используются в арифметических инструкциях.

Слайд 31Адресация INTEL – x86

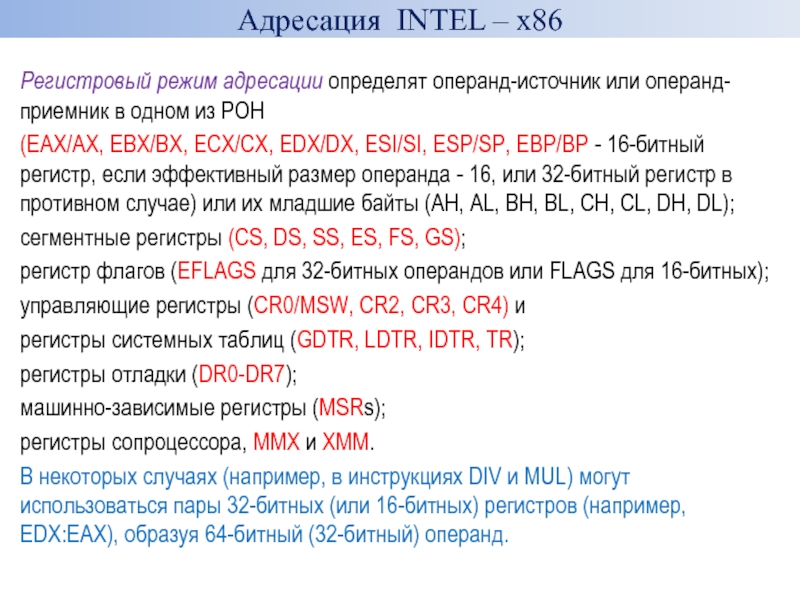

Регистровый режим адресации определят операнд-источник или операнд-приемник

в одном из РОН

(EAX/AX, EBX/BX, ECX/CX, EDX/DX, ESI/SI, ESP/SP,

EBP/BP - 16-битный регистр, если эффективный размер операнда - 16, или 32-битный регистр в противном случае) или их младшие байты (AH, AL, BH, BL, CH, CL, DH, DL);

сегментные регистры (CS, DS, SS, ES, FS, GS);

регистр флагов (EFLAGS для 32-битных операндов или FLAGS для 16-битных);

управляющие регистры (CR0/MSW, CR2, CR3, CR4) и

регистры системных таблиц (GDTR, LDTR, IDTR, TR);

регистры отладки (DR0-DR7);

машинно-зависимые регистры (MSRs);

регистры сопроцессора, MMX и XMM.

В некоторых случаях (например, в инструкциях DIV и MUL) могут использоваться пары 32-битных (или 16-битных) регистров (например, EDX:EAX), образуя 64-битный (32-битный) операнд.

Слайд 32Адресация INTEL – x86

Неявная адресация, когда местоположение операнда предопределено кодом

операции.

Обычно операнд находится в специальном регистре процессора, например, в

регистре-аккумуляторе или в вершине стека.

Слайд 33Адресация INTEL – x86

Адресация через порт ввода-вывода подразумевает получение операнда

или сохранение операнда через пространство портов ввода-вывода.

Адрес порта ввода-вывода

либо непосредственно включается в код инструкции, либо берется из регистра DX.

Адресация через память подразумевает получение операнда или сохранение операнда через память.

Таким образом может быть указан операнд-источник или операнд-приемник. Следует отметить, что процессор не позволяет одновременно задавать оба операнда через память (за исключением некоторых цепочечных команд).

Слайд 34Адресация INTEL – x86

Способ определения операнда называется режимом адресации. Рассмотрим

наиболее типичные режимы адресации микропроцессора 8086. Они разделяются на два

класса — режимы адресации данных и режимы адресации переходов.

Различают следующие режимы адресации.

Непосредственный. Операнд длиной 8 или 16 бит является частью команды.

IMUL AX,5 AX = 10 До

AX = 50 После...

Прямой. 16-битный эффективный адрес Операнда является частью команды.

MOV EAX,[1994h], EAX = 0000h DS:1994h = 5000h До

EAX = 5000h DS:1994h = 5000h После...

Слайд 35Адресация INTEL – x86

Регистровый. Операнд содержится в определяемом командой регистре.

16-битный операнд может находиться в регистрах АХ, ВХ, СХ, DX,

SI, DI, SP или ВР, а 8-битный - в регистрах AL, АН, BL, ВН, CL, CH, DL или DH.

MOVL R2,R3 R2 = 00000010 R3 = 00001000 до

R2 = 00001000 R3 = 00001000 после

Регистровый косвенный. Эффективный адрес Операнда находится в базовом регистре ВХ или индексном регистре, определяемых командой:

MOVL (R2),R3

(00000010)= 100 (R2) R2 = 00000010 R3 = 00000010 до

(00000010)= 10 (R2) R2 = 00000010 R3 = 00000010 после

Слайд 36Адресация INTEL – x86

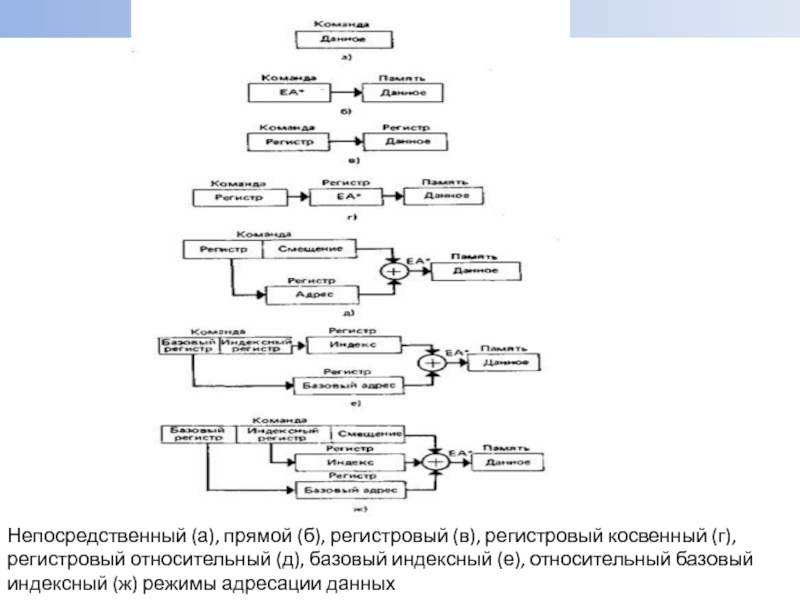

Непосредственный (а), прямой (б), регистровый (в),

регистровый косвенный (г), регистровый относительный (д), базовый индексный (е), относительный

базовый индексный (ж) режимы адресации данных

Слайд 37Адресация INTEL – x86

Базовый Эффективный адрес равен сумме содержимого базового

регистра и непосредственного смещения:

ADD AX,[BP+10h]

AX = 0067h BP = 0100h→DS:100h до

(BPh+10h)

= 0110h→DS:012h

AX = 0079h BP = 0100h→DS:100h после

Слайд 38Адресация INTEL – x86

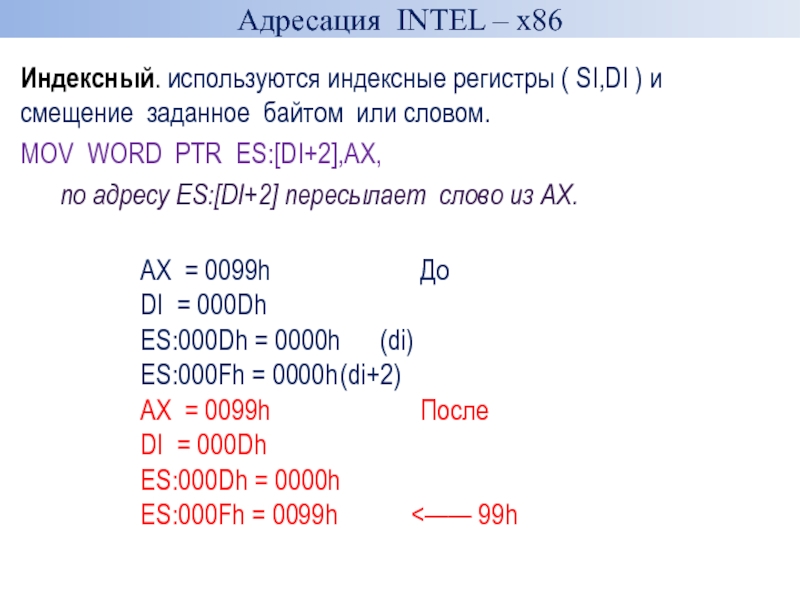

Индексный. используются индексные регистры ( SI,DI )

и смещение заданное байтом или словом.

MOV WORD PTR ES:[DI+2],AX,

по адресу ES:[DI+2] пересылает слово из AX.

AX = 0099h До

DI = 000Dh

ES:000Dh = 0000h (di)

ES:000Fh = 0000h (di+2)

AX = 0099h После

DI = 000Dh

ES:000Dh = 0000h

ES:000Fh = 0099h <—— 99h

Слайд 39Адресация INTEL – x86

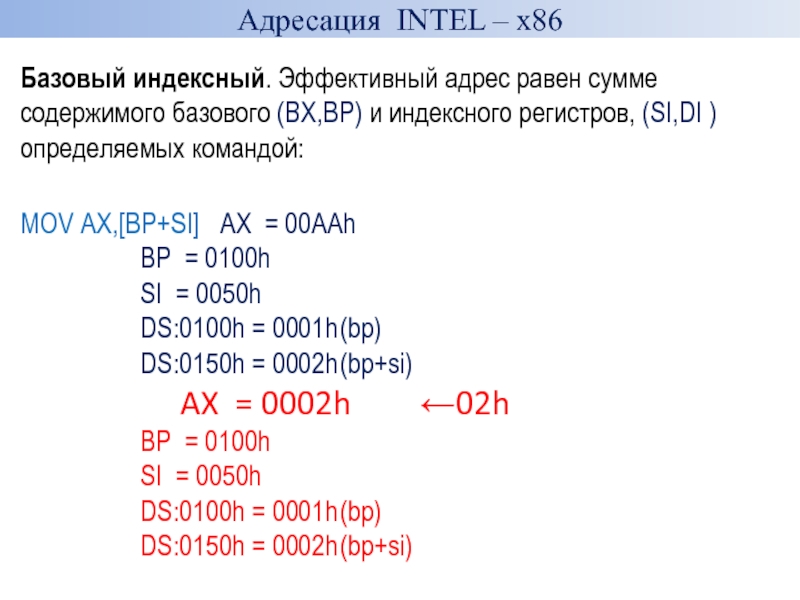

Базовый индексный. Эффективный адрес равен сумме содержимого

базового (BX,BP) и индексного регистров, (SI,DI ) определяемых командой:

MOV AX,[BP+SI] AX

= 00AAh

BP = 0100h

SI = 0050h

DS:0100h = 0001h (bp)

DS:0150h = 0002h (bp+si)

AX = 0002h ←02h

BP = 0100h

SI = 0050h

DS:0100h = 0001h (bp)

DS:0150h = 0002h (bp+si)

Слайд 40Адресация INTEL – x86

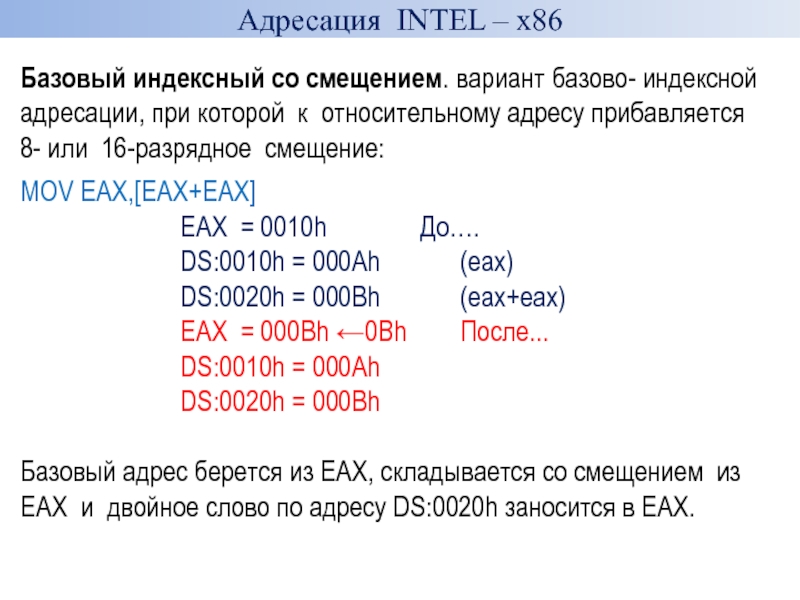

Базовый индексный со смещением. вариант базово- индексной

адресации, при которой к относительному адресу прибавляется

8- или 16-разрядное

смещение:

MOV EAX,[EAX+EAX]

EAX = 0010h До….

DS:0010h = 000Ah (eax)

DS:0020h = 000Bh (eax+eax)

EAX = 000Bh ←0Вh После...

DS:0010h = 000Ah

DS:0020h = 000Bh

Базовый адрес берется из EAX, складывается со смещением из EAX и двойное слово по адресу DS:0020h заносится в EAX.

Слайд 41Адресация INTEL – x86

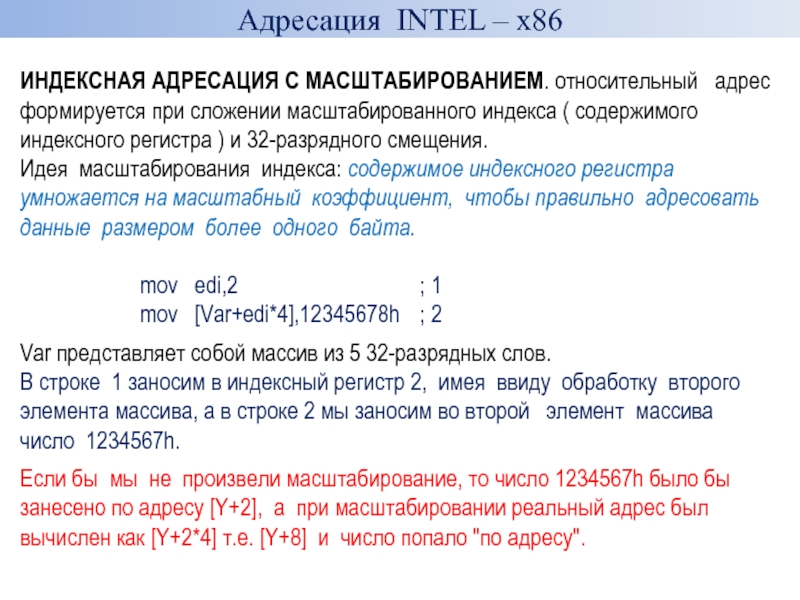

ИНДЕКСНАЯ АДРЕСАЦИЯ С МАСШТАБИРОВАНИЕМ. относительный адрес

формируется при сложении масштабированного индекса ( содержимого индексного регистра )

и 32-разрядного смещения.

Идея масштабирования индекса: содержимое индексного регистра умножается на масштабный коэффициент, чтобы правильно адресовать данные размером более одного байта.

mov edi,2 ; 1

mov [Var+edi*4],12345678h ; 2

Var представляет собой массив из 5 32-разрядных слов.

В строке 1 заносим в индексный регистр 2, имея ввиду обработку второго элемента массива, а в строке 2 мы заносим во второй элемент массива число 1234567h.

Если бы мы не произвели масштабирование, то число 1234567h было бы занесено по адресу [Y+2], а при масштабировании реальный адрес был вычислен как [Y+2*4] т.е. [Y+8] и число попало "по адресу".

Слайд 42Адресация INTEL – x86

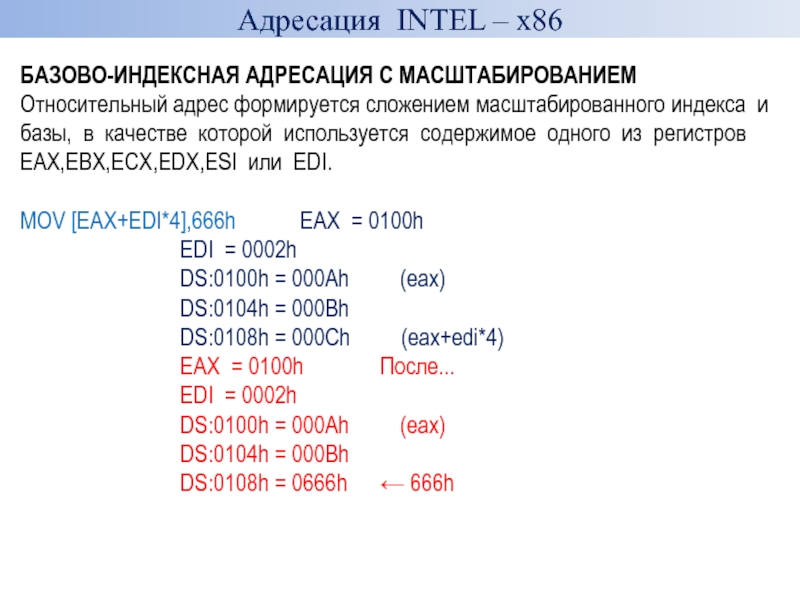

БАЗОВО-ИНДЕКСНАЯ АДРЕСАЦИЯ С МАСШТАБИРОВАНИЕМ Относительный адрес формируется

сложением масштабированного индекса и базы, в качестве которой используется содержимое

одного из регистров EAX,EBX,ECX,EDX,ESI или EDI.

MOV [EAX+EDI*4],666h EAX = 0100h

EDI = 0002h

DS:0100h = 000Ah (eax)

DS:0104h = 000Bh

DS:0108h = 000Ch (eax+edi*4)

EAX = 0100h После...

EDI = 0002h

DS:0100h = 000Ah (eax)

DS:0104h = 000Bh

DS:0108h = 0666h ← 666h

Слайд 43Адресация INTEL – x86

БАЗОВО-ИНДЕКСНАЯ АДРЕСАЦИЯ СО СМЕЩЕНИЕМ И МАСШТАБИРОВАНИЕМ

пример

Инструкция INC

[EAX+EDI*4+12345678h] увеличит на единицу число,

адрес которого вычисляется, как базовый

плюс 32-разрядное смещение 12345678h,

плюс масштабированный по основанию 4 индекс, из регистра EDI.

Слайд 44Адресация INTEL – x86

ОТНОСИТЕЛЬНАЯ АДРЕСАЦИЯ

Относительная адресация используется

в микропроцессоре 80386 при выполнении ряда команд управления ( условные

и безусловные переходы, вызовы подпрограмм, управление циклами и т.д. ), чтобы адресовать ячейку памяти, содержащую следующую команду. При этом способе адрес формируется как сумма содержимого регистра EIP(IP) ( instruction pointer), соответствующего текущей команде, и 8-, 16- или 32-разрядного смещения, определяющего положение следующей команды, относительно текущей.

Например рассмотрим операцию безусловного перехода в приведенном фрагменте

mov ax,5

jmp @1

sub ax,ax

@1: mov bx,ax

Слайд 45Адресация INTEL – x86

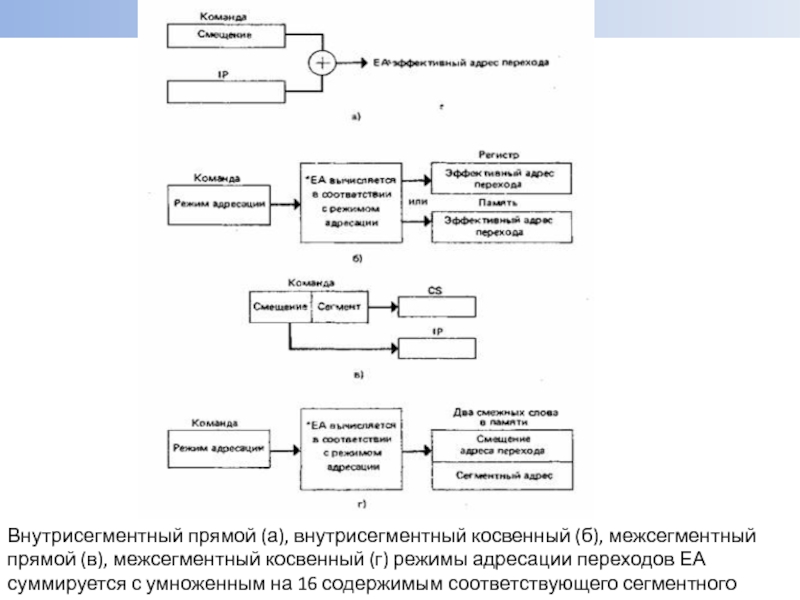

Режимы для указания адресов перехода

Внутрисегментный прямой. Эффективный

адрес перехода равен сумме 8-или 16-битного смещения и текущего содержимого

IP. Когда смещение имеет длину 8 бит, этот режим называется коротким переходом. Внутрисегментную прямую адресацию в большинстве книг называют относительной адресацией, так как смещение вычисляется "относительно" IP. Этот режим допустим в условных и безусловных переходах, но в команде условного перехода может быть только смещение длиной 8 бит.

Внутрисегментный косвенный. Эффективный адрес перехода есть содержимое регистра или ячейки памяти, которые указываются в любом режиме (кроме непосредственного) адресации данных. Содержимое IP заменяется эффективным адресом перехода. Данный режим допустим только в командах безусловного перехода.

Слайд 46Адресация INTEL – x86

Межсегментный прямой. Заменяет содержимое IP одной частью

команды, а содержимое CS — другой частью команды. Назначение данного

режима адресации — обеспечить переход из одного сегмента кода в другой.

Межсегментный косвенный. Заменяет содержимое IP и CS содержимым двух смежных слов из памяти, которые определяются в любом режиме адресации данных кроме непосредственного и регистрового.

Слайд 47Адресация INTEL – x86

Внутрисегментный прямой (а), внутрисегментный косвенный (б), межсегментный

прямой (в), межсегментный косвенный (г) режимы адресации переходов ЕА суммируется

с умноженным на 16 содержимым соответствующего сегментного регистра

Слайд 48Адресация INTEL – x86 В защищенном режиме

Адресация INTEL – x86

в защищенном режиме

Слайд 49Адресация INTEL – x86 В защищенном режиме

Для получения операнда из

памяти процессору необходимо знать селектор сегмента и смещение в сегменте.

Селектор может быть указан непосредственно в коде инструкции или можно явно или неявно использовать значение одного из сегментных регистров. Под неявным - подразумевается то, что в зависимости от предназначения операнда процессор использует определенный сегментный регистр для обращения к памяти: CS - для выборки инструкций; SS - для работы со стеком или обращения к памяти через регистры ESP или EBP; ES - для получения адреса операнда-приемника в цепочечных командах; DS - при всех остальных обращениях к памяти.

Явное использование сегментных регистров возможно, если в код инструкции включается префикс смены сегмента.

Указание префикса смены сегмента допустимо не для всех команд: нельзя менять сегмент для команд работы со стеком (всегда используется SS), для цепочечных команд можно менять сегмент только операнда-источника (операнд-приемник всегда адресуется через ES).

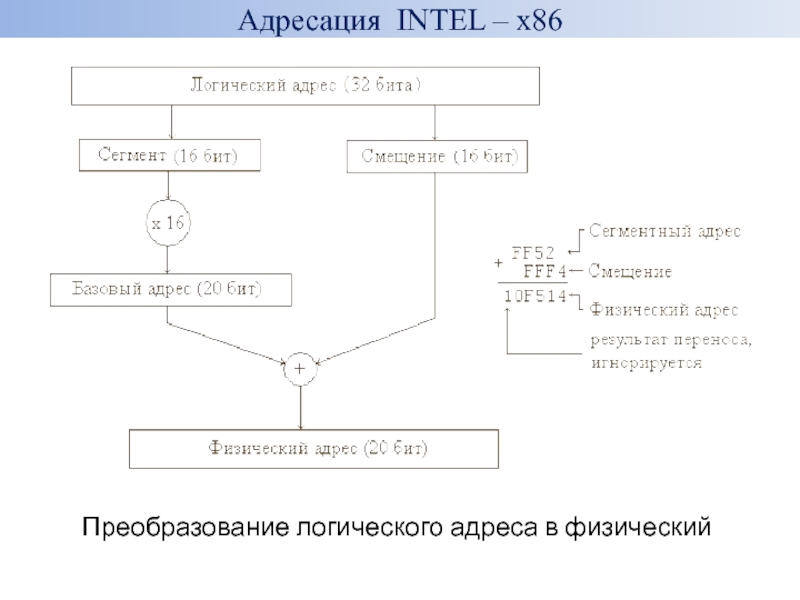

Слайд 50Адресация INTEL – x86

Преобразование логического адреса в физический

Слайд 51Адресация INTEL – x86

Смещение в сегменте (эффективный или исполнительный адрес

- EA) может быть вычислено на основе значений регистров общего

назначения и/или указанного в коде инструкции относительного смещения, при этом любой или даже несколько из указанных компонентов могут отсутствовать:

EA = BASE + (INDEX*SCALE) + DISPLACEMENT

Слайд 52Адресация INTEL – x86

Таким образом, различные способы вычисления эффективного адреса

формируют еще несколько режимов адресации:

EA=DISPLACEMENT (например, INC byte ptr

[500h]);

EA=BASE (например, MOV AL,[BX] для операнда-источника);

EA=BASE+DISPLACEMENT (например, ADD AL,[ECX+1234h] для операнда-источника);

EA=BASE+(INDEX*SCALE) (например, SUB EAX,[EBX+ECX*2] для операнда-источника);

EA=INDEX*SCALE+DISPLACEMENT (например, MOV [EAX*4+TableOffset],BL для операнда-приемника);

EA=BASE+(INDEX*SCALE)+DISPLACEMENT (например, DEC dword ptr [EAX+ECX*2+200h]) и др.

Слайд 53Адресация INTEL – x86

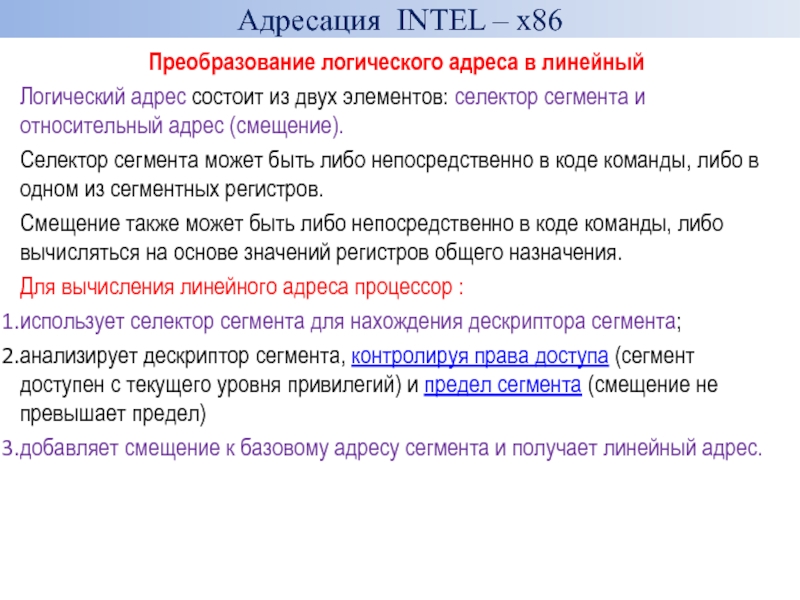

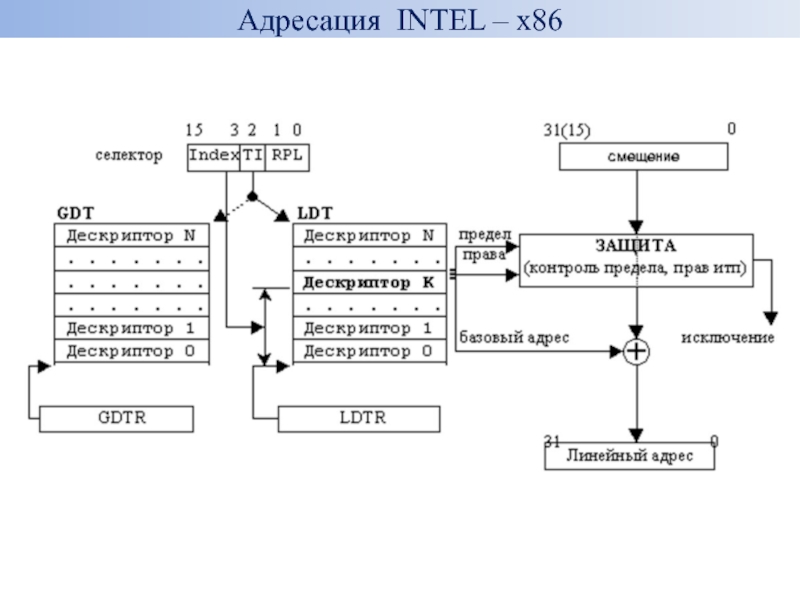

Преобразование логического адреса в линейный

Логический адрес состоит

из двух элементов: селектор сегмента и относительный адрес (смещение).

Селектор

сегмента может быть либо непосредственно в коде команды, либо в одном из сегментных регистров.

Смещение также может быть либо непосредственно в коде команды, либо вычисляться на основе значений регистров общего назначения.

Для вычисления линейного адреса процессор :

использует селектор сегмента для нахождения дескриптора сегмента;

анализирует дескриптор сегмента, контролируя права доступа (сегмент доступен с текущего уровня привилегий) и предел сегмента (смещение не превышает предел)

добавляет смещение к базовому адресу сегмента и получает линейный адрес.

Слайд 55Адресация INTEL – x86

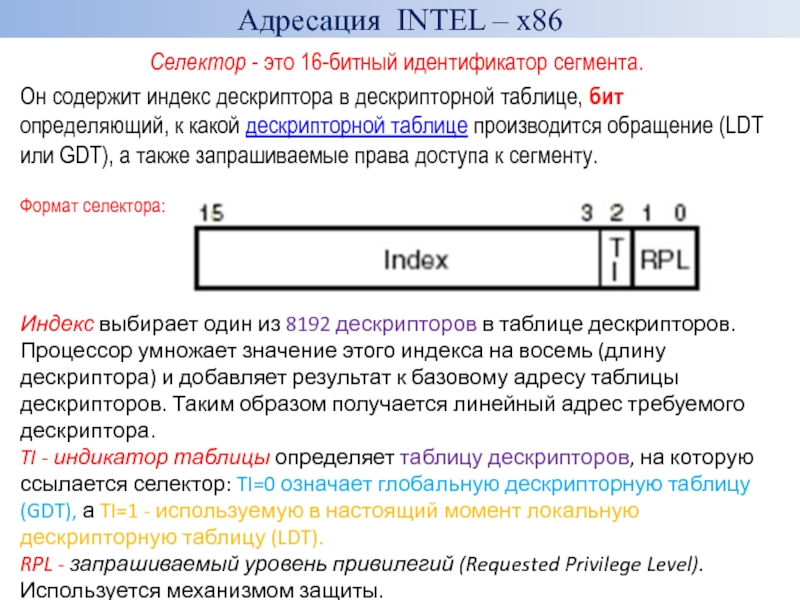

Селектор - это 16-битный идентификатор сегмента.

Он

содержит индекс дескриптора в дескрипторной таблице, бит определяющий, к какой

дескрипторной таблице производится обращение (LDT или GDT), а также запрашиваемые права доступа к сегменту.

Формат селектора:

Индекс выбирает один из 8192 дескрипторов в таблице дескрипторов. Процессор умножает значение этого индекса на восемь (длину дескриптора) и добавляет результат к базовому адресу таблицы дескрипторов. Таким образом получается линейный адрес требуемого дескриптора.

TI - индикатор таблицы определяет таблицу дескрипторов, на которую ссылается селектор: TI=0 означает глобальную дескрипторную таблицу (GDT), а TI=1 - используемую в настоящий момент локальную дескрипторную таблицу (LDT).

RPL - запрашиваемый уровень привилегий (Requested Privilege Level). Используется механизмом защиты.

Слайд 56Адресация INTEL – x86

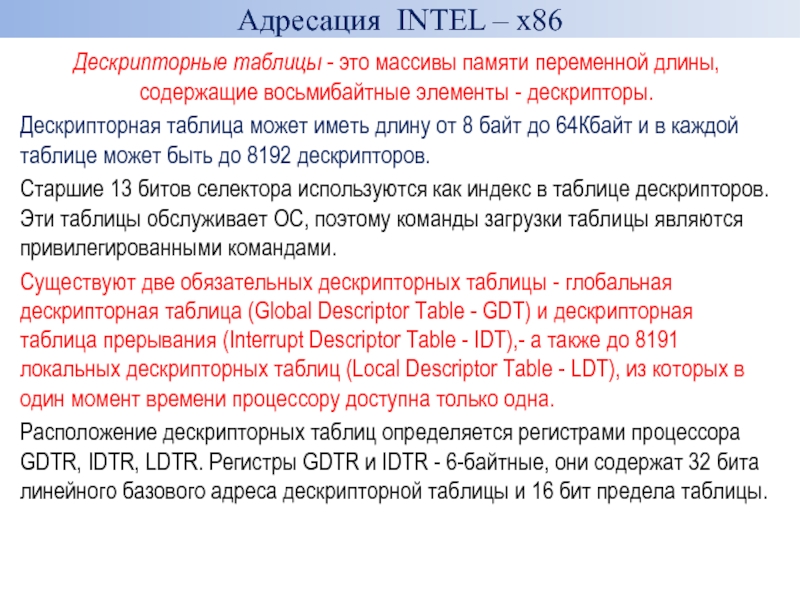

Дескрипторные таблицы - это массивы памяти переменной

длины, содержащие восьмибайтные элементы - дескрипторы.

Дескрипторная таблица может иметь

длину от 8 байт до 64Кбайт и в каждой таблице может быть до 8192 дескрипторов.

Старшие 13 битов селектора используются как индекс в таблице дескрипторов. Эти таблицы обслуживает ОС, поэтому команды загрузки таблицы являются привилегированными командами.

Существуют две обязательных дескрипторных таблицы - глобальная дескрипторная таблица (Global Descriptor Table - GDT) и дескрипторная таблица прерывания (Interrupt Descriptor Table - IDT),- а также до 8191 локальных дескрипторных таблиц (Local Descriptor Table - LDT), из которых в один момент времени процессору доступна только одна.

Расположение дескрипторных таблиц определяется регистрами процессора GDTR, IDTR, LDTR. Регистры GDTR и IDTR - 6-байтные, они содержат 32 бита линейного базового адреса дескрипторной таблицы и 16 бит предела таблицы.

Слайд 57Адресация INTEL – x86

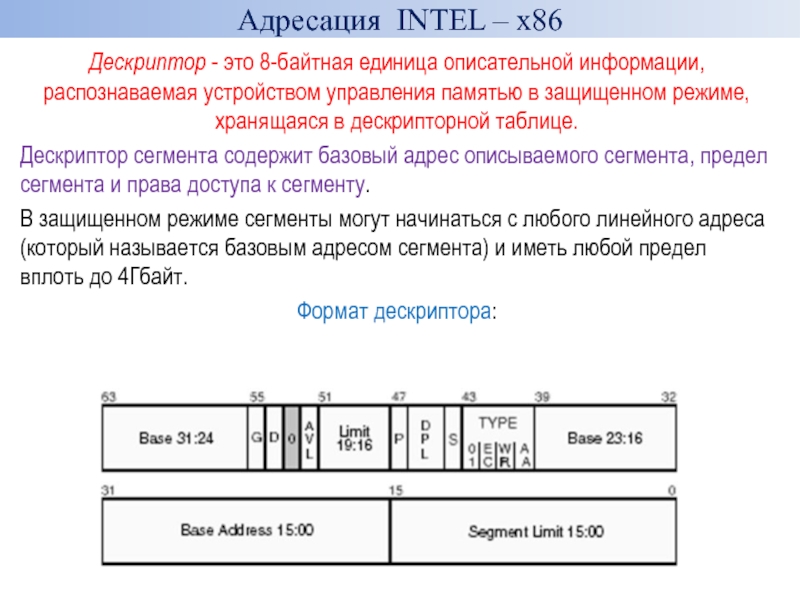

Дескриптор - это 8-байтная единица описательной информации,

распознаваемая устройством управления памятью в защищенном режиме, хранящаяся в дескрипторной

таблице.

Дескриптор сегмента содержит базовый адрес описываемого сегмента, предел сегмента и права доступа к сегменту.

В защищенном режиме сегменты могут начинаться с любого линейного адреса (который называется базовым адресом сегмента) и иметь любой предел вплоть до 4Гбайт.

Формат дескриптора:

Слайд 58Адресация INTEL – x86

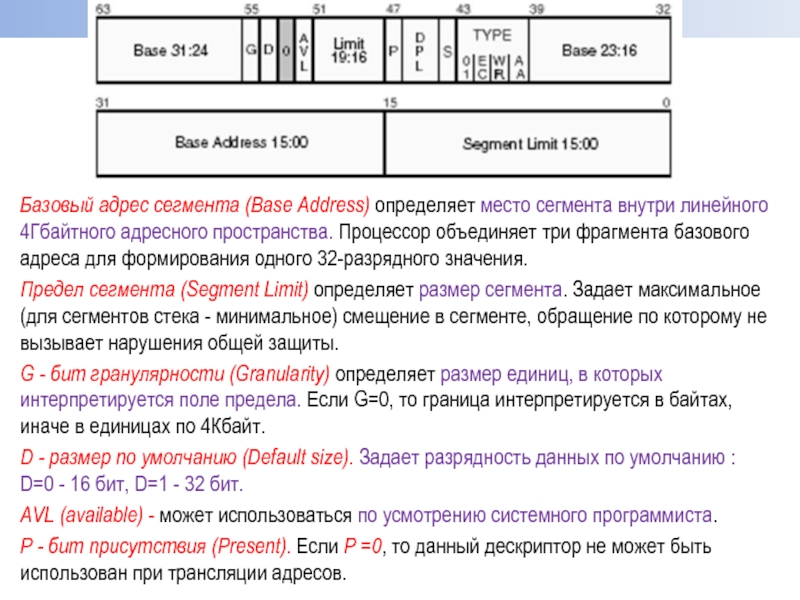

Базовый адрес сегмента (Base Address) определяет место

сегмента внутри линейного 4Гбайтного адресного пространства. Процессор объединяет три фрагмента

базового адреса для формирования одного 32-разрядного значения.

Предел сегмента (Segment Limit) определяет размер сегмента. Задает максимальное (для сегментов стека - минимальное) смещение в сегменте, обращение по которому не вызывает нарушения общей защиты.

G - бит гранулярности (Granularity) определяет размер единиц, в которых интерпретируется поле предела. Если G=0, то граница интерпретируется в байтах, иначе в единицах по 4Кбайт.

D - размер по умолчанию (Default size). Задает разрядность данных по умолчанию : D=0 - 16 бит, D=1 - 32 бит.

AVL (available) - может использоваться по усмотрению системного программиста.

P - бит присутствия (Present). Если P =0, то данный дескриптор не может быть использован при трансляции адресов.

Слайд 59Адресация INTEL – x86

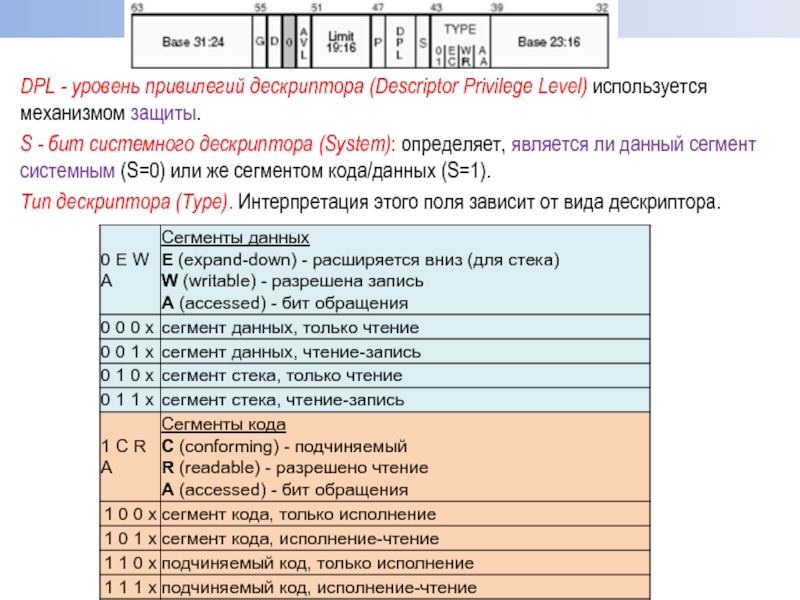

DPL - уровень привилегий дескриптора (Descriptor Privilege

Level) используется механизмом защиты.

S - бит системного дескриптора (System):

определяет, является ли данный сегмент системным (S=0) или же сегментом кода/данных (S=1).

Тип дескриптора (Type). Интерпретация этого поля зависит от вида дескриптора.

Слайд 60Адресация INTEL – x86

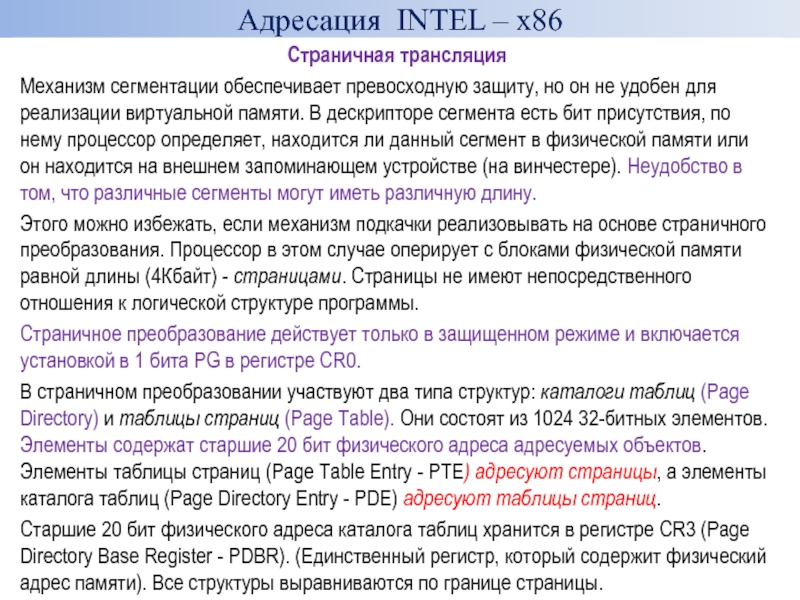

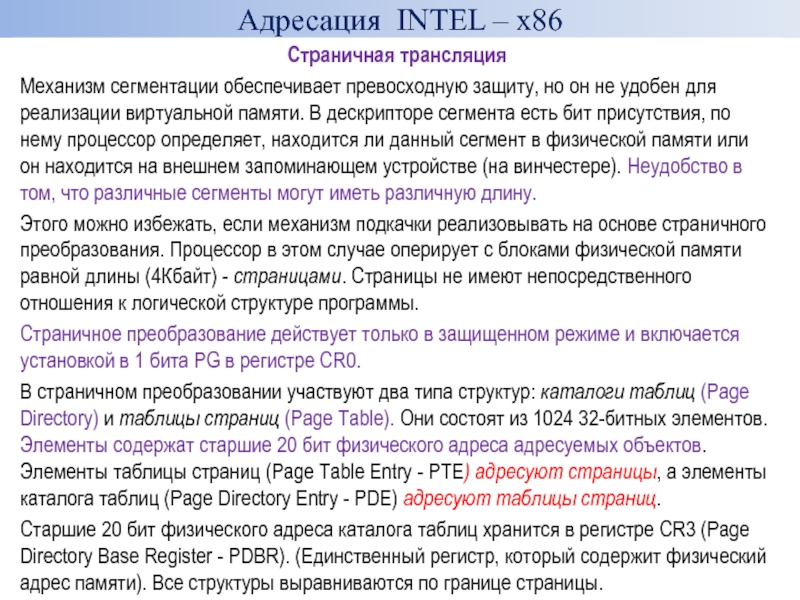

Страничная трансляция

Механизм сегментации обеспечивает превосходную защиту,

но он не удобен для реализации виртуальной памяти. В дескрипторе

сегмента есть бит присутствия, по нему процессор определяет, находится ли данный сегмент в физической памяти или он находится на внешнем запоминающем устройстве (на винчестере). Неудобство в том, что различные сегменты могут иметь различную длину.

Этого можно избежать, если механизм подкачки реализовывать на основе страничного преобразования. Процессор в этом случае оперирует с блоками физической памяти равной длины (4Кбайт) - страницами. Страницы не имеют непосредственного отношения к логической структуре программы.

Страничное преобразование действует только в защищенном режиме и включается установкой в 1 бита PG в регистре CR0.

В страничном преобразовании участвуют два типа структур: каталоги таблиц (Page Directory) и таблицы страниц (Page Table). Они состоят из 1024 32-битных элементов. Элементы содержат старшие 20 бит физического адреса адресуемых объектов. Элементы таблицы страниц (Page Table Entry - PTE) адресуют страницы, а элементы каталога таблиц (Page Directory Entry - PDE) адресуют таблицы страниц.

Старшие 20 бит физического адреса каталога таблиц хранится в регистре CR3 (Page Directory Base Register - PDBR). (Единственный регистр, который содержит физический адрес памяти). Все структуры выравниваются по границе страницы.

Слайд 61Адресация INTEL – x86 Страничная трансляция

При страничной трансляции адресов

линейный адрес разбивается на три части.

Старшие десять бит (Directory)

линейного адреса являются индексом элемента из каталога таблиц. По этому элементу определяется физический адрес таблицы страниц.

Биты 21-12 (Table) линейного адреса выбирают элемент из этой таблицы страниц. Выбранный элемент определяет физический адрес страницы. Младшие 12 бит (Offset) линейного адреса определяют смещение от начала страницы.

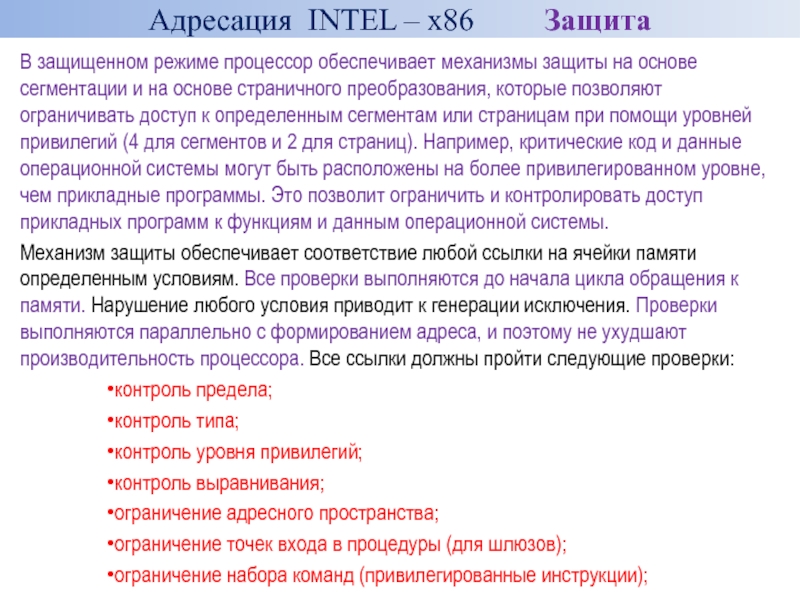

Слайд 62Адресация INTEL – x86 Защита

В защищенном

режиме процессор обеспечивает механизмы защиты на основе сегментации и на

основе страничного преобразования, которые позволяют ограничивать доступ к определенным сегментам или страницам при помощи уровней привилегий (4 для сегментов и 2 для страниц). Например, критические код и данные операционной системы могут быть расположены на более привилегированном уровне, чем прикладные программы. Это позволит ограничить и контролировать доступ прикладных программ к функциям и данным операционной системы.

Механизм защиты обеспечивает соответствие любой ссылки на ячейки памяти определенным условиям. Все проверки выполняются до начала цикла обращения к памяти. Нарушение любого условия приводит к генерации исключения. Проверки выполняются параллельно с формированием адреса, и поэтому не ухудшают производительность процессора. Все ссылки должны пройти следующие проверки:

контроль предела;

контроль типа;

контроль уровня привилегий;

контроль выравнивания;

ограничение адресного пространства;

ограничение точек входа в процедуры (для шлюзов);

ограничение набора команд (привилегированные инструкции);

Слайд 63Адресация INTEL – x86 Защита

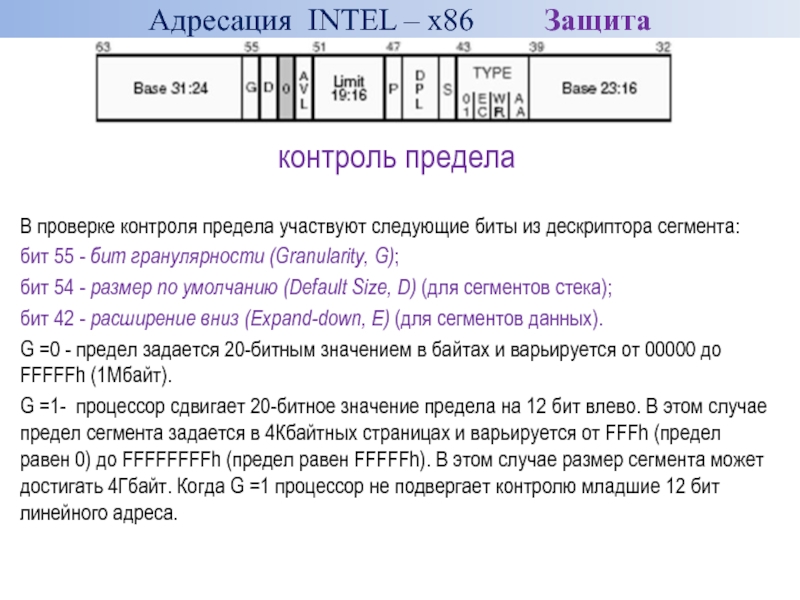

контроль предела

В проверке контроля предела участвуют следующие биты из дескриптора сегмента:

бит 55 - бит гранулярности (Granularity, G);

бит 54 - размер по умолчанию (Default Size, D) (для сегментов стека);

бит 42 - расширение вниз (Expand-down, E) (для сегментов данных).

G =0 - предел задается 20-битным значением в байтах и варьируется от 00000 до FFFFFh (1Мбайт).

G =1- процессор сдвигает 20-битное значение предела на 12 бит влево. В этом случае предел сегмента задается в 4Кбайтных страницах и варьируется от FFFh (предел равен 0) до FFFFFFFFh (предел равен FFFFFh). В этом случае размер сегмента может достигать 4Гбайт. Когда G =1 процессор не подвергает контролю младшие 12 бит линейного адреса.

Слайд 64Адресация INTEL – x86 Защита

Контроль выравнивания

Возможность контроля выравнивания впервые появилась в МП Intel486.

Контроль выравнивания

применим только к ссылкам на сегменты данных (или стека). Контроль выравнивания заключается в следующих проверках:

16-битное слово (например, короткое целое, селектор сегмента) должно храниться по адресу, кратному 2;

32-битное (двойное) слово (например, целое число, вещественное число одинарной точности, 32-битный указатель) должно храниться по адресу, кратному 4;

48-битные дальние указатели и 48-битное содержимое регистров дескрипторных таблиц должны храниться по адресу, кратному 4;

64-битное (четверное) слово (например, вещественное число двойной точности), а также 80-битное вещественное число расширенной точности должны храниться по адресу, кратному 8;

128-битные данные для XMM (Pentium III+) должны храниться по адресу, кратному 16.

Слайд 65Адресация INTEL – x86 Защита

Задача -

это "единица измерения" заданий для процессора, которую процессор может выполнять,

приостанавливать и осуществлять над ней диспетчеризацию.

В качестве задачи может выполняться прикладная программа, сервис операционной системы, ядро операционной системы, обработчик прерывания или исключения и т.п.

В защищенном режиме архитектура IA-32 предоставляет механизм для сохранения состояния задачи и переключения с одной задачи на другую.

Все команды процессора выполняются в контексте той или иной задачи. Даже самые простые системы должны определить как минимум одну задачу. Более сложные системы могут использовать средства управления задачами для поддержки многозадачных приложений.

С точки зрения пользователя, многозадачность - это метод управления компьютерной системой, когда отдельные задачи выполняются так, как если бы они выполнялись параллельно на отдельных процессорах с общей памятью.

Другими словами, за исключением пауз для взаимодействия или синхронизации с другими задачами, каждая задача работает параллельно с другими задачами.

Слайд 66Адресация INTEL – x86 Задача

Задачу составляют

два компонента: адресное пространство задачи и сегмент состояния задачи (Task

State Segment - TSS).

В адресное пространство задачи входят доступные ей сегменты кода, данных и стека.

Сегмент состояния задачи хранит состояние регистров (контекст) процессора:

состояние сегментных регистров (селекторы сегментов, формирующие адресное пространство задачи);

состояние регистров общего назначения;

состояние регистра флагов (EFLAGS);

указатель очередной команды (EIP);

значение регистра CR3 (PDBR);

значение регистра LDTR.

Каждая задача идентифицируется селектором соответствующего ей TSS. Этот селектор загружается в регистр задачи (Task Register - TR) при переключении на задачу. В теневую часть этого регистра загружаются базовый адрес, предел и атрибуты TSS.

Операционная система может предусматривать для каждой задачи свое линейное адресное пространство (свой набор страниц для страничного преобразования), тогда при переключении задачи загружается и регистр CR3 (PDBR), хранящий адрес каталога таблиц для страничного преобразования.

Слайд 67Адресация INTEL – x86

Прерывания и исключения - возникновении в системе

или в выполняемой в данный момент задаче определенных условий, требующих

вмешательства процессора.

Это вынуждает процессор прервать выполнение текущей задачи и передать управление специальной процедуре или задаче, называемой обработчиком прерывания или обработчиком исключения.

Прерывания обычно возникают в произвольный момент времени. Прерывания бывают аппаратурные и программные. Первые генерируются по аппаратному сигналу, поступающему от периферийного оборудования, когда оно требует обслуживания. Программные прерывания генерируются при помощи инструкции INT n.

Исключения - внутренние события процессора - сигнализируют о каких-либо ошибочных условиях при выполнении той или иной инструкции: деление на ноль, нарушение правил защиты, отсутствие страницы и т.п.

При возникновении прерывания или исключения текущая выполняемая задача автоматически приостанавливается на время выполнения обработчика, после чего ее выполнение возобновляется без потери непрерывности выполнения, кроме случаев, когда обработка прерывания или исключения вынуждает завершить программу.

Все прерывания и исключения имеют номер (иногда именуемый вектором) в диапазоне от 0 до 255. Номера 0...31 зарезервированы фирмой Intel для исключений

Слайд 68Адресация INTEL – x86 Прерывания

Процессор определяет

необходимость обработки внешнего прерывания по наличию сигнала на одном из

контактов INTR# или NMI#.

В процессорах Pentium+ эти линии могут быть сконфигурированы на использование APIC (Advanced Programmable Interrupt Controller), тогда они называются LINT0 и LINT1 и информация по ним передается в виде сообщений в специальном формате.

Сигналы на некоторых других контактах процессора также прерывает работу процессора. Однако обработка этих событий отличается от механизма обработки прерываний и исключений. К таким сигналам относятся: RESET# и INIT# (аппаратный сброс), SMI# (переход в режим системного управления) и некоторые другие.

Прерывания, которые генерируются при поступлении сигнала на вход INTR#, называют маскируемыми аппаратными прерываниями. Бит IF в регистре флагов позволяет заблокировать (замаскировать) обработку таких прерываний.

Прерывания, генерируемые сигналом NMI#, называют немаскируемыми аппаратными прерываниями. В процессорах Pentium+ немаскируемое прерывание может быть сгенерировано при получении специального сообщения по шине APIC.

Слайд 69Адресация INTEL – x86 Прерывания

Программные прерывания

С помощью инструкции INT n (n - номер прерывания) можно

сгенерировать прерывание с любым номером 0...255. Такие прерывания называют программными. Состояние бита IF в регистре флагов не влияет на возможность генерации программных прерываний.

Слайд 70Адресация INTEL – x86 Режимы работы

Защищенный

режим (Protected Mode)

Основным режимом работы микропроцессора является защищенный режим.

Ключевыми особенностями защищенного режима являются: виртуальное адресное пространство, защита и многозадачность.

В защищенном режиме программа оперирует адресами, которые могут относиться к физически отсутствующим ячейкам памяти, поэтому такое адресное пространство называется виртуальным.

Размер виртуального адресного пространства программы может превышать емкость физической памяти и достигать 64Тбайт.

Для адресации виртуального адресного пространства используется сегментированная модель, в которой адрес состоит из двух элементов: селектора сегмента и смещения внутри сегмента. С каждым сегментом связана особая структура, хранящая информацию о нем, - дескриптор.

Кроме "виртуализации" памяти на уровне сегментов существует возможность "виртуализации" памяти при помощи страниц - страничная трансляция. Страничная трансляция предоставляет удобные средства для реализации в операционной системе функций подкачки, а кроме того в процессорах P6+ обеспечивает 36-битную физическую адресацию памяти (64Гбайт).

Слайд 71Адресация INTEL – x86 Режимы работы

Встроенные средства переключения задач обеспечивают

многозадачность в защищенном режиме.

Среда задачи состоит из содержимого регистров

МП и всего кода с данными в пространстве памяти.

Микропроцессор способен быстро переключаться из одной среды выполнения в другую, имитируя параллельную работу нескольких задач.

Для некоторых задач может эмулироваться управление памятью как у процессора 8086. Такое состояние задачи называется режимом виртуального 8086 (Virtual 8086 Mode).

Слайд 72Адресация INTEL – x86 Режимы работы

Защита задач обеспечивается

следующими средствами: контроль пределов сегментов, контроль типов сегментов, контроль привилегий,

привилегированные инструкции и защита на уровне страниц.

Контроль пределов и типов сегментов обеспечивает целостность сегментов кода и данных.

Программа не имеет права обращаться к виртуальной памяти, выходящей за предел того или иного сегмента.

Программа не имеет права обращаться к сегменту данных как к коду и наоборот. Архитектура защиты микропроцессора обеспечивает 4 иерархических уровня привилегий, что позволяет ограничить задаче доступ к отдельным сегментам в зависимости от ее текущих привилегий.

Кроме того, текущий уровень привилегий задачи влияет на возможность выполнения тех или иных специфических команд (привилегированных инструкций).

Слайд 73Адресация INTEL – x86 Режимы работы

Реальный режим (Real

Mode)

В реальном режиме микропроцессор работает как очень быстрый 8086

с возможностью использования 32-битных расширений.

Механизм адресации, размеры памяти и обработка прерываний (с их последовательными ограничениями) МП Intel386 в реальном режиме полностью совпадают с аналогичными функциями МП 8086.

Имеется две фиксированные области в памяти, которые резервируются в режиме реальной адресации:

область инициализации системы

область таблицы прерываний

Ячейки от 00000h до 003FFH резервируются для векторов прерываний. Каждое из 256 возможных прерываний имеет зарезервированный 4-байтовый адрес перехода. Ячейки от FFFFFFF0H до FFFFFFFFH резервируются для инициализации системы.

Слайд 74Адресация INTEL – x86 Режимы работы

Режим системного управления

(System Management Mode)

Режим системного управления предназначен для выполнения некоторых

действий с возможностью их полной изоляции от прикладного программного обеспечения и даже операционной системы.

Переход в этот режим возможен только аппаратно. Когда процессор находится в режиме SMM, он выставляет сигнал SMIACT#. Этот сигнал может служить для включения выделенной области физической памяти (System Management RAM), так что память SMRAM можно сделать доступной только для этого режима.

При входе в режим SMM процессор сохраняет свой контекст в SMRAM (контекст сопроцессора не сохраняется) по адресу SMM Base и передает управление процедуре, называемой обработчиком System Management Interrupt, по адресу SMM Base+8000h (по умолчанию SMM Base содержит значение 30000h).

Слайд 75Адресация INTEL – x86 Режимы работы

Переключение между режимами

Слайд 76Организация прерываний

Назначение системы прерываний –реакция на события, внутри и вне

ЭВМ.

Обеспечивается реализацией специальной операции прерывания.

Операция прерывания – прекращение

выполнения текущей программы и переключение процессора на выполнение программы, обслуживающей данную причину прерывания.

После обслуживания прерывания прерванная программа должна быть продолжена, с момента, в котором он была прервана.

Для этого при прерывании программы необходимо сохранить всю информацию, необходимую для его возобновления (состояние процесса).

Эту информацию принято называть вектором состояния процесса. Он включает информацию о состоянии процессора - т.н. слово состояния процессора, признаки результата последней команды – флаги, хранящиеся в специальном регистре признаков (РП), а также значения переменных процесса, которые хранятся в регистрах общего назначения (РОН). Для хранения вектора состояния процесса обычно используют специальную область ОП, организованную как стек.

Слайд 77Организация прерываний

Операция прерывания реализуется аппаратурой ЭВМ и сводится к выполнению

следующих действий:

Выполнение текущей программы прерывается. Прерывание осуществляется как правило по

завершении текущей команды программы.

Выполнение следующей команды не начинается, т.е. она блокируется.

Запоминается информация о состоянии процессора - адрес следующей команды, признаки результата, маски и т. п. информация.

Управление передается специальной программе - обработчику, обслуживающей данную причину прерывания. Она выполняет все действия, необходимые для обработки прерывания.

Слайд 78Организация прерываний

Типовая структура программы обработчики прерывания включает следующий пункты:

преостановка выполняемой

программы по сигналу прерывания;

сохранение используемых прерванной программой РОН и

информации о текущем состояния процессора (регистр РП) в ОП;

собственно обработка прерывания соответствующей программой;

восстановление РОН и сохраненной информации о состоянии процессора из ОП;

возобновление выполнения прерванной программы.

Слайд 79Организация прерываний

Процесс прерывания запускается либо по сигналам прерывания, либо по

командам прерывания (для IBM PC это команда INT N, где

N - номер прерывания).

Причины, по которым формируются сигналы прерываний, различны и делятся на внутренние и внешние.

Внешние причины – это события, которые возникают вне ЭВМ, (например во внешних устройствах), в другой ЭВМ, подключенной к данной, сигналы времени от таймера и т.п.

Внутренние причины – это события, которые происходят внутри ЭВМ. Их можно разделить на два типа:

причины, при возникновении которых продолжение вычислительного процесса становится невозможным, или бессмысленным (переполнение, неправильный код, неправильный адрес и т.д.);

причины нормальные, естественные для вычислительного процесса (процессы ввода/вывода обычно используют прерывания, обращение к системным ресурсам).

Слайд 80Организация прерываний

Сигналы прерываний от устройств ввода/вывода вырабатываются при готовности устройства

к обмену информацией.

По этому сигналу прерывания прерывается текущая программа

и запускается специальная программа-обработчик, которая обеспечивает обмен информацией между регистром данных или буферной памятью УВВ и ячейками ОП или регистрами процессора (РОН). Этот способ ввода-вывода используется обычно для обслуживания ВУ (принтера, клавиатуры и т.п.).

Прерывания при обращениях к сервисным программам ОС обычно осуществляются по специальным командам прерываний.

В IBM PC для этих целей можно использовать специальную команду прерывания типа INT N, которая встраивается в пользовательскую программу в нужных местах.

Эту группу причин прерываний принято называть программными прерываниями.

Слайд 81Организация прерываний

Обслуживание прерываний

Может возникнуть ситуация, когда прерывание от ВУ

повредит выполнению основной программы.

Для предотвращения этого процессор может обладать

системой защиты от прерываний, которая позволяет регулировать обработку сигналов прерывания.

Процессор может обрабатывать прерывания

сразу по приходу прерывания,

откладывать их обработку на некоторое время,

полностью игнорировать используя механизм маскирования прерываний.

Обычно операции прерывания выполняются только после завершения выполнения текущей команды.

Слайд 82Организация прерываний

Возможна другая ситуация, когда во время обработки одного прерывания

поступит сигнал прерывания от другого или нескольких других устройств.

Существуют

два способа решения данной проблемы:

Первый – проводить прерывания в той последовательности, в которой приходят сигналы. Но это может привести к сбою в работе устройств, которые не могут долго простаивать.

Второй - в присвоении каждому периферийному устройству определенного номера приоритета и использовать систему приоритетных прерываний, которая будет следить, что бы прерывания с более высоким приоритетом выполнялись раньше, чем с низким.

Существует две разновидности приоритета – относительный и абсолютный.

При относительном более высокий приоритет не может прервать уже работающий более низкий, а при абсолютном - может.

Слайд 83Организация прерываний

Маскирование прерывания. Приоритет прерывания.

ЭВМ должна иметь средства, позволяющие

избирательно реагировать на различные сигналы прерывания.

Например, если пришел сигнал

прерывания от одной из схем контроля, которая обнаружила факт отказа аппаратуры, то нет необходимости реагировать на другие сигналы прерываний, например, на переполнение разрядной сетки, до тех пор, пока неисправность аппаратуры не будет устранена.

Для этих целей используется маска прерываний – двоичный код М = m1... mk, в котором каждой причине прерывания ставится в соответствие бит маски mi.

Если, например, бит маски mi = 0, то прерывание по i - й причине запрещено, т.е. замаскировано.

Если mi = 1, то прерывание разрешено, т.е. не замаскировано.

Таким образом, операция прерывания инициализируется только незамаскированным сигналом прерывания.

Слайд 84Организация прерываний

Для исключения конфликтной ситуации сигналам прерываний присваиваются различные приоритеты.

Приоритет – это преимущественное право на обслуживание – привилегия в

обслуживании.

Назначение приоритетов осуществляется исходя, например, из динамики процессов: быстропротекающим процессам назначают более высокие приоритеты.

Например, исходя из уровня некорректностей: некорректность в аппаратуре (отказ) в отличие от некорректности в программе необходимо обслуживать в первую очередь.

Некорректную программу можно снять со счета и начать обслуживать другую программу.

Отказ же аппаратуры делает невозможным выполнение любой программы. Поэтому реакция на отказ должна иметь преимущества перед программными некорректностями и другими причинами прерываний.

Слайд 85Организация прерываний

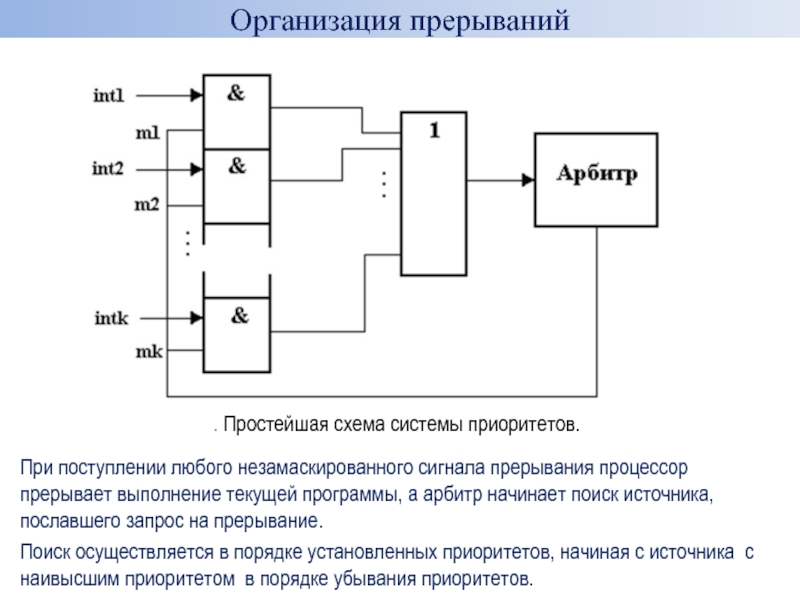

. Простейшая схема системы приоритетов.

При поступлении любого незамаскированного сигнала

прерывания процессор прерывает выполнение текущей программы, а арбитр начинает поиск

источника, пославшего запрос на прерывание.

Поиск осуществляется в порядке установленных приоритетов, начиная с источника с наивысшим приоритетом в порядке убывания приоритетов.

Слайд 86Организация прерываний

Существует две схемы поведения систем приоритетных прерываний относительно возможности

прерывания одной обрабатывающей программы другой.

Первая - обслуживание по схеме

с относительными приоритетами (ОПР).

Вторая – обслуживание по схеме с абсолютными приоритетами (АПР).

Слайд 87Организация прерываний

В случае ОПР приоритет, который присваивается сигналу прерывания, относителен,

т.е. действует не всегда, а только в момент одновременного поступления

нескольких запросов прерываний.

Если высокоприоритетный сигнал поступил позже сигнала с более низким приоритетом, то обслуживание этого более низкоприоритетного сигнала не может быть прервано сигналом с более высоким приоритетом, т.е. осуществляется без прерывания до завершения и только потом начинается обслуживание запроса с более высоким приоритетом.

Этот механизм обеспечивается путем маскирования сигналов прерываний от других устройств на время обслуживания.

В случае АПР приоритет абсолютен и действует всегда, вызывая прерывание программ с более низкими приоритетами.

Системы прерываний с ОПР имеет глубину прерываний 1,

Системы прерываний с АПР – глубину прерываний больше 1: 2,3, . . . (вложенные прерывания).

Время ответа (реакции) систем прерывания с АПР как правило меньше, чем систем прерывания с ОПР.

Слайд 88Организация прерываний

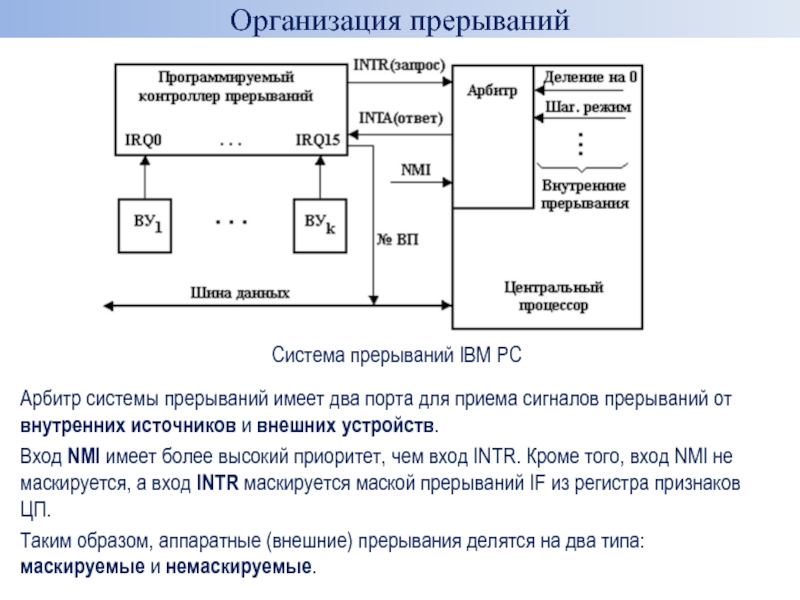

Система прерываний IBM PC

Арбитр системы прерываний имеет два порта

для приема сигналов прерываний от внутренних источников и внешних устройств.

Вход NMI имеет более высокий приоритет, чем вход INTR. Кроме того, вход NMI не маскируется, а вход INTR маскируется маской прерываний IF из регистра признаков ЦП.

Таким образом, аппаратные (внешние) прерывания делятся на два типа: маскируемые и немаскируемые.

Слайд 89Организация прерываний

Внутренние прерывания.

Прерывания типа отказ (fault) –наступает в случаях,

когда в результате различных некорректностей невозможно нормальное выполнение команды –

прерывание наступает до выполнения команды.

Прерывание «ловушка» (trap) –наступает в результате выполнения команды, например, команды прерывания INT N.

Прерывание «аварийное завершение команды» (abort) из-за ошибки аппаратуры. Этот тип прерываний не маскируется.

Слайд 90Организация прерываний

Обслуживание прерываний производится следующим образом.

В стек заталкивается адрес

следующей команды: CS (базовый адрес) , IP (смещение) (2 слова)

и регистр флагов RF (третье слово) и сбрасываются биты IF=0, TF=0 в регистре RF процессора ЦП.

Затем по номеру вектора прерывания (ВП) N, полученному от внешнего устройства или сгенерированному внутри ЦП, из ОП извлекается ВП.

Адрес ВП формируется следующим образом: АВП = 4 x N.

По нему из ОП извлекаются два слова адреса обработчика, которые загружаются в регистр CS и IP. По ним выбирается первая команда программы обработки прерывания.

В конце программы-обработчика ставится команда IRET – возврат из прерывания, по которой из стека выталкиваются два слова адреса возврата к прерванной программе и загружаются в CS и IP, и третье слово - в регистр RF.

В компьютере PC каждой причине прерывания ставится в соответствие свой номер ВП (тип прерывания). Например, деление на 0 имеет ВП с номером 0 (тип 0).

Слайд 91Организация прерываний

Всего в IBM PC используется 256 ВП с номерами

от 0 до 255 (от 0 до FFh).

Все ВП

располагаются в сегменте данных, начиная с 0 адреса,

Адрес ВП кратен 4.

Запросом на прерывание NMI является положительный перепад сигнала на входе .

Запрос по входу NMI обслуживается ВП с номером 2 (тип 2).

Обслуживание прерывания по входу NMI осуществляется без прерывания обрабатывающей программы, т.е. по схеме с относительным приоритетом,.

Запрос на прерывание на входе INTR - сигнал высокого уровня.

По этому сигналу арбитр заталкивает в стек содержимое регистров IP, CS, RF и вырабатывает ответный сигнал INTA.

Получив INTA, программируемый контроллер прерываний сбрасывает сигнал на входе INTR и посылает по шине данных в процессор номер ВП, соответствующий причине прерывания с наивысшим в данный момент времени приоритетом (IRQi).

![Архитектура системы команд

12.03.2014

1

Н. В. Горбунов

Системой команд ЭВМ Адресация INTEL – x86Базовый Эффективный адрес равен сумме содержимого базового регистра Адресация INTEL – x86Базовый Эффективный адрес равен сумме содержимого базового регистра и непосредственного смещения:ADD AX,[BP+10h] AX = 0067h BP](/img/thumbs/7aba33fb4ee5800e4bbcb8f8ab1021ea-800x.jpg)

![Архитектура системы команд

12.03.2014

1

Н. В. Горбунов

Системой команд ЭВМ Адресация INTEL – x86БАЗОВО-ИНДЕКСНАЯ АДРЕСАЦИЯ СО СМЕЩЕНИЕМ И МАСШТАБИРОВАНИЕМ примерИнструкция INC [EAX+EDI*4+12345678h] Адресация INTEL – x86БАЗОВО-ИНДЕКСНАЯ АДРЕСАЦИЯ СО СМЕЩЕНИЕМ И МАСШТАБИРОВАНИЕМ примерИнструкция INC [EAX+EDI*4+12345678h] увеличит на единицу число,адрес которого вычисляется,](/img/thumbs/608691ccf29b70ea5b1bf0af5a301512-800x.jpg)