Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Архитектура ЭВМ и систем

Содержание

- 1. Архитектура ЭВМ и систем

- 2. Цель дисциплиныЦелью дисциплины «Архитектура ЭВМ и систем»

- 3. Задачи изучения дисциплины изучение принципов создания автоматизированных

- 4. Задачи изучения дисциплины изучение устройства основных компонент

- 5. Студент должен иметь представление об информатике как

- 6. Студент должен знатьпоказатели качества информации;понятие системы обработки

- 7. Студент должен знатьпорядок адресации данных в оперативной

- 8. Студент должен знатьвиды ИВС и топологии их

- 9. Студент должен уметь:определять тип и класс ЭВМ

- 10. Студент должен приобрести навыки:использования системного подхода применительно

- 11. Тема 1ЭВМ как средство обработки информации: основные характеристики информационно-вычислительных систем

- 12. Учебные вопросы:Назначение ЭВМ. Представление информации в ЭВМ.

- 13. ВведениеРазвитие Вычислительной Техники (ВТ) обусловлено успехами в

- 14. АрхитектураВ процессе работы ВМ все ее компоненты

- 15. Обобщенная структура ЭВМПринцип действия обычной ВМ можно

- 16. Архитектура

- 17. АлгоритмВ основе функционирования любой ВМ лежат два

- 18. АлгоритмАлгоритм - некоторая однозначно определенная последовательность действий,

- 19. ПрограммаПрограмма – описание алгоритма на каком-либо языке.Принцип

- 20. Архитектурно-функциональные принципыППУ включает в себя несколько архитектурно

- 21. Назначение ЭВМЭВМ обладает способностью собирать и хранить

- 22. Представление информации в ЭВМЛюбая информация, поступающая в

- 23. Показатели качества информацииВозможность и эффективность использования информации

- 24. Показатели качестваРепрезентативность информации связана с правильностью ее

- 25. Показатели качестваСвоевременность информации определяется возможностью ее использования

- 26. Информатика как технология, сфера народного хозяйства и

- 27. ИнформатикаИнформатика изучает свойства, структуру и функции информационных

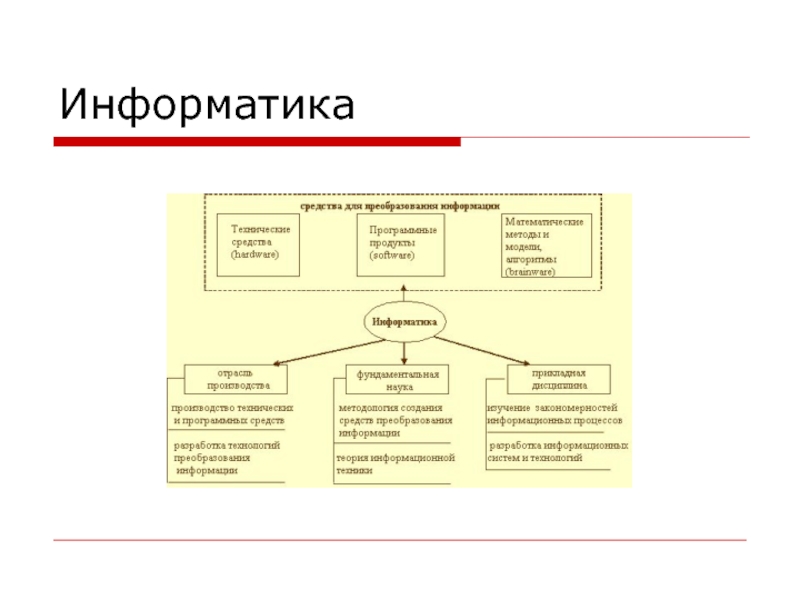

- 28. ИНформатикаИнформатика как наука объединяет группу дисциплин, занимающихся

- 29. ИнформатикаИнформатика как индустрия — это инфраструктурная отрасль

- 30. ИнформатикаРоль информатики в современных условиях постоянно возрастает.

- 31. Информатика

- 32. Систематизация процесса обработки информации - информационные системы

- 33. Систематизация процесса обработки информации - информационные системы

- 34. Систематизация процесса обработки информации - информационные системы (ИС), их структура и классификация

- 35. Систематизация процесса обработки информации - информационные системы

- 36. Систематизация процесса обработки информации - информационные системы

- 37. Взаимосвязь понятий "информатика", "информация", "система", "информационно-вычислительная система"самостоятельно

- 38. Информационно-вычислительные системы (ИВС) как логическое развитие информационных системсамостоятельно

- 39. Классификация, состав и функции ИВСКлассификация по принципам:по территориальностипо организация передачи данныхпо геометрии

- 40. Поколения ЭВМПервое (ламповые, начало 50-х)Второе (транзисторные 60-е)Третье

- 41. Первое поколениеЛамповые ЭВМ, промышленный выпуск начат в

- 42. Второе поколениеСвязывают с переходом от ламповых к

- 43. Архитектура второго поколения

- 44. Второе поколениеНачинается бурное развитие математического и программного

- 45. Третье поколениеВ конце 60-х годов появляются первые

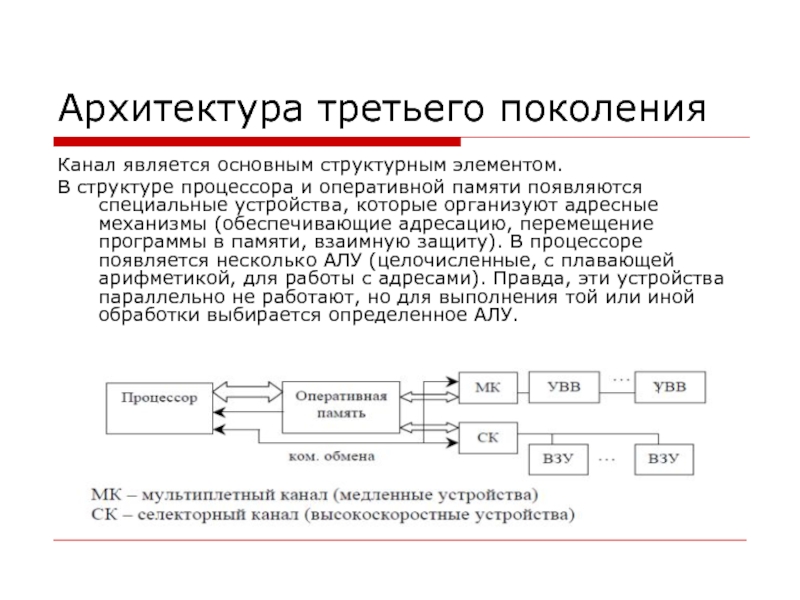

- 46. Архитектура третьего поколенияКанал является основным структурным элементом.В

- 47. Третье поколениеВ памяти четко выделяется основная память,

- 48. Четвертое поколениеВ конце 70-х кодов появляются первые

- 49. Технические характеристики 4-го поколенияСредняя задержка сигнала 0.7

- 50. Пятое поколениеВ конце 80-х годов появляются первые

- 51. Современные тенденцииВ этот период существуют две диаметрально противоположных тенденции:Персонификация ресурсовКоллективизация ресурсов (коллективный доступ – сети)

- 52. Шестое поколениеОптоэлектронные ЭВМ с массовым параллелизмом и

- 53. Эволюция ЭВМ и вычислительных систем (ВС)История ВТ

- 54. Первая настоящая ЭВМФизически первая цифровая ВМ была

- 55. ХарактеристикиХарактеристики ВМ (работали с 23 разрядными десятичными

- 56. Адамы современных ЭВМПервая ЭВМ, разработанная на электронных

- 57. Тема 2Области применения и архитектурные особенности ЭВМ различных классов

- 58. Учебные вопросы:Характеристика семейств ЭВМ.Требования к ИВС, определяющие

- 59. Характеристики семейств ЭВМОперационные ресурсы ЭВМЕмкость памятиБыстродействие ЭВМНадежность ЭВМПоказатель стоимости

- 60. Операционные ресурсы ЭВМОперационные ресурсы ЭВМ – это

- 61. Емкость памятиЕмкость памяти (внешняя и основная) Основная

- 62. Быстродействие ЭВМБыстродействие ЭВМ характеризует скорость обработки информации

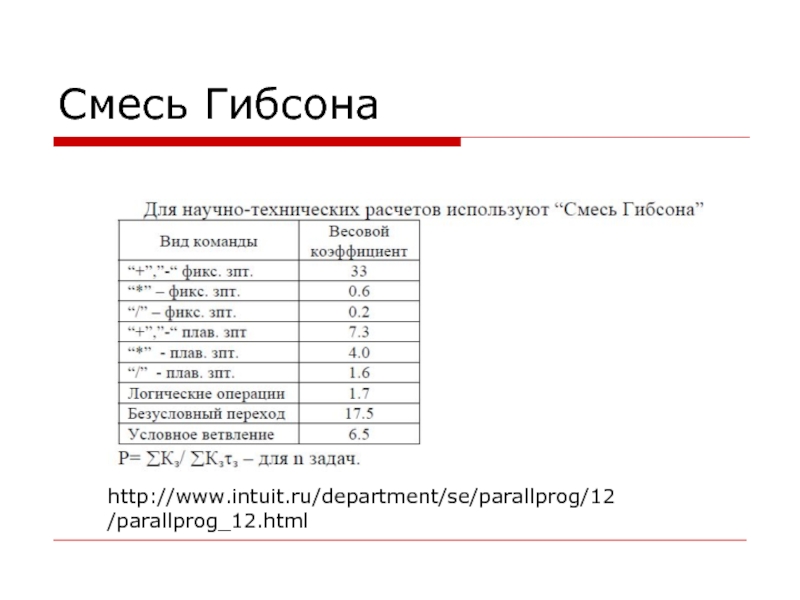

- 63. Смесь Гибсонаhttp://www.intuit.ru/department/se/parallprog/12/parallprog_12.html

- 64. Надежность ЭВМ.Надежность – свойство ЭВМ выполнять возложенные

- 65. ОтказыПо характеру проявлений отказы могут быть:1. Внезапный

- 66. Показатель стоимостиПоказатель стоимости – суммарная стоимость всего

- 67. ВыводВывод, если не менять технологическую базу компьютеров,

- 68. График стоимости

- 69. Классификация ЭВМЭВМ классифицируются по:Назначению.Принципу действияПо размерам и функциональным возможностям Способу структурной организацииПроизводительности.Режимам работы

- 70. По назначениюуниверсальные (общего назначения) — предназначены для

- 71. По принципу действияаналоговые вычислительные машины (АВМ) —

- 72. По размерам и функциональным возможностям Большие ЭВМ Малые ЭВМ Супер ЭВММикро ЭВМ или персональный компьютерСпециальные ЭВМ

- 73. Большие ЭВМ Исторически первыми появились большие ЭВМ,

- 74. Малые ЭВМ Малые (мини) ЭВМ — надежные,

- 75. Супер ЭВМ Это мощные многопроцессорные ЭВМ с

- 76. Микро ЭВМ или персональный компьютер ПК должен

- 77. Термины микроЭВМС понятием микроЭВМ связаны также термины:Однокристальная

- 78. Специальные ЭВМ Специальные ЭВМ ориентированы на решение специальных

- 79. Альтернативная классификацияБазовая ЭВМ [original computer ] - ЭВМ, являющаяся

- 80. Альтернативная классификацияУправляющая ЭВМ [control computer ] - ЭВМ, предназначенная

- 81. Способ структурной организацииДля увеличения скорости ЭВМ в

- 82. По режиму и месту работыАктивная ЭВМ [active computer ]

- 83. По функциям , выполняемым в многомашинных системах ( комплексах ) Главная ( ведущая , центральная ) ЭВМ , ГВМ , хост[master (host, central) computer] -В

- 84. Виды серверов 1Почтовый сервер [mail server] - Сервер, обеспечивающий

- 85. Виды серверов 2Сервер ( станция ) связи [gateway server ] - Специализированный узел

- 86. Виды серверов 3Файловый сервер , файл-сервер [file server] - Сервер, управляющий

- 87. Виды серверов 4Телефонный сервер API [TSAPI - Telephony Server Application

- 88. Виды серверов 5Псевдо-УАТС, телефонный телекоммуникационный сервер, –

- 89. Виды серверов 6Хост-узел [host ] - Отдельная ЭВМ или

- 90. Требования к ИВС, определяющие класс используемых ЭВМСтруктура

- 91. Масштабируемость ИВСМасштабируемость – это способность (свойство) системы

- 92. МасштабируемостьВертикальная масштабируемость Увеличение производительности каждого компонента системы

- 93. Совместимость и мобильность программного обеспеченияСовместимость программного обеспечения

- 94. Классификация персональных компьютеров (ПК)По конструктивным особенностям можно классифицировать ПК так:Стационарные (настольные)Переносимые:портативныеблокнотыкарманныеэлектронные секретариэлектронные записные книжки

- 95. Понятие о суперЭВМ, мини- и микроЭВМ, особенности

- 96. Понятие о суперЭВМ, мини- и микроЭВМ, особенности

- 97. Понятие о суперЭВМ, мини- и микроЭВМ, особенности

- 98. Понятие о суперЭВМ, мини- и микроЭВМ, особенности

- 99. Основные области и формы использования ЭВМ различных классовсамостоятельно

- 100. Тема 3Основные принципы построения ЭВМ и вычислительных систем

- 101. Учебные вопросы:Обобщенная структурная схема ЭВМ.Состав устройств, их

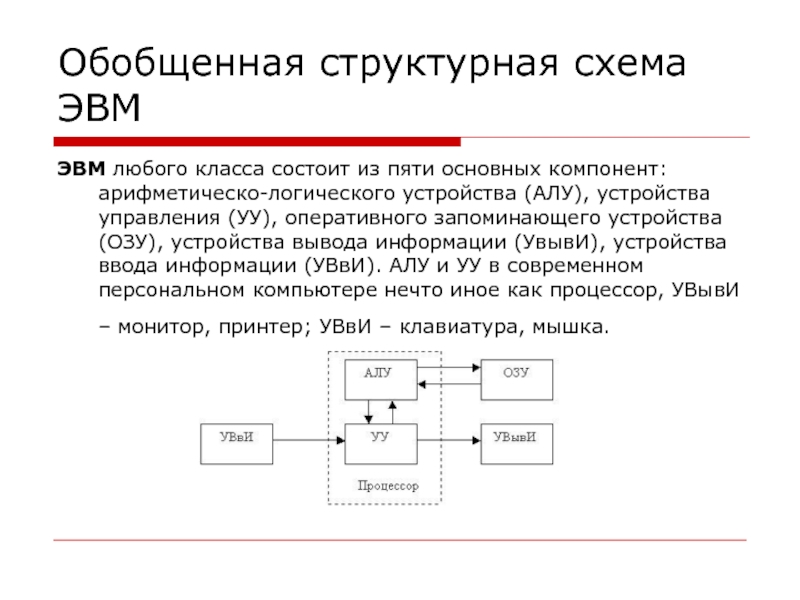

- 102. Обобщенная структурная схема ЭВМЭВМ любого класса состоит

- 103. Состав устройств, их назначение и взаимодействие

- 104. Принцип программного управленияОсновным принципом построения всех современных

- 105. Фон-Неймановская архитектура ЭВМСтруктурная схема ЭВМ по фон Нейману

- 106. Фон-Неймановская архитектура ЭВМПроцессор выполняет логические и арифметические

- 107. Фон-Неймановская архитектура ЭВМ (2)В постоянном запоминающем устройстве

- 108. Последовательность прохождения информации при обработке на ЭВМСм . два слайда назад

- 109. Принципы создания элементов структур современных ЭВМ: модульность

- 110. Тема 4Функциональная и структурная организация ЭВМ и ВС, периферийные устройства, организация ввода-вывода

- 111. Учебные вопросы:Общие принципы функциональной и структурной организации

- 112. Общие принципы функциональной и структурной организации современных

- 113. Общие принципы функциональной и структурной организации современных

- 114. Организация функционирования ЭВМ с магистральной архитектурой1 шаг:

- 115. Организация функционирования ЭВМ с магистральной архитектурой4 шаг:

- 116. Организация функционирования ЭВМ с магистральной архитектурой6 шаг:

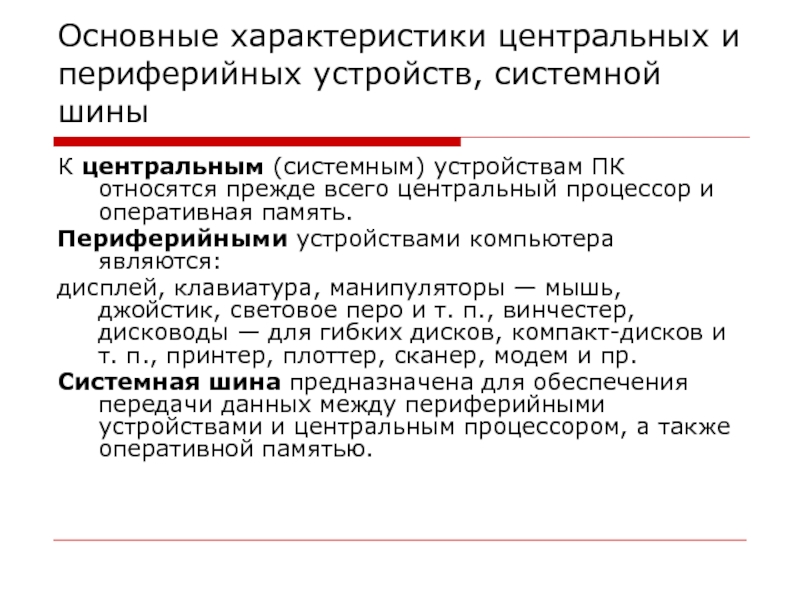

- 117. Основные характеристики центральных и периферийных устройств, системной

- 118. Взаимодействие центральных и периферийных устройств, организация ввода-вывода

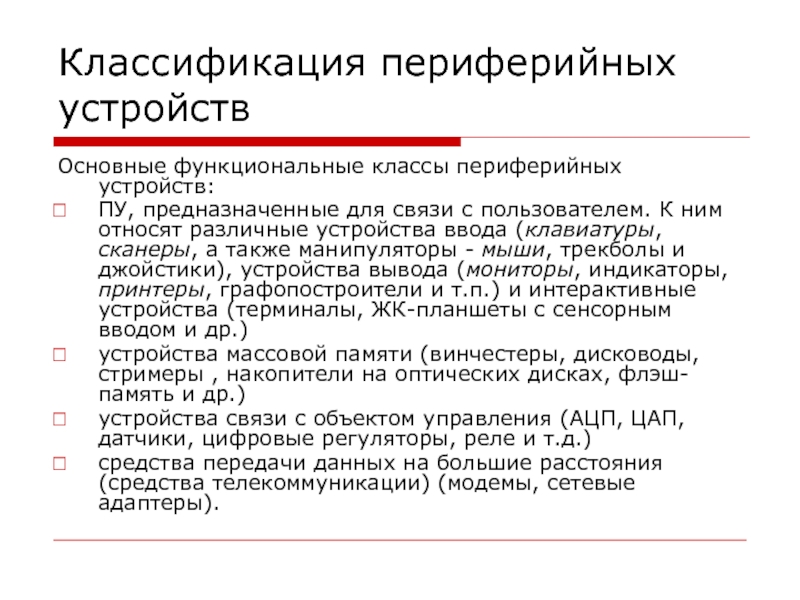

- 119. Классификация периферийных устройствОсновные функциональные классы периферийных устройств:ПУ,

- 120. Структурная организация и взаимодействие узлов и устройств ЭВМ при выполнении основных команд ЭВМИнтернет

- 121. Системы адресацииСистемы адресации используемые в мини-ЭВМ (11

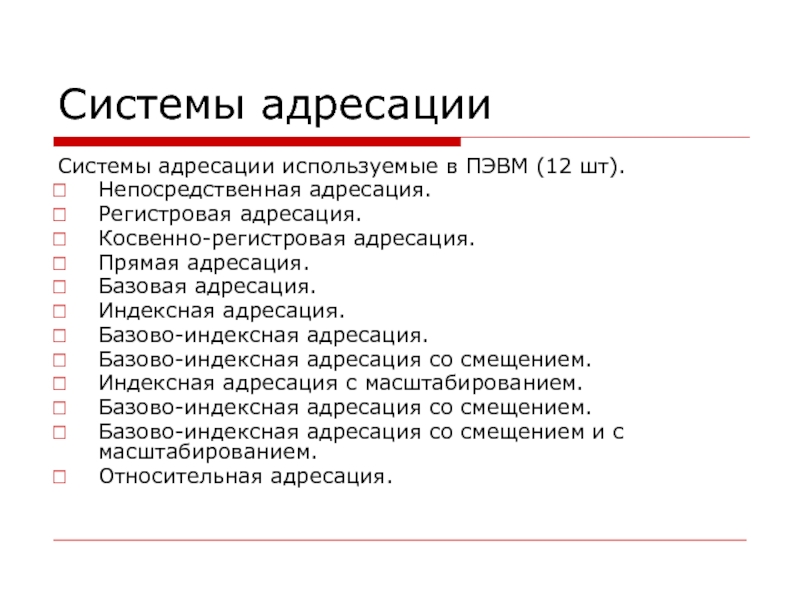

- 122. Системы адресацииСистемы адресации используемые в ПЭВМ (12

- 123. АдресацияНепосредственная IMUL AX,5 Регистровая PUSH DS Косвенно-регистровая

- 124. Технология выполнения основных команд ЭВМКоманда ЭВМ обычно состоит из двух частей - операционной и адресной

- 125. Тема 5Функциональная и структурная организация процессора, микропроцессоры для IMB-совместимых ПЭВМ

- 126. Учебные вопросы:Назначение и структура центрального процессора (ЦП),

- 127. Назначение и структура центрального процессора (ЦП), состав

- 128. Центральное устройство управления (УУ)Устройство управления организует процесс

- 129. Арифметико-логическое устройство (АЛУ): назначение, основные характеристики, обобщенная

- 130. Арифметико-логическое устройство (АЛУ): назначение, основные характеристики, обобщенная

- 131. Арифметико-логическое устройство (АЛУ): назначениеАрифметико-логическое устройство (АЛУ) -

- 132. Арифметико-логическое устройство (АЛУ): основные характеристикиАЛУ состоит из

- 133. Арифметико-логическое устройство (АЛУ): обобщенная структурная схема

- 134. Структурная схема АЛУСтруктурная схема АЛУ и его

- 135. Альтернативная структурная схема АЛУ

- 136. Предыдущий слайд – ШУТКА, не имеющая отношения к АЛУ.

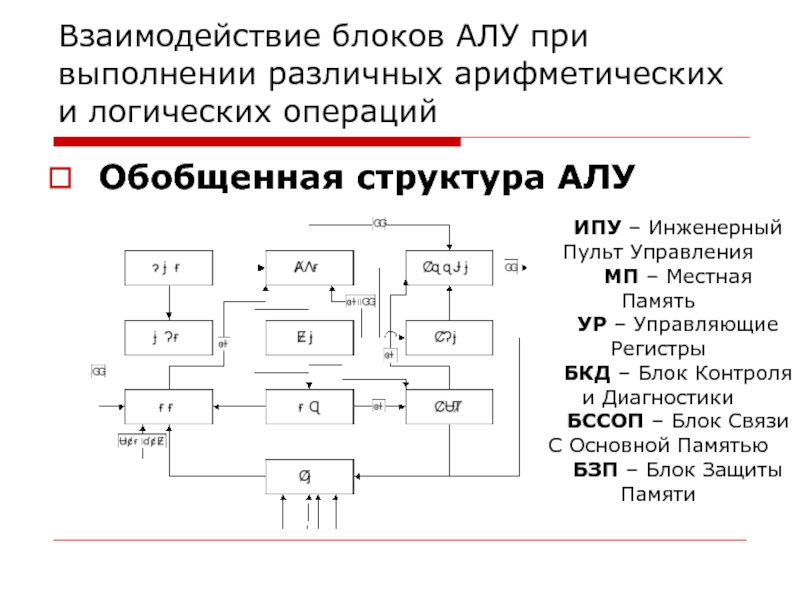

- 137. Взаимодействие блоков АЛУ при выполнении различных арифметических

- 138. Центральное Устройство Управления ЦУУ формирует управляющие сигналы

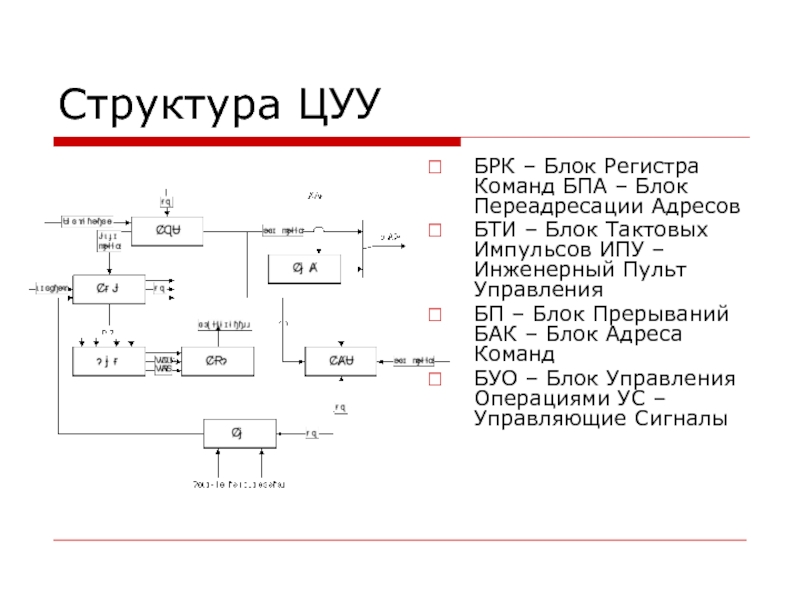

- 139. Структура ЦУУ БРК – Блок Регистра Команд

- 140. ЦУУАлгоритм: 1)код очередной команды программы принимается для

- 141. АЛУНазначение – обработка информации (операции +, -,

- 142. АЛУ (2)1) Регистры для хранения кодов операндов

- 143. АЛУ 3Алгоритм работы: 1) перед суммированием по

- 144. Назначение и классификация АЛУ Типы АЛУ: используемая

- 145. АЛУ с непосредственными связямиПринцип организации АЛУ с

- 146. АЛУ магистральной структуры Схемы для преобразования информации

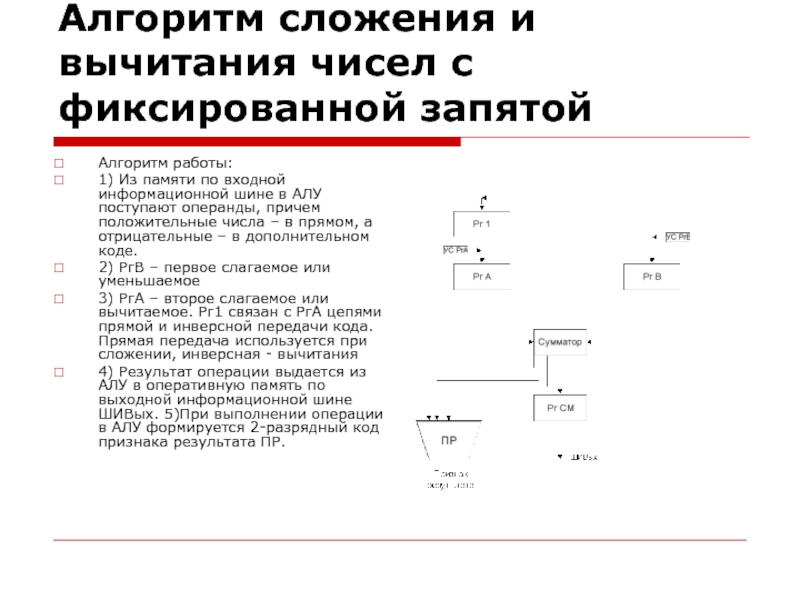

- 147. Структура АЛУ для сложения и вычитания чисел

- 148. Алгоритм сложения и вычитания чисел с фиксированной

- 149. Алгоритм сложения и вычитания чисел с фиксированной

- 150. Структура АЛУ для умножения чисел с фиксированной

- 151. умножение чисел с фиксированной запятой Для выполнения

- 152. Архитектура и микроархитектура процессораАрхитектура процессора ПК определяется

- 153. Список команд МПСистема команд – список всех командных

- 154. RISC- и CISC-процессоры, их использование в ПЭВМ

- 155. CISCCISC (Complete Instruction Set Computer) – полный набор

- 156. CISCДля CISC-процессоров характерно:сравнительно небольшое число регистров общего

- 157. RISCМикропроцессоры с архитектурой RISC (Reduced Instruction Set

- 158. RISCДейв Паттерсон и Карло Секуин сформулировали 4

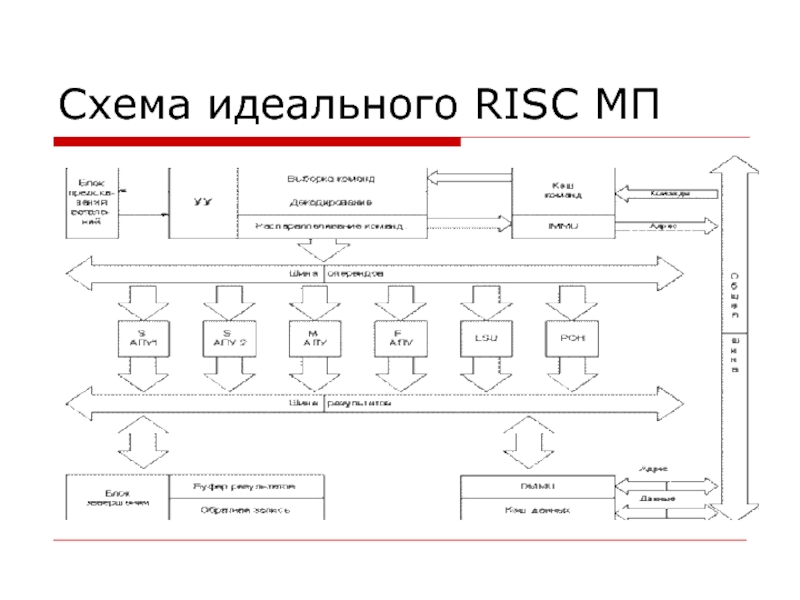

- 159. Схема идеального RISC МП

- 160. CISC против RISCПринципиально новое, что отличает RISC-

- 161. Структура базового микропроцессора (МП) современных моделей для IMB-совместимых ПЭВМ, взаимодействие его узлов и блоковсамостоятельно

- 162. Параметры микропроцессоровразрядность; рабочая тактовая частота; размер кэш-памяти; состав инструкций; конструктив; рабочее напряжение и т. д.

- 163. Параметры микропроцессоровРазрядность шины данных микропроцессора определяет количество

- 164. Параметры микропроцессоровСостав инструкций -- перечень, вид и

- 165. Кэш-памятьКэш – память Это статическая память (Statiс

- 166. КонвейеризацияСущественное повышение производительности МП 80286 по сравнению

- 167. Конвейеризация в 286 Конвейеризация команд в МП 80286

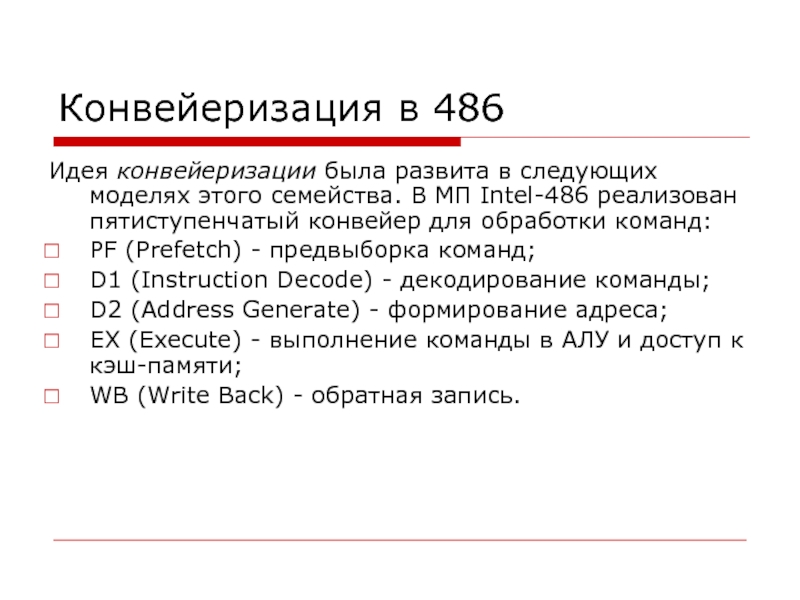

- 168. Идея конвейеризации была развита в следующих моделях этого семейства.

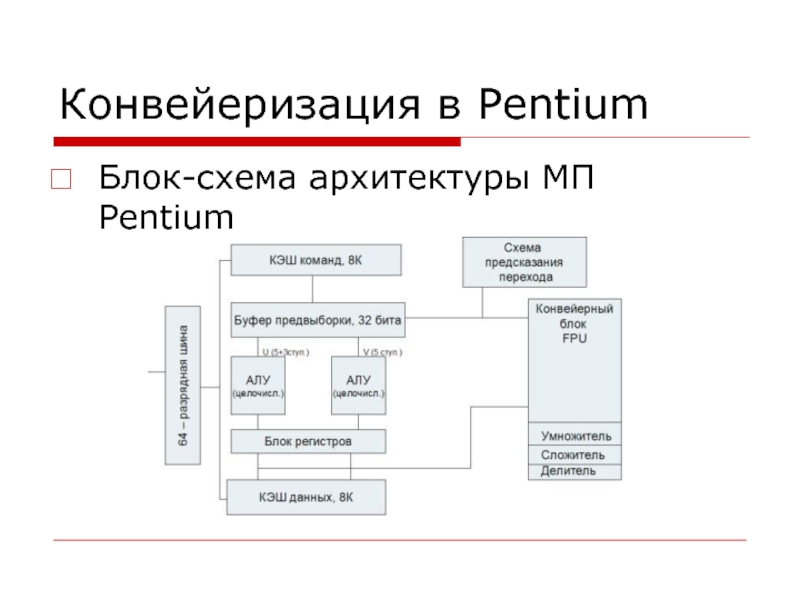

- 169. Конвейеризация в Pentium Блок-схема архитектуры МП Pentium

- 170. Конвейеризация в PentiumНовая микроархитектура процессоров Pentium и

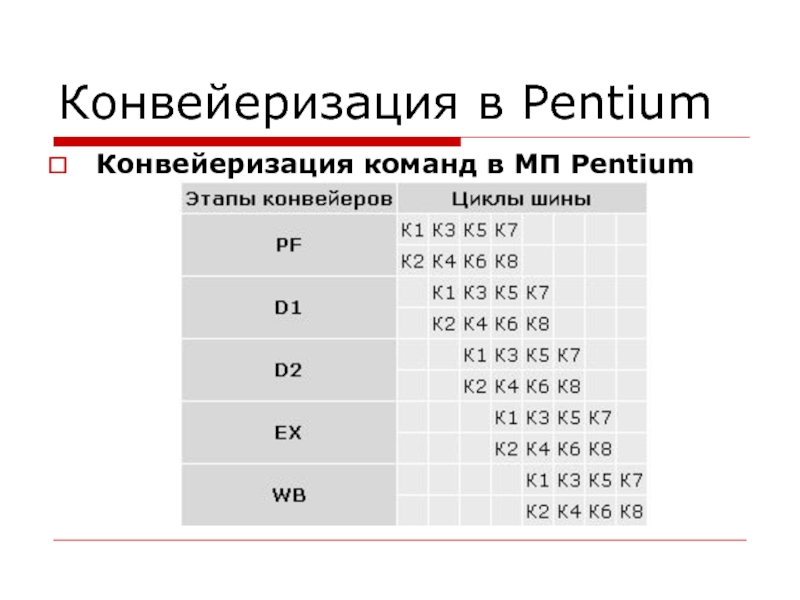

- 171. Конвейеризация в PentiumКонвейеризация команд в МП Pentium

- 172. Динамическое (спекулятивное) исполнениеОдной из главных особенностей шестого

- 173. Особенности P6Внутренняя организация МП P6 соответствует архитектуре

- 174. Особенности P6Блок исполнительных устройств способен выбирать инструкции

- 175. РазрядностьРазрядность Первые процессорные регистры могли хранить лишь

- 176. Блок схема микропроцессора Pentium Pro

- 177. Технология производства МПВыращивание диоксида кремния и создание проводящих областей Тестирование Изготовление корпуса. Доставка.

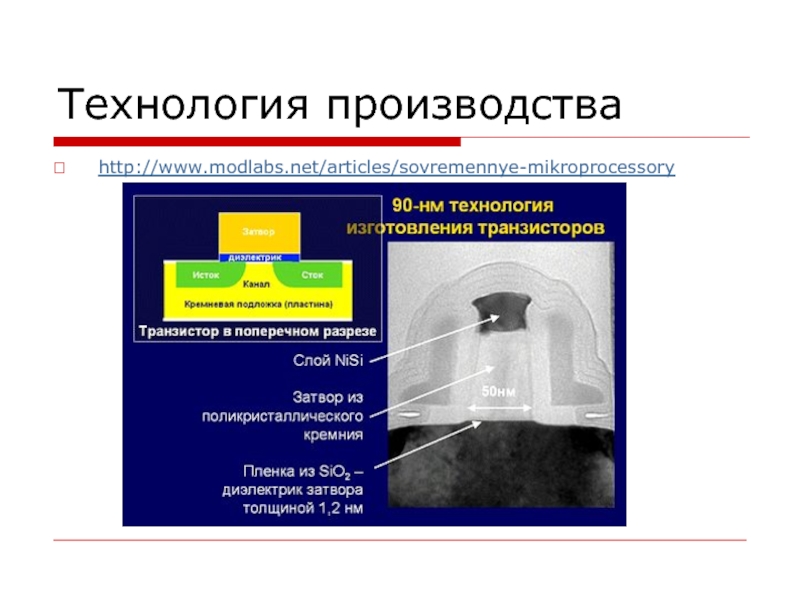

- 178. Технология производстваhttp://www.modlabs.net/articles/sovremennye-mikroprocessory

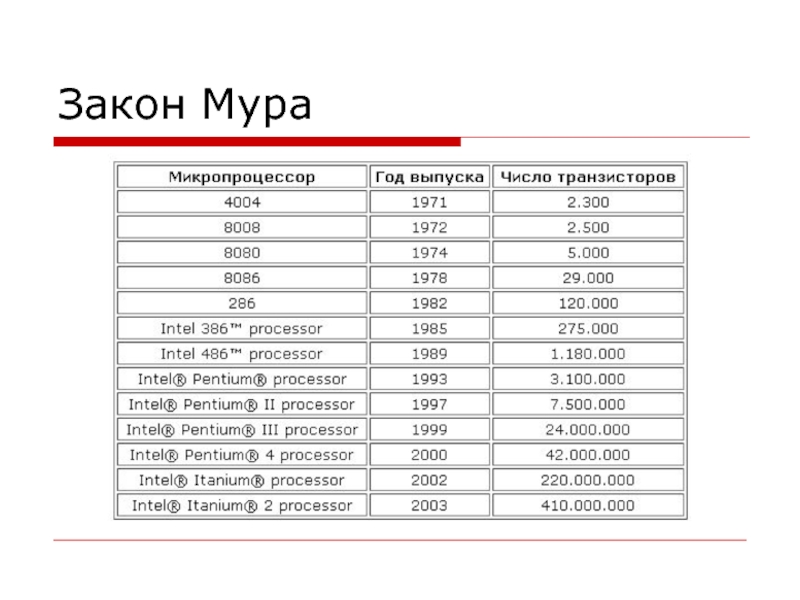

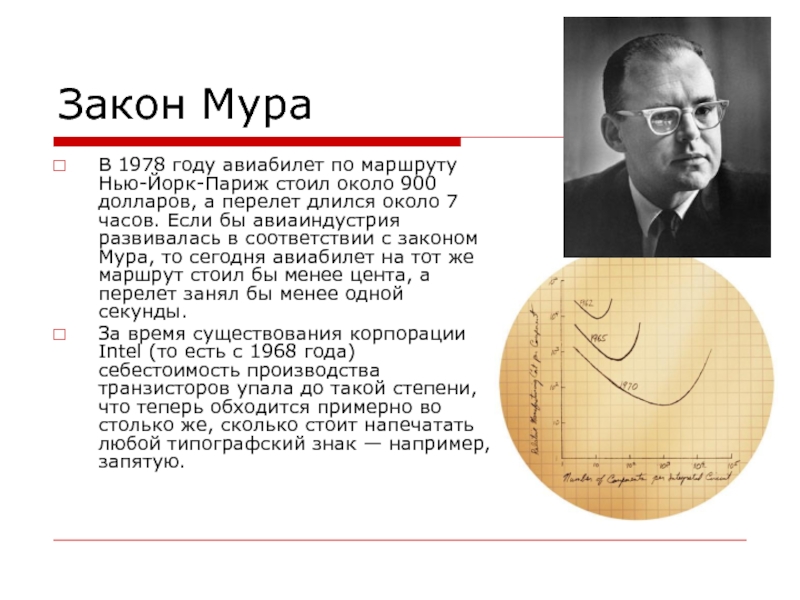

- 179. Закон Мура

- 180. Закон Мура40 лет назад микроэлектроника пребывала в

- 181. Закон МураВ 1978 году авиабилет по маршруту

- 182. Тема 6Система команд, выполняемых процессором, основные стадии выполнения команды, организация прерываний в ЭВМ

- 183. Учебные вопросы:Логические блоки микропроцессора: блок исполнения и

- 184. Логические блоки микропроцессора: блок исполнения и блок интерфейса шин

- 185. Порты ввода-вывода микропроцессора

- 186. Микропроцессорная память, регистры памяти

- 187. Понятие машинной команды

- 188. Нотации для описания операций с регистрами

- 189. Машинные команды на языке ассемблер

- 190. Этапы выполнения команд, линейный код и ветвление

- 191. Организация мультизадачного режима работы ЭВМ

- 192. Система прерываний и приоритетов, их назначениеПрерывания и исключения - это

- 193. Виды прерываний

- 194. Алгоритм обработки прерываний

- 195. Функции операционной системы в управлении прерыванием

- 196. Приоритеты и дисциплины обслуживания прерываний

- 197. Тема 7Организация памяти ЭВМ, типы и устройство памяти IMB-совместимых ПЭВМ

- 198. Учебные вопросы:Запоминающие устройства (ЗУ), назначение, основные характеристики.Классификация

- 199. Запоминающие устройства (ЗУ), назначение, основные характеристики

- 200. Классификация ЗУ

- 201. Постоянная память, ее назначение, принципы перезаписи информации

- 202. Сверхоперативная память: регистровая память, стековая память, кэш-память

- 203. Оперативная память (ОП), ее устройство, назначение, способы записи и считывания информации

- 204. Размещение информации в ОП персонального компьютера типа Intel

- 205. Управление памятью

- 206. Системы защиты памяти, их виды и назначение

- 207. Эволюция оперативной памяти ПЭВМ

- 208. Параметры модулей оперативной памяти

- 209. Наследование усовершенствований в развитии оперативной памяти

- 210. Соотношение объема оперативной памяти с используемой операционной системой

- 211. Тема 8Архитектурные особенности параллельных, многопроцессорных и многомашинных вычислительных систем

- 212. Учебные вопросы:Многомашинные вычислительные системы (ММС): назначение, уровни

- 213. СуперкомпьютерыСупер-ЭВМ обладают производительностью, достигающей 1011 оп./с и

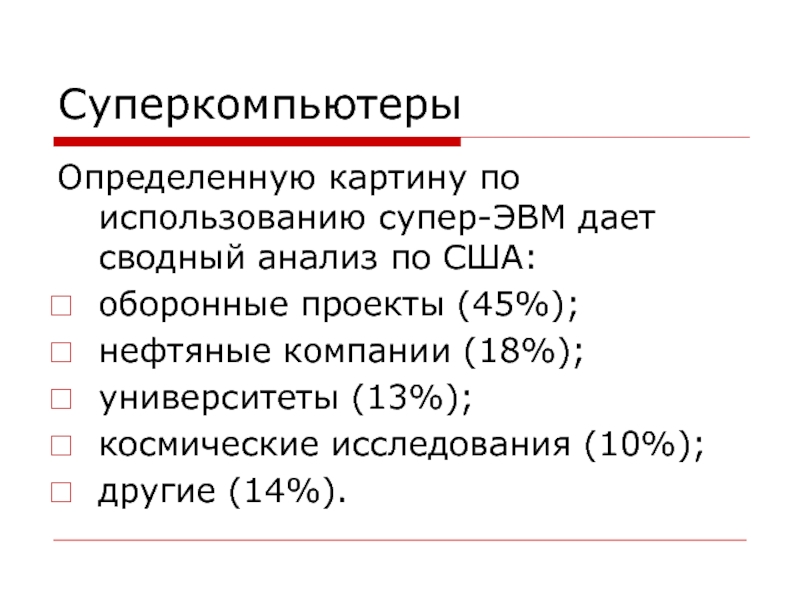

- 214. СуперкомпьютерыОпределенную картину по использованию супер-ЭВМ дает сводный

- 215. Многопроцессорные параллельные вычислительные системыСуперкомпьютеры, как и все

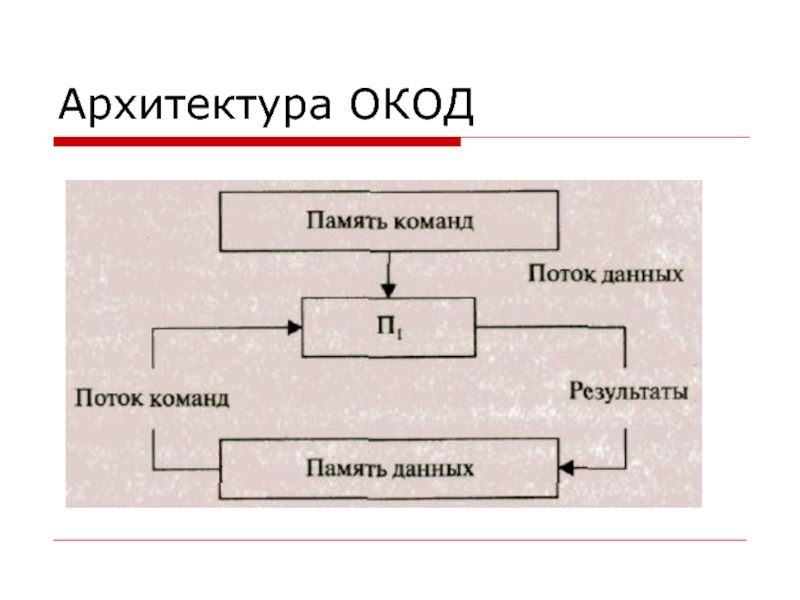

- 216. Архитектура ОКОД ОКОД - одиночный поток команд

- 217. Архитектура ОКОД

- 218. Архитектура ОКМД ОКМД — одиночный поток команд

- 219. Архитектура ОКМД

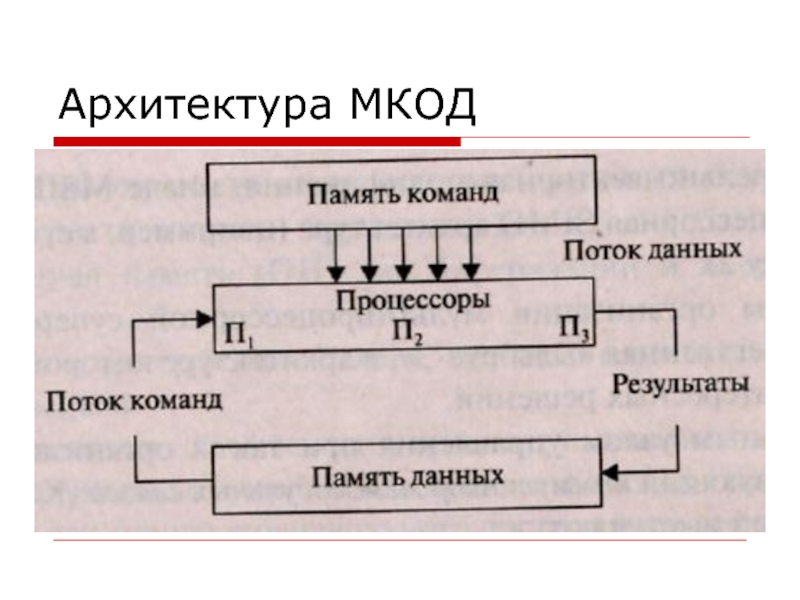

- 220. Архитектура МКОД МКОД — множественный поток команд

- 221. Архитектура МКОД

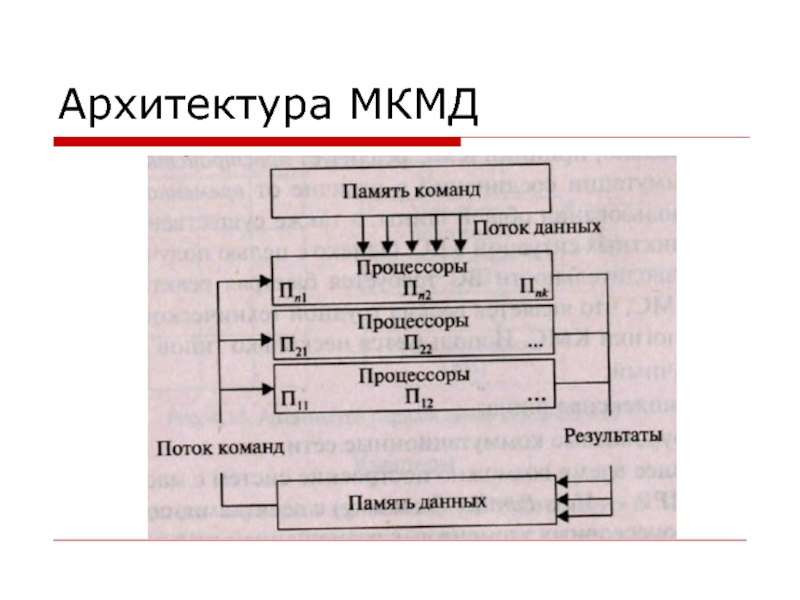

- 222. Архитектура МКМД Архитектура МКМД — множественный поток

- 223. Архитектура МКМД

- 224. Современные варианты архитектурыВ современных супер-ЭВМ используются три

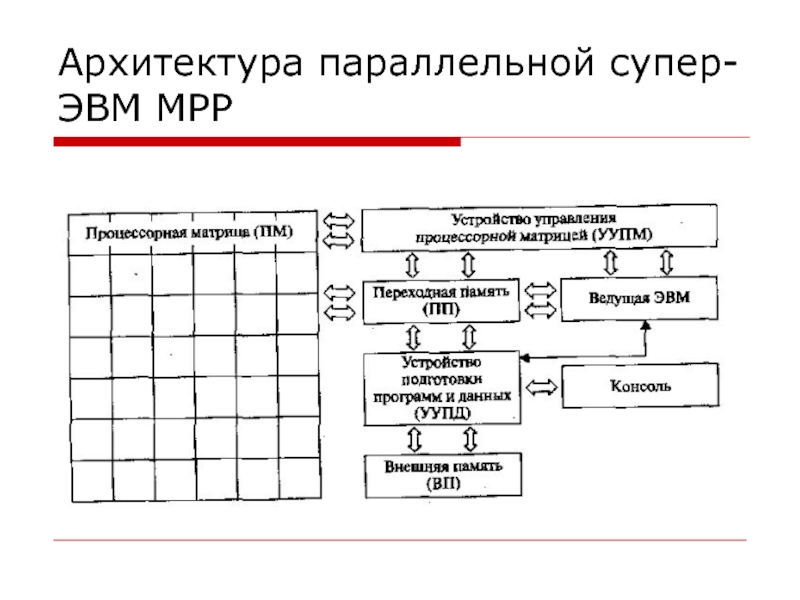

- 225. Системы с массовым параллелизмомВ настоящее время возможно

- 226. Архитектура параллельной супер-ЭВМ МРР

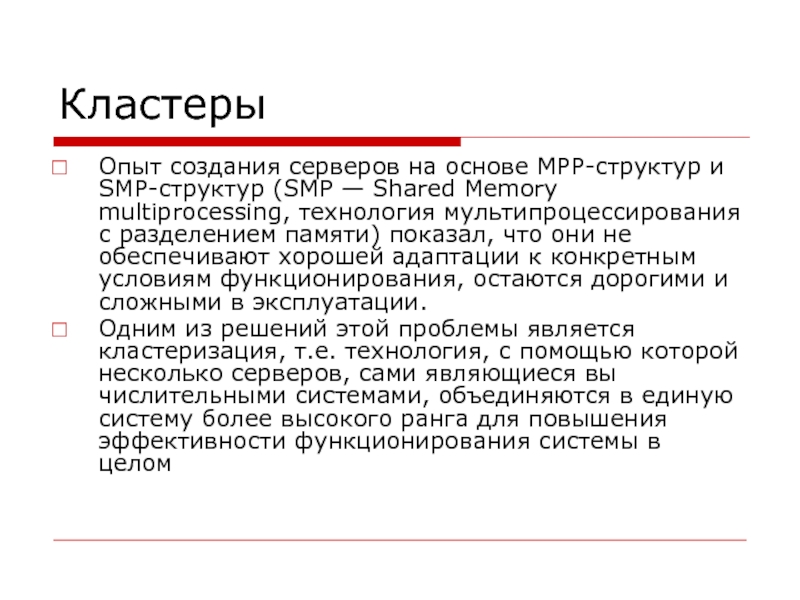

- 227. КластерыОпыт создания серверов на основе MPP-структур и

- 228. Кластеры

- 229. Кластеры. Зачем?Целями построения кластеров могут служить:улучшение масштабируемости

- 230. Многомашинные вычислительные системы (ММС): назначение, уровни организации взаимодействия

- 231. Многопроцессорные системы (МПС): назначение, распределение ресурсов системы между процессорами

- 232. Классификация и особенности архитектуры параллельных систем различных типов

- 233. Типовые структуры и характеристики параллельных ВС

- 234. Уровни и средства комплексирования средств вычислительной техники

- 235. Кластеризация

- 236. Тема 9Сети ЭВМ, информационно-вычислительные системы и сети

- 237. Учебные вопросы:Принципы распределенной обработки данных.Организация многомашинной вычислительной

- 238. Принципы распределенной обработки данных

- 239. Организация многомашинной вычислительной системы в информационно-вычислительную сеть (ИВС)

- 240. Задачи ИВС и техническое обеспечение их реализации

- 241. Показатели качества ИВС

- 242. Виды ИВС

- 243. Топологии сетей

- 244. Протоколы передачи данных

- 245. Понятие открытых систем и модель их взаимодействия

- 246. Тема 10Вычислительные сети: матричные и ассоциативные, конвейерные и потоковые

- 247. Учебные вопросы:Масштабируемость вычислительных систем.Факторы, влияющие на ограничения

- 248. Масштабируемость вычислительных систем

- 249. Факторы, влияющие на ограничения масштабируемости

- 250. Ассоциативные вычислительные сети: принцип ассоциативной обработки данных, ассоциативное запоминающее устройство

- 251. Конвейерные вычислительные сети: принцип конвейеризации данных и команд

- 252. Матричные вычислительные сети

- 253. Принцип матричной обработки потоков данных

- 254. Многомодальная логика

- 255. Многомодальная логика

- 256. Потоковые вычислительные сети

- 257. Принцип обработки многих данных с помощью одной команды

- 258. Векторная обработка данных

- 259. ЛитератураАппаратное обеспечение вычислительных систем / Д.В. Денисов,

- 260. Скачать презентанцию

Цель дисциплиныЦелью дисциплины «Архитектура ЭВМ и систем» является формирование у студентов базовой системы знаний в области устройства средств вычислительной техники, принципов организации вычислительных систем и сетей, подготовка студентов к профессиональной деятельности

Слайды и текст этой презентации

Слайд 1Архитектура ЭВМ и систем

Преподователь кафедры ИС МФПА

Аблов Игорь Васильевич

Адрес

в сети : http://iablov.narod.ru

Слайд 2Цель дисциплины

Целью дисциплины «Архитектура ЭВМ и систем» является формирование у

студентов базовой системы знаний в области устройства средств вычислительной техники,

принципов организации вычислительных систем и сетей, подготовка студентов к профессиональной деятельности в сфере эксплуатации средств вычислительной техники организации.Слайд 3Задачи изучения дисциплины

изучение принципов создания автоматизированных систем обработки данных;

формирование

системного подхода к процессам обработки информации,

изучение информационных систем с

точки зрения технического устройства средств обработки информации;изучение теоретических основ архитектуры Электронно-Вычислительных Машин (ЭВМ) и Вычислительных Сетей (ВС);

формирование представления о развитии средств вычислительной техники и перспективных разработках в этой области;

Слайд 4Задачи изучения дисциплины

изучение устройства основных компонент компьютера: центральное арифметико-логическое

устройство (АЛУ), центральное устройство управления (УУ), память, т.е. запоминающее устройство

(ЗУ), система ввода информации, система вывода информации;формирование представления о топологиях вычислительных систем и сетей, способах параллельной обработки информации;

развитие технического мышления по широкому кругу проблем эксплуатации средств вычислительной техники.

Слайд 5Студент должен иметь представление

об информатике как науке, технологии и

отрасли народного хозяйства;

о функциональной и структурной организации систем;

об истории развития

информационно-вычислительных систем (ИВС);о назначении и принципах работы арифметико-логического устройство (АЛУ) процессора;

о внешних интерфейсах ПК;

кластеризации как способе организации многомашинных ВС;

о принципах построения и возможностях суперкомпьютеров;

о ВС с массовым параллелизмом

Слайд 6Студент должен знать

показатели качества информации;

понятие системы обработки данных (СОД) и

их классификацию;

принципы архитектуры Электронно-Вычислительных Машин (ЭВМ) Джона фон Неймана;

принципы создания

элементов структур современных ЭВМ;этапы развития элементной базы электронных вычислительных машин (ЭВМ);

классификацию ЭВМ по различным признакам (принцип действия, назначение, вычислительная мощность и так далее);

типы современных компьютеров и сферы их использования;

классификацию процессоров;

логическое и техническое устройство процессоров;

систему команд микропроцессора, в том числе типы команд;

порядок обработки команд микропроцессором;

назначение и принципы обработки прерываний микропроцессором;

Слайд 7Студент должен знать

порядок адресации данных в оперативной памяти (ОП);

порядок доступа

и операции с данными оперативной памяти;

понятие прямого доступа к ОП

(DMA);режимы работы микропроцессора при обращении к ОП;

принципы подключения периферийных устройств;

понятия: драйвер, стандартные периферийные устройства, устройства сопряжения;

стандарты внешних интерфейсов: Centronics, RS-232C, USB, PCI;

назначение и основные принципы построения информационно-вычислительных сетей (ИВС);

показатели качества работы ИВС;

Слайд 8Студент должен знать

виды ИВС и топологии их построения;

модели взаимодействия открытых

систем;

способы организации взаимодействия компьютеров в многомашинных ВС;

организацию и принципы построения

многопроцессорных ВС;классификацию многопроцессорных параллельных ВС по режиму выполнения команд (классификация Флинна);

различные подходы к классификации многопроцессорных параллельных ВС (классификации Дункана, Хокни и другие);

Слайд 9Студент должен уметь:

определять тип и класс ЭВМ по его техническим

параметрам и описанию;

определять тип ЛВС по представленной топологии;

формулировать требования к

ЛВС с точки зрения экономичности, качества работы, требований заказчика и других критериев;определять тип архитектуры ВС по представленному описанию режиму выполнения команд (классификация Флинна);

Слайд 10Студент должен приобрести навыки:

использования системного подхода применительно к процессам обработки

информации;

определения типа и класса вычислительной системы или вычислительной сети по

ее техническим параметрам и способу организации;формирования требований к вычислительным системам и вычислительным сетям, исходя из решаемого с их помощью комплекса задач.

Слайд 11Тема 1

ЭВМ как средство обработки информации: основные характеристики информационно-вычислительных систем

Слайд 12Учебные вопросы:

Назначение ЭВМ.

Представление информации в ЭВМ.

Показатели качества информации.

Информатика как технология, сфера народного хозяйства и наука об информации.

Систематизация процесса обработки информации - информационные системы (ИС), их структура и классификация.

Взаимосвязь понятий "информатика", "информация", "система", "информационно-вычислительная система".

Информационно-вычислительные системы (ИВС) как логическое развитие информационных систем.

Классификация, состав и функции ИВС.

Поколения ЭВМ.

Эволюция ЭВМ и вычислительных систем (ВС).

Слайд 13Введение

Развитие Вычислительной Техники (ВТ) обусловлено успехами в 3-х областях:

В технологии

производства, как элементарной базы ВТ, так и самих машин в

целом.В принципах организации ВМ (успехи в развитии архитектуры).

В разработке математического и программного обеспечения.

Любая ВМ должна рассматриваться, как некоторый программно - аппаратный комплекс, обеспечивающий реализацию некоторого класса алгоритмов над информацией.

Слайд 14Архитектура

В процессе работы ВМ все ее компоненты каким-то образом взаимодействуют

между собой. Причем уровни рассмотрения этого взаимодействия могут быть различными:

Низший

уровень: на уровне электрических импульсов.Высший уровень: взаимодействие узлов ВМ на уровне программных модулей (1 и 2 рассматривать не будем).

Функциональный уровень каждого отдельного узла: функция и их реализация программно – аппаратными средствами (под этим и понимается понятие “Архитектура”).

Под Архитектурой понимается совокупность свойств и характеристик ВМ, рассматриваемая с точки зрения пользователя.

Слайд 15Обобщенная структура ЭВМ

Принцип действия обычной ВМ можно считать копией обычного

процесса вычислений (например, с помощью калькулятора).

Этапы вычислений:

1. Определение и задание

порядка вычислений.2. Задание исходных данных.

3. Выполнение вычислений (для получения промежуточных результатов)

4. Получение конечного результата.

То есть любая ВМ имеет 4 базовых узла.

Слайд 17Алгоритм

В основе функционирования любой ВМ лежат два фундаментальных понятия в

вычислительной технике:

понятие алгоритма.

принцип программного управления.

Алгоритм - некоторая однозначно определенная последовательность

действий, состоящая из формально заданных операций над исходными данными, приводящая к решению за конечное число шагов.Слайд 18Алгоритм

Алгоритм - некоторая однозначно определенная последовательность действий, состоящая из формально

заданных операций над исходными данными, приводящая к решению за конечное

число шагов.Свойства алгоритмов:

1. дискретность алгоритма (действия выполняются по шагам, а сама информация дискретна)

2. детерменированность (сколько бы раз один и тот же алгоритм не реализовывался для одних и тех же данных результат один и тот же)

3. массовость (алгоритм "решает задачу" для различных исходных данных из допустимого множества и дает всегда правильный результат)

Слайд 19Программа

Программа – описание алгоритма на каком-либо языке.

Принцип программного управления (ППУ)

впервые был сформулирован Венгерским математиком и физиком Джоном фон Нейманом,

при участии Гольцтайна и Берца в 1946 году.Слайд 20Архитектурно-функциональные принципы

ППУ включает в себя несколько архитектурно – функциональных принципов.

Любой

алгоритм представляется в виде некоторой последовательности управляющих слов – команд.

Каждая отдельная команда определяет простой (единичный) шаг преобразования информации.Принцип условного перехода. В процессе вычислений в зависимости от полученных промежуточных результатов возможен автоматический переход на тот или иной участок программы.

Принцип хранимой программы. Команды в ЭВМ представляются в такой же кодируемой форме, как и любые данные и хранятся в таком оперативном запоминающем устройстве (ОЗУ). Это значит, что если рассматривать содержимое памяти, то без какой-то команды невозможно различить данные и команды. Следовательно, любые команды можно принципиально обрабатывать как данные (информация в ЭВМ отличается не представлением, а способом ее использования).

Принцип двоичного кодирования.

Принцип иерархии запоминающих устройств (ЗУ).

Слайд 21Назначение ЭВМ

ЭВМ обладает способностью собирать и хранить информацию, обрабатывать и

анализировать ее, проводя определенные логические операции

По назначению электронно-вычислительные машины разделяются

на специализированные (предназначенные для решения узкого круга специальных задач) и универсальные (предназначенные для решения широкого круга задач). Слайд 22Представление информации в ЭВМ

Любая информация, поступающая в ЭВМ, преобразуется в

двоичный код. Это могут быть тексты, изображения, числа, звуки и

т.д. Например, все клавиши клавиатуры компьютера закодированы 8-разрядными двоичными кодами таким образом, что любая буква латинского и русского алфавита, как заглавная, так и прописная, цифры десятичной системы счисления, знаки препинания и другие служебные символы имеют свой индивидуальный двоичный код. Поскольку двоичное 8-разрядное число (байт) может иметь 28 = 256 комбинаций, то этого вполне достаточно для кодирования сразу нескольких текстовых алфавитов. Изображение на экране компьютера представляется в виде растрового расположения точек (пикселей). Информация о содержании каждой точки хранится в одном 8-разрядном двоичном коде. Это позволяет отображать черно-белые изображения с 256-ю градациями яркости. Для цветных изображений каждый из 3-х основных цветов также кодируется 1 байтом, следовательно на каждую цветную точку выделяется 3 байта информации. На кодирование звукового элемента - ноты требуется от нескольких единиц до десятков байт и т.д. С учётом вышеизложенного, одна страница текста имеет информационный объём ~3 Кбайт, один цветной экранный кадр содержит уже ~3 Мбайт, а 1,5-часовой цветной телевизионный фильм ~ 300 Гбайт.Слайд 23Показатели качества информации

Возможность и эффективность использования информации для управления обусловливается

такими ее потребительскими показателями качества, как репрезентативность, содержательность, полнота, доступность,

актуальность, своевременность, точность, устойчивость, достоверность и ценность.Слайд 24Показатели качества

Репрезентативность информации связана с правильностью ее отбора и формирования

с целью адекватного отражения заданных свойств объекта.

Содержательность информации определяется

удельной семантической емкостью (коэффициентом содержательности), равной отношению количества семантической информации к общему объему данных.Полнота информации означает, что она содержит минимальный, но достаточный для принятия правильного управленческого решения состав.

Доступность информации для ее восприятия при принятии управленческого решения обеспечивается нением соответствующих процедур ее получения и преобразования.

Актуальность информации определяется степенью хранения ценности информации для управления в момент ее использования.

Слайд 25Показатели качества

Своевременность информации определяется возможностью ее использования при принятии управленческого

решения без нарушения установленной процедуры и регламента. Таким образом, своевременной

является информация, поступающая на тот или иной уровень управления не позже заранее назначенного момента времени.Точность информации определяется степенью близости отображаемого информацией параметра управления и истинного значения этого параметра.

Устойчивость — это свойство информации реагировать на изменение исходных данных, сохраняя необходимую точность.

Достоверность информации определяется ее свойством отображать реально существующие объекты с необходимой точностью.

Наконец, ценность информации — это комплексный показатель ее качества, мера количества информации на прагматическом уровне.

Слайд 26Информатика как технология, сфера народного хозяйства и наука об информации

Информатика

— это научная и прикладная область знаний, изучающая законы, методы

и способы накопления, обработки и передачи информации с помощью компьютерных и других технических средств.Слайд 27Информатика

Информатика изучает свойства, структуру и функции информационных систем, а также

происходящие в них информационные процессы. Под информационной системой понимают систему,

организующую, хранящую и преобразующую информацию. Подавляющее большинство современных информационных систем являются автоматизированными.Информатика тесно связана с кибернетикой, но не тождественна ей. Кибернетика изучает общие закономерности процессов управления сложными системами в разных областях человеческой деятельности независимо от наличия или отсутствия компьютеров. Информатика же изучает общие свойства только конкретных информационных систем.

Информатику можно рассматривать как науку, как технологию и как индустрию.

Слайд 28ИНформатика

Информатика как наука объединяет группу дисциплин, занимающихся изучением различных аспектов

свойств информации в информационных процессах, а также применением алгоритмических, математических

и программных средств для ее обработки с помощью компьютеров.Информатика как технология включает в себя систему процедур компьютерного преобразования информации с целью ее формирования, хранения, обработки, распространения и использования. Основными чертами современной (новой) информационной технологии являются:

дружественный программный и аппаратный интерфейс;

интерактивный (диалоговый) режим решения задач;

сквозная информационная поддержка всех этапов решения задачи на основе интегрированной базы данных;

возможность коллективного решения задач на основе информационных сетей и систем телекоммуникаций;

безбумажная технология, при которой основным носителем информации является не бумажный, а электронный документ.

Слайд 29Информатика

Информатика как индустрия — это инфраструктурная отрасль народного хозяйства, обеспечивающая

все другие отрасли необходимыми информационными ресурсами. Индустрия информатики включает в

себя предприятия, производящие вычислительную технику и ее элементы; вычислительные центры различного типа и назначения (индивидуальные, кустовые, коллективного пользования и др.); предприятия, осуществляющие производство программных средств и проектирование информационных систем; организации, накапливающие, распространяющие и обслуживающие фонды алгоритмов и программ; станции технического обслуживания вычислительной техники.Слайд 30Информатика

Роль информатики в современных условиях постоянно возрастает. Деятельность как отдельных

людей, так и целых организаций все в большей степени зависит

от их информированности и способности эффективно использовать имеющуюся информацию. Внедрение компьютеров, современных средств переработки и передачи информации в различные индустрии послужило началом процесса, называемого информатизацией общества. Современное материальное производство и другие сферы деятельности все больше нуждаются в информационном обслуживании, переработке огромного количества информации. Информатизация на основе внедрения компьютерных и телекоммуникационных технологий является реакцией общества на потребность в существенном увеличении производительности труда в информационном секторе общественного производства, где сосредоточено более половины трудоспособного населения.Результатом процесса информатизации является создание информационного общества, где манипулируют не материальными объектами, а идеями, образами, интеллектом, знаниями. Для каждой страны ее движение от индустриального этапа развития к информационному определяется степенью информатизации общества.

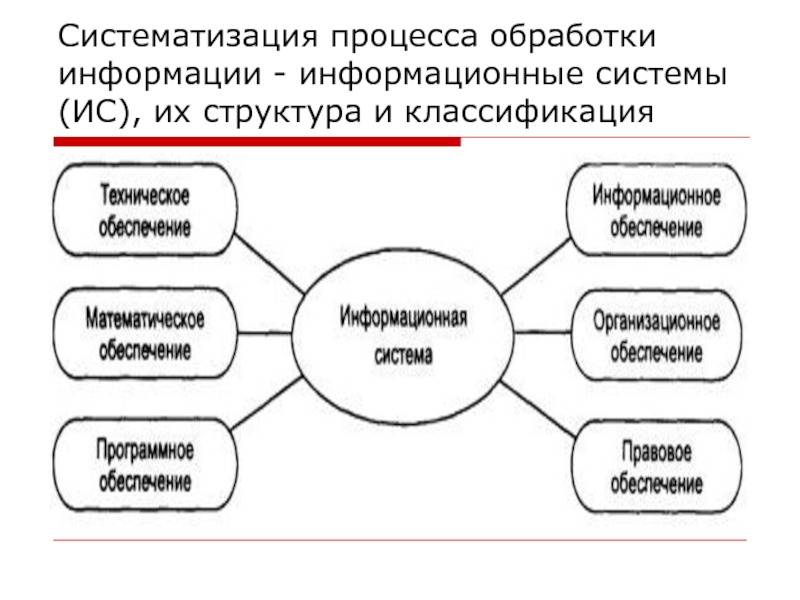

Слайд 32Систематизация процесса обработки информации - информационные системы (ИС), их структура

и классификация

Инфopмaциoннaя cиcтeмa - этo cpeдa, oбecпeчивaющaя цeлeнaпpaвлeннyю дeятeльнocть пpeдпpиятия.

Тo ecть oнa пpeдcтaвляeт coбoй coвoкyпнocть кoмпoнeнтoв (инфopмaция, пpoцeдypы, пepcoнaл, aппapaтнoe и пpoгpaммнoe oбecпeчeниe), oбъeдинeнныx peгyлиpyeмыми взaимooтнoшeниями для фopмиpoвaния opгaнизaции кaк eдинoгo цeлoгo и oбecпeчeния ee цeлeнaпpaвлeннoй дeятeльнocтиМиccия инфopмaциoнныx cиcтeм - этo пpoизвoдcтвo нyжнoй для opгaнизaции инфopмaции для oбecпeчeния эффeктивнoгo yпpaвлeния вceми ee pecypcaми, coздaниe инфopмaциoннoй и тexничecкoй cpeды для ocyщecтвлeния yпpaвлeния opгaнизaциeй.

Слайд 33Систематизация процесса обработки информации - информационные системы (ИС), их структура

и классификация

Структуру информационной системы составляет совокупность отдельных ее частей, называемых

подсистемами Общую структуру информационной системы можно рассматривать как совокупность подсистем независимо от сферы применения. В этом случае говорят о структурном признаке классификации, а подсистемы называют обеспечивающими. Таким образом, структура любой информационной системы может быть представлена совокупностью обеспечивающих подсистем

Среди обеспечивающих подсистем обычно выделяют информационное, техническое, математическое, программное, организационное и правовое обеспечение.

Слайд 34Систематизация процесса обработки информации - информационные системы (ИС), их структура

и классификация

Слайд 35Систематизация процесса обработки информации - информационные системы (ИС), их структура

и классификация

Важнейшими принципами построения эффективных информационных систем являются следующие:

Принцип

интеграции, заключающийся в том, что обрабатываемые данные, однажды введенные в систему, многократно используются для решения большого числа задач. Принцип системности, заключающийся в обработке данных в различных аспектах, чтобы получить информацию, необходимую для принятия решений на всех уровнях управления.

Принцип комплексности, заключающийся в механизации и автоматизации процедур преобразования данных на всех этапах функционирования информационной системы.

Слайд 36Систематизация процесса обработки информации - информационные системы (ИС), их структура

и классификация

Информационные системы также классифицируются:

по функциональному назначению: производственные, коммерческие,

финансовые, маркетинговые и др.; по объектам управления: информационные системы автоматизированного проектирования, управления технологическими процессами, управления предприятием (офисом, фирмой, корпорацией, организацией) и т. п.;

по характеру использования результатной информации: информационно-поисковые, предназначенные для сбора, хранения и выдачи информации по запросу пользователя; информационно-советующие, предлагающие пользователю определенные рекомендации для принятия решений (системы поддержки принятия решений); информационно-управляющие, результатная информация которых непосредственно участвует в формировании управляющих воздействий.

Слайд 37Взаимосвязь понятий "информатика", "информация", "система", "информационно-вычислительная система"

самостоятельно

Слайд 38Информационно-вычислительные системы (ИВС) как логическое развитие информационных систем

самостоятельно

Слайд 39Классификация, состав и функции ИВС

Классификация по принципам:

по территориальности

по организация передачи

данных

по геометрии

Слайд 40Поколения ЭВМ

Первое (ламповые, начало 50-х)

Второе (транзисторные 60-е)

Третье (интегральная системотехника, конец

60-х)

Четвертое (БИС, конец 70-х)

Пятое (микропроцессорные, конец 80-х)

Шестое (Оптоэлектронные с массовым

параллелизмом и нейронной структурой, наше тысячелетие)Слайд 41Первое поколение

Ламповые ЭВМ, промышленный выпуск начат в начале 50-х годов.

В нашей стране началом выпуска можно считать начало 50-х годов

“МЭСМ”. Разработана под руководством Лебедева. В 1952-1953 годах на этой основе, под руководством Мельникова и Бурцева была разработана “БЭСМ-1” (Большая электронная счетная машина). А на ее основе был произведен серийный выпуск машины “БЭСМ-2”. В это же время в США выпускают машину “Эдвак”. Технические характеристики машины “БЭСМ-2” были гораздо выше. Это было связано с тем, что в “БЭСМ-2”, использовались два совершенно новых принципа: конвейеризации и стека. Для “БЭСМ-2”, быстродействие АЛУ составляло порядка 10000 операций в секунду.В 1953 году была разработана машина “Стрела” под руководством Василевского. А так же в Московском Энергетическом институте под руководством академика Брука были разработаны ЭВМ получившие название “М”. В Минске был создан завод по производству ЭВМ, серийное производство машин “Минск”. В городе Пензе было создано ОКБ (отдел конструкторского бюро) под руководством академика Рамеева, где разработали и выпускали серийно ЭВМ “Урал”.

Структура ЭВМ первого поколения полностью соответствовали машине фон Неймана.

Технические характеристики машин были значительно ниже характеристик современных ПК. Программирование велось в машинных кодах. Емкость ОЗУ – 2 тысячи слов. Ввод информации с перфоленты и кинопленки.

Слайд 42Второе поколение

Связывают с переходом от ламповых к транзисторным ЭВМ. Транзисторы

позволяли обеспечить большую надежность, быстродействие и меньшее энергопотребление (среднее время

отказа около 100 часов, тогда как на машинах первого поколение около 10 часов, энергоемкость на два порядка ниже, по сравнению с машинами первого поколения). Переход к печатному монтажу также улучшило надежность.Слайд 44Второе поколение

Начинается бурное развитие математического и программного обеспечения. Высшая точка:

создание алгоритмических языков (Fortran, ALGOL). Создаются простейшие компиляторы и интерпретаторы.

Становится нецелесообразна работа пользователя у пульта управления. Основным режимом становится работа через операторов. Появляются многопрограммные ЭВМ. Многопрограммность достигается за счет программной обработки. Для работы в пакетном режиме создаются первые мониторы и supervisor’ы. Вследствие чего происходит резкое увеличение использование ЭВМ второго поколения.Слайд 45Третье поколение

В конце 60-х годов появляются первые машины третьего поколения.

Переход к третьему поколению ЭВМ связывают с серьезными архитектурными изменениями.

Изменение технической базы связано с переходом на интегральную схематехнику. Правда степень интеграции была небольшой. Вследствие чего произошло заметное увеличение надежности. В машинах третьего поколения формируется концепция канала, начинается работа с распараллеливанием процессора, появляется микропрограммное управление, иерархируется память, впервые вводится понятие агрегатирования.Слайд 46Архитектура третьего поколения

Канал является основным структурным элементом.

В структуре процессора и

оперативной памяти появляются специальные устройства, которые организуют адресные механизмы (обеспечивающие

адресацию, перемещение программы в памяти, взаимную защиту). В процессоре появляется несколько АЛУ (целочисленные, с плавающей арифметикой, для работы с адресами). Правда, эти устройства параллельно не работают, но для выполнения той или иной обработки выбирается определенное АЛУ.Слайд 47Третье поколение

В памяти четко выделяется основная память, к которой процессор

обращается непосредственно, и массовая память, емкость которой значительно больше емкости

основной памяти, но непосредственно процессору она недоступна. Тем более данные с внешних устройств непосредственно недоступны процессору. Так как память иерархична, то создаются механизмы для управления памятью. Развивается и внутренняя память процессора (создаются предпосылки кэширования). В конце третьего поколения ЭВМ появляется концепция управления виртуальной памяти, развиваются внешние устройства и терминальное оборудование. Самое главное в тот период: унификация ЭВМ по конструктивно - технологическим параметрам. ЭВМ третьего поколения начинают выпускаться сериями или семействами, совместимыми моделями. Дальнейшее развитие математического и программного обеспечения приводит к созданию пакетных программ для решения типовых задач, проблемно - ориентированных программных языков (для решения задач отдельной категории) и впервые создаются уникальные программные комплексы, - операционные системы (разработаны IBM).Слайд 48Четвертое поколение

В конце 70-х кодов появляются первые ЭВМ четвертого поколения.

Связано с переходом на интегральные схемы средней и большой степени

интеграции.Характерные свойства ЭВМ четвертого поколения:

Мультипроцессорность

Параллельно – последовательная обработка

Языки высокого уровня

Появляются первые сети ЭВМ

Слайд 49Технические характеристики 4-го поколения

Средняя задержка сигнала 0.7 нс./вентиль (вентиль –

типовая схема)

Впервые основная память – полупроводниковая. Время выработки данного из

такой памяти 100-150 нс. Емкость 1012 –1013 символов.Впервые применяется аппаратная реализация оперативной системы

Модульное построение стало применяться и для программных средств

Основная внимание машин четвертого поколения было направлено на сервис (улучшение общения ЭВМ и человека).

Слайд 50Пятое поколение

В конце 80-х годов появляются первые ЭВМ пятого поколения.

Пятое поколение ЭВМ связывают с переходом к микропроцессорам. С точки

зрения структурного построения характерна максимальная децентрализация управления. С точки зрения программного и математического обеспечения – переход на работу в программных средах и оболочках. Производительность 108 - 109 операций в секунду. Для пятого и шестого поколения характерны многопроцессорные структуры созданные на упрощенных микропроцессорах, которых очень много (решающие поля или среды). Создаются ЭВМ ориентированные на языки высокого уровня.Слайд 51Современные тенденции

В этот период существуют две диаметрально противоположных тенденции:

Персонификация ресурсов

Коллективизация

ресурсов (коллективный доступ – сети)

Слайд 52Шестое поколение

Оптоэлектронные ЭВМ с массовым параллелизмом и нейронной структурой —

с сетью из большого числа (десятки тысяч) несложных микропроцессоров, моделирующих

структуру нейронных биологических систем.Слайд 53Эволюция ЭВМ и вычислительных систем (ВС)

История ВТ отсчитывается с опубликования

работы Джона фон Неймана. Впервые возможность построения цифровой ВМ была

доказана английским математиком Тьюрингом в 1936 году. Он показал, что любой алгоритм реализуется с помощью его дискретного автомата, который был назван машиной Тьюринга. Независимо это же доказал Пост (машина Поста).Слайд 54Первая настоящая ЭВМ

Физически первая цифровая ВМ была сконструирована в 1935

году фирмой Белл (США). Такого же вида машина была сконструирована

для специальных задач под руководством К. Цунзе (1941, Германия). Попытка построения универсальной ЭВМ была предпринята Айтнетом (США). Она получила название “Марк-1”. Спроектирована и изготовлена в Гарвардском университете.Слайд 55Характеристики

Характеристики ВМ (работали с 23 разрядными десятичными цифрами):

Программа вводилась по-командно

с перфоленты.

Сложение 2-х чисел 0.3 секунды

Умножение 2-х чисел 6 секунд

Деление

2-х чисел 11 секунд.Релейная основа была ненадежна. Для ЭВМ были разработаны специальные реле. На которых была разработана ВМ “Марк-2”. Реальный отсчет ВТ ведется с перехода от реле к триггерам. Триггер был изобретен в 1918 году в России Бонч-Бруевичем.

Слайд 56Адамы современных ЭВМ

Первая ЭВМ, разработанная на электронных компонентах, изготовлена в

1942 году (“Эниак”). Серийный выпуск в 1945-1946 годах. Разработана в

Пенсельванском университете под руководством Маушли и Энкера. В 1943 году под руководством Тьюринга была разработана ЭВМ “Колос”. После рассекречивания архивов в 70-х годах оказалось, что первая ЭВМ была разработана в 1939 году выходцем из Германии Антоносовым, которая получила название “ABC”.Слайд 58Учебные вопросы:

Характеристика семейств ЭВМ.

Требования к ИВС, определяющие класс используемых ЭВМ.

Масштабируемость

ИВС.

Совместимость и мобильность программного обеспечения.

Классификация персональных компьютеров (ПК).

Понятие о суперЭВМ,

мини- и микроЭВМ, особенности их архитектуры.Основные области и формы использования ЭВМ различных классов.

Слайд 59Характеристики семейств ЭВМ

Операционные ресурсы ЭВМ

Емкость памяти

Быстродействие ЭВМ

Надежность ЭВМ

Показатель стоимости

Слайд 60Операционные ресурсы ЭВМ

Операционные ресурсы ЭВМ – это (грубо говоря) перечень

возможностей ЭВМ. Сюда включаются:

Способы представления информации в ЭВМ

Система команд ЭВМ

Способы

адресацииОперационные ресурсы ЭВМ напрямую связаны с аппаратными средствами, которые характеризуют степень приспособленности ЭВМ для решения тех или иных задач.

Слайд 61Емкость памяти

Емкость памяти (внешняя и основная) Основная память, какой бы

большой она не была, всегда ограничена. Внешняя память не ограничена.

Для характеристики компьютера используют емкость основной памяти. Использование памяти идет многобайтно, следовательно, доступ измеряется в байтах (максимальная память 4Гб). Внешняя память – суммарная емкость всех накопительных устройств. Следовательно, необходимо использовать косвенную характеристику – количество накопителей подключаемых к ЭВМ. В современных компьютерах есть также и сверхоперативная память (cashe), ее объем – один из важнейших параметров влияющих на время решения задачи.Слайд 62Быстродействие ЭВМ

Быстродействие ЭВМ характеризует скорость обработки информации компьютером (число операций

в секунду (V), время выполнения (τ=1/v)). Но для различных операций

эти показатели различны, следовательно, реальная характеристика – номинальное быстродействие (Vн)– количество коротких операций в единицу времени (обычно берут операцию “+”, а операнды хранятся во внутренних регистрах процессора (R-R)). Иногда также используют в качестве характеристики быстродействия – цикл обращения к основной памяти, а также эффективное быстродействие (Vф) Vф=1/ Σpiτi pi – вероятность выполнения i-ой операции. По содержанию производительность ЭВМ – это среднее число операций в единицу времени.Производительность ЭВМ зависит от:

1. Быстродействия процессора

2. Класса решаемых задач

3. Порядка прохождения задачи через ЭВМ

Для оценки числового выражения эффективности ЭВМ используют смеси команд.

Слайд 64Надежность ЭВМ.

Надежность – свойство ЭВМ выполнять возложенные на нее функции

в течение заданного промежутка времени, необходимого для решения поставленной задачи.

В процессе функционирования ЭВМ возникают отказы, связанные с неисправностью отдельных элементов либо соединений между ними.Слайд 65Отказы

По характеру проявлений отказы могут быть:

1. Внезапный отказ (механическое разрушение

элементов)

2. Постепенный отказ (деградация параметров ЭВМ)

С точки зрения математического подхода

– отказы это случайное событие. Используется самая простейшая математическая модель – “Простейший поток отказов”. Если поток отказов простейший, то в качестве характеристики надежности используется величина интенсивности потоков отказа. λ=1/Тр Тр – среднее время безотказной работы между двумя очередными отказами.Слайд 66Показатель стоимости

Показатель стоимости – суммарная стоимость всего оборудования, входящего в

состав ЭВМ. Если возрастает количество оборудования ЭВМ, то в конечном

итоге, будет расти не только стоимость, но будет расти и ее производительность. Путем статистического анализа была выведена связь между стоимостью и производительностью. Впервые это было установлено Найтом и получило название “Закон Гроша”. (V=kS2),где k – константа определяется эмпирически

Слайд 67Вывод

Вывод, если не менять технологическую базу компьютеров, то:

При росте стоимости

ЭВМ растет количество оборудования и, следовательно, снижается скорость решения задачи.

При

росте стоимости ЭВМ растет объем оборудования и, следовательно, увеличивается время ремонта.Слайд 69Классификация ЭВМ

ЭВМ классифицируются по:

Назначению.

Принципу действия

По размерам и функциональным возможностям

Способу

структурной организации

Производительности.

Режимам работы

Слайд 70По назначению

универсальные (общего назначения) — предназначены для решения самых разных

инженерно-технических задач: экономических, математических, информационных и других задач, отличающихся сложностью

алгоритмов и большим объемом обрабатываемых данных. Характерными чертами этих ЭВМ являются высокая производительность, разнообразие форм обрабатываемых данных (двоичных, десятичных, символьных), разнообразие выполняемых операций (арифметических, логических, специальных), большая емкость оперативной памяти, развитая организация ввода-вывода информации;проблемно-ориентированные — предназначены для решение более узкого круга задач, связанных обычно с технологическими объектами, регистрацией, накоплением и обработкой небольших объемов данных (управляющие вычислительные комплексы);

специализированные — для решения узкого круга задач, чтобы снизить сложность и стоимость этих ЭВМ, сохраняя высокую производительность и надежность работы (программируемые микропроцессоры специального назначения, контроллеры, выполняющие функции управления техническими устройствами).

Слайд 71По принципу действия

аналоговые вычислительные машины (АВМ) — вычислительные машины непрерывного

действия, работают с информацией, представленной в непрерывной форме, т.е. виде

непрерывного ряда значений какой-либо физической величины (чаще всего электрического напряжения); в этом случае величина напряжения является аналогом значения некоторой измеряемой переменной. Например, ввод числа 19.42 при масштабе 0.1 эквивалентен подаче на вход напряжения в 1.942 В;цифровые вычислительные машины (ЦВМ) — вычислительные машины дискретного действия, работают с информацией, представленной в дискретной, а точнее в цифровой, форме — в виде нескольких различных напряжений, эквивалентных числу единиц в представляемом значении переменной;

гибридные вычислительные машины (ГВМ) — вычислительные машины комбинированного действия, работают с информацией, представленной и в цифровой, и в аналоговой форме.

Слайд 72По размерам и функциональным возможностям

Большие ЭВМ

Малые ЭВМ

Супер

ЭВМ

Микро ЭВМ или персональный компьютер

Специальные ЭВМ

Слайд 73Большие ЭВМ

Исторически первыми появились большие ЭВМ, элементная база которых

прошла путь от электронных ламп до ИС со сверх высокой

степенью интеграции. Однако их производительность оказалась недостаточной для моделирования экологических систем, задач генной инженерии, управления сложными оборонными комплексами и др.Большие ЭВМ часто называют за рубежом MAINFRAME и слухи об их смерти сильно преувеличены. Как правило они имеют:

производительность не менее 10 MIPS (миллионов операций с плавающей точкой в секунду)

основную память от 64 до 10000 МВ

внешнюю память не менее 50 ГВ

многопользовательский режим работы

Основные направления использования — это решение научно-технических задач, работа с большими БД, управление вычислительными сетями и их ресурсами в качестве серверов.

Примеры:

Семейство mainframe: IBM ES/9000 ( Enterprise System), включает более 18 моделей, реализованных на основе архитектуры IBM390.

Слайд 74Малые ЭВМ

Малые (мини) ЭВМ — надежные, недорогие и удобные

в эксплуатации, обладают несколько более низкими, по сравнению с большими

ЭВМ возможностями.Супер-мини ЭВМ имеют:

емкость основной памяти — 4-512 МВ

емкость дисковой памяти — 2 - 100 ГВ

число поддерживаемых пользователей - 16-512.

Мини-ЭВМ ориентированы на использование в качестве управляющих вычислительных комплексов, в системах несложного моделирования, в АСУП, для управления технологическими процессами.

Родоначальник современных мини-ЭВМ — PDP-11,(programm driven processor -программно-управляемый процессор) фирмы DEC (США).

Слайд 75Супер ЭВМ

Это мощные многопроцессорные ЭВМ с быстродействием сотни миллионов

- десятки миллиардов операций в секунду.

Достичь такую производительность на одном

микропроцессоре по современным технологиям невозможно, в виду конечного значения скорости распространения электромагнитных волн (300000 км/сек), ибо время распространения сигнала на расстояние в несколько миллиметров (размер стороны МП) становится соизмеримым с временем выполнения одной операции. Поэтому суперЭВМ создают в виде высокопараллельных многопроцессорных вычислительных систем.В настоящее время в мире насчитывается несколько тысяч суперЭВМ, начиная от простеньких офисных Cray EL до мощных Cray 3, SX-X фирмы NEC, VP2000 фирмы Fujitsu (Япония), VPP 500 фирмы Siemens (Германия).

Слайд 76Микро ЭВМ или персональный компьютер

ПК должен иметь характеристики, удовлетворяющие

требованиям общедоступности и универсальности:

малую стоимость

автономность эксплуатации

гибкость архитектуры, дающую возможность адаптироваться

в сфере образования, науки, управления, в быту;дружественность операционной системы;

высокую надежность (более 5000 часов наработки на отказ);

Слайд 77Термины микроЭВМ

С понятием микроЭВМ связаны также термины:

Однокристальная ЭВМ [single-chip computer] - МикроЭВМ, выполненная

на одной большой (БИС) или сверхбольшой (СБИС) интегральной микросхеме ;

Одноплатная ЭВМ [single-board computer]

- МикроЭВМ, у которой микропроцессор , микросхемы устройств памяти и подсистемы ввода-вывода а также другие основные компоненты размещены на одной печатной плате ;Однопроцессорная ЭВМ [monoprocessor computer ] - ЭВМ с одним центральным процессором .

Интеллектуальная карточка [smart card ] - Пластиковая карточка со встроенным микропроцессором и памятью. Она может хранить, например, личные сведения, идентификационные шифры для охранных устройств, данные банковского счета и т.д.

Слайд 78Специальные ЭВМ

Специальные ЭВМ ориентированы на решение специальных вычислительных задач или

задач управления. В качестве специальной ЭВМ можно рассматривать также электронные

микрокалькуляторы. Программа, которую выполняет процессор находится в ПЗУ или в ОП. Т.к. машина решает, как правило, одну задачу, то меняются только данные. Это удобно (программу хранить в ПЗУ), в этом случае повышается надежность и быстродействие ЭВМ. Такой подход часто используется в бортовых ЭВМ; управлении режимом работы фотоаппарата, кинокамеры, в спортивных тренажерах.Слайд 79Альтернативная классификация

Базовая ЭВМ [original computer ] - ЭВМ, являющаяся начальной исходной моделью

в серии ЭВМ определенного типа или вида.

Универсальная ЭВМ [universal computer ] -

ЭВМ, предназначенная для решения широкого класса задач. ЭВМ этого класса имеют разветвленную и алгоритмически полную систему операций, иерархическую структуру ЗУ и развитую систему устройств ввода-вывода данных.Специализированная ЭВМ [specialized computer ] - ЭВМ, предназначенная для решения узкого класса определенных задач. Характеристики и архитектура машин этого класса определяются спецификой задач, на которые они ориентированы, что делает их более эффективными в соответствующем применении по отношению к универсальным ЭВМ. К разряду специализированных могут быть отнесены, в частности, - “управляющие”, “бортовые“, “бытовые“ и “выделенные“ ЭВМ (см. ниже).

Слайд 80Альтернативная классификация

Управляющая ЭВМ [control computer ] - ЭВМ, предназначенная для автоматического управления

объектом (устройством, системой, процессом) в реальном масштабе времени. Сопряжение ЭВМ

с объектом управления производится с помощью аналого-цифровых и цифро-аналоговых преобразователей .Бортовая ЭВМ [onboard computer ] - Специализированная управляющая ЭВМ, устанавливаемая на борту транспортного средства (самолета, спутника, корабля, автомобиля и т.п.) и предназначенная для оптимального управления функционированием других бортовых устройств, в частности, связанных с управлением перемещением своего носителя в пространстве.

Выделенная ЭВМ [dedicated computer ] - Разновидность (как правило) однокристальной специализированной ЭВМ, встроенной в какое-либо устройство с целью управления им или передачи ему данных. Используется в бытовой технике и других видах устройств - нагревательных приборах, часах, автомобилях, магнитофонах и т.д.

Бытовая ( домашняя ) ЭВМ [home computer ] - То же, что - домашняя ПЭВМ или домашний ПК.

Слайд 81Способ структурной организации

Для увеличения скорости ЭВМ в ее состав включают

несколько процессоров различают:

Однопроцессорные ЭВМ

Мультипроцессорные ЭВМ (можно также выделить квазипроцессорные ЭВМ),

которые состоят как из однотипных, так и из разнотипных процессоров (неоднородные ЭВМ).Слайд 82По режиму и месту работы

Активная ЭВМ [active computer ] - ЭВМ, входящая

в состав многомашинного комплекса (см. вычислительная сеть) и ведущая в данный

момент обработку или готовая к немедленной обработке задач пользователей.Дублирующая ( резервная ) ЭВМ [slave (standby) computer] - ЭВМ, ориентированная на выполнение тех же операций, что и активная ЭВМ, но работающая в т.н. “дежурном” или “ждущем” режиме, предусматривающем передачу ей функций активной машины в случаях сбоев в работе или выхода из строя последней.

Периферийная ЭВМ [peripheral (satellite) computer] - 1. ЭВМ, управляющая периферийным оборудованием;

ЭВМ, выполняющая вспомогательные функции, например, предварительный сбор и обработку данных.

Подчиненная ЭВМ [slave computer ] - В многомашинных системах - ЭВМ, работающая под управлением главной ( центральной) ЭВМ.

Псевдоведущая ЭВМ [take host] - ЭВМ, осуществляющая сбор статистики о работе вычислительной сети.

Слайд 83По функциям , выполняемым в многомашинных системах ( комплексах )

Главная ( ведущая , центральная ) ЭВМ , ГВМ , хост[master (host, central) computer] -

В многомашинных вычислительных комплексах

ЭВМ, осуществляющая управление другими ЭВМ, организацию работ в системе (вычислительной

сети) и производящая основную обработку информации .В телекоммуникационных вычислительных сетях - ЭВМ, обеспечивающая обслуживание сети, передачу сообщений и выполнение программ, связанных с дополнительными функциями или задачами.

Сервер [server] -

В локальных вычислительных сетях - специализированная ЭВМ, управляющая использованием разделяемых между терминалами сети дорогостоящих ресурсов системы, например, - внешней (дисковой) памяти, баз данных, средств связи, принтеров и т.д. По признаку характера разделяемых ресурсов различают файловые серверы , серверы приложений и др. (см. ниже);

ЭВМ, выполняющая определенные функции обслуживания вычислительной сети.

Слайд 84Виды серверов 1

Почтовый сервер [mail server] - Сервер, обеспечивающий поддержку обмена электронной

почтой в рамках сетей Интернет и Интранет.

Сервер-издатель [publishing server] - Сервер с базой данных, которые рассылаются

(“публикуются“) по другим станциям сети.Сервер приложений [application server] - Сервер, управляющий работой локальной сети ЭВМ при выполнении каких-либо прикладных задач автоматизированной системы. Примерами такого рода задач могут служить: обеспечение связи с другими локальными и/или телекоммуникационными системами, коллективное использование печатающих устройств и т.п. В указанной связи различают также: серверы связи (см. ниже) и сервер печати [print server].

Слайд 85Виды серверов 2

Сервер ( станция ) связи [gateway server ] - Специализированный узел (станция, сервер) локальной сети,

обеспечивающий доступ терминалов этой сети к внешней сети передачи данных

и другим вычислительным сетям.Сервер ( станция ) телексной связи [telex server] - Сервер, обеспечивающий связь данной локальной сети и отдельных ее узлов с телексной сетью.

Слайд 86Виды серверов 3

Файловый сервер , файл-сервер [file server] - Сервер, управляющий созданием и использованием

информационных ресурсов локальной сети (системы ЭВМ), включая доступ к ее БД и отдельным

файлам, а также их защиту. Для поддержки и ведения “больших” и “очень больших” баз данных, содержащих десятки миллионов записей, используются т.н. многопроцессорные системы, способные эффективно обрабатывать большие объемы информации и обладающие хорошим соотношением характеристик цена/производительность. Разновидностью файловых серверов, предназначенных для обеспечения резервного копирования данных абонентов сети, являются: NFS (Network File System ) и NAS(Network Attached Storage ). Более гибкими и перспективными считаются NAS . Существует несколько разновидностей серверов NAS , использующих различные системы внешней памяти, в том числе - комбинированные.Слайд 87Виды серверов 4

Телефонный сервер API [TSAPI - Telephony Server Application Programming Interface ] –

Сервер, предназначенный для управления вызовами, мониторинга устройств, маршрутизации вызовов и

других функций связи. Разработан фирмой Novell при участии фирмы AT&T.Мэйнфрэйм [mainframe ] - Мощная, высокопроизводительная ЭВМ с весьма значительным объемом оперативной и внешней памяти, которая выполняет функции сервера в развитых локальных вычислительных сетях (ЛВС) с большим числом периферийных ЭВМ и терминалов (например, ЛВС больших организаций, фирм, учебных заведений и т.д.). Данный термин многими специалистами считается устаревшим, в связи с развитием персональных и мини-ЭВМ

Слайд 88Виды серверов 5

Псевдо-УАТС, телефонный телекоммуникационный сервер, – Объединение в одном

продукте готового аппаратного обеспечения, серверного программного обеспечения и программного обеспечения

телефонии для выполнения функций учрежденческой автоматической телефонной станции (УАТС). Указанный сервер выполняет также функции, автоматического секретаря, голосовой почты и факсимильной связи.Удаленный файловый сервер [remote file server] - Сервер, обеспечивающий телеобработку и управление информационными ресурсами распределенной сети на расстоянии через каналы связи.

Слайд 89Виды серверов 6

Хост-узел [host ] - Отдельная ЭВМ или их группа, имеющая

прямое сетевое соединение с Интернет, и предоставляющая пользователям теледоступ к своим информационным ресурсам,

программно-техническим средствам и службам.WAIS (Wide Area Information Server) - “ Сервер глобальной информации” предоставляет доступ к неструктурированной информации, распределенной по сети Интернет. Использует простой язык управления, близкий к естественному. Поиск информации производится по ключевым словам.

Слайд 90Требования к ИВС, определяющие класс используемых ЭВМ

Структура информационно-вычислительной системы (ИВС)

должна в определенной степени соответствовать оргштатной структуре, и, следовательно, является

иерархической многоуровневой с большим количеством информационных связей между подразделениями. Сами связи представляют собой сообщения, содержащие информационные ресурсы и действуют как между уровнями (по вертикали), так и по горизонтали, а сама информационная система представляется совокупностью иерархически связанных информационных подсистем.Слайд 91Масштабируемость ИВС

Масштабируемость – это способность (свойство) системы увеличивать свою производительность

за счет подключения дополнительных вычислительных ресурсов, как аппаратных, так и

программных.Слайд 92Масштабируемость

Вертикальная масштабируемость Увеличение производительности каждого компонента системы c целью повышения

общей производительности.

Горизонтальная масштабируемость Разбиение системы на более мелкие структурные

компоненты и разнесение их по отдельным физическим машинам (или их группам) и/или увеличение количества серверов параллельно выполняющих одну и ту же функцию. Слайд 93Совместимость и мобильность программного обеспечения

Совместимость программного обеспечения - мера того,

насколько просто объединить различные программные изделия вместе для нового применения.

Мобильность – возможность работы ПИ в различных ОС.

Слайд 94Классификация персональных компьютеров (ПК)

По конструктивным особенностям можно классифицировать ПК так:

Стационарные

(настольные)

Переносимые:

портативные

блокноты

карманные

электронные секретари

электронные записные книжки

Слайд 95Понятие о суперЭВМ, мини- и микроЭВМ, особенности их архитектуры

По совокупности

технических характеристик (производительности, объёму памяти, принципу реализации, характеру применения, стоимости,

габаритным размерам, и др.) различают высокопроизводительные, сверхвысокопроизводительные, средние, малые (мини-) и микроЭВМ.Высокопроизводительные ЭВМ предназначены для решения задач комплексного проектирования и использования в системах управления высшего звена.

Сверхвысокопроизводительные модели ЭВМ получили за рубежом название суперЭВМ, что в первую очередь означает широкие возможности, предоставляемые пользователю, а также способность системы проводить по сложности обработку данных.

Слайд 96Понятие о суперЭВМ, мини- и микроЭВМ, особенности их архитектуры (2)

Средние

ЭВМ имеют производительность ниже 1 млн. оп/с, развитую конфигурацию ввода-вывода

и служат для применения в системах обработки информации коллективного пользования, отраслевых системах автоматизированного проектирования и системах управления.К малым (мини-ЭВМ) относят ЭВМ с производительностью процессора порядка сотен тысяч операций в секунду, ограниченным объёмом оперативной памяти, упрощённой организацией ввода-вывода.

МикроЭВМ - это обычно ЭВМ с малой ёмкостью оперативной памяти, низкой разрядностью и познаковым вводом-выводом.

Слайд 97Понятие о суперЭВМ, мини- и микроЭВМ, особенности их архитектуры (3)

Можно

предложить следующую классификацию средств вычислительной техники, в основу которой положено

их разделение по быстродействию.СуперЭВМ для решения крупномасштабных вычислительных задач, для обслуживания крупнейших информационных банков данных.

Большие ЭВМ для комплектования ведомственных, территориальных и региональных вычислительных центров.

Средние ЭВМ широкого назначения для управления сложными технологическими производственными процессами. ЭВМ этого типа могут использоваться и для управления распределенной обработкой информации в качестве сетевых серверов.

Слайд 98Понятие о суперЭВМ, мини- и микроЭВМ, особенности их архитектуры (4)

Персональные

и профессиональные ЭВМ, позволяющие удовлетворять индивидуальные потребности пользователей. На базе

этого класса ЭВМ строятся автоматизированные рабочие места (АРМ) для специалистов различного уровня.Встраиваемые микропроцессоры, осуществляющие автоматизацию управления отдельными устройствами и механизмами.

Слайд 101Учебные вопросы:

Обобщенная структурная схема ЭВМ.

Состав устройств, их назначение и взаимодействие.

Принцип

программного управления.

Фон-Неймановская архитектура ЭВМ.

Последовательность прохождения информации при обработке на ЭВМ.

Принципы

создания элементов структур современных ЭВМ: модульность построения, магистральность, иерархия управления Слайд 102Обобщенная структурная схема ЭВМ

ЭВМ любого класса состоит из пяти основных

компонент: арифметическо-логического устройства (АЛУ), устройства управления (УУ), оперативного запоминающего устройства

(ОЗУ), устройства вывода информации (УвывИ), устройства ввода информации (УВвИ). АЛУ и УУ в современном персональном компьютере нечто иное как процессор, УВывИ – монитор, принтер; УВвИ – клавиатура, мышка.Слайд 104Принцип программного управления

Основным принципом построения всех современных ЭВМ является программное

управление. В основе его лежит представление алгоритма решения любой задачи

в виде программы вычислений.Принцип программного управления заключается в том, что после сообщения машине адреса первой команды программы и занесения тела этой команды в регистр команд, программа управляет сама собой.

Принцип программного управления может быть осуществлен различными способами. Стандартом для построения практически всех ЭВМ стал способ, описанный Дж. фон Нейманом в 1945 г. при построении еще первых образцов ЭВМ.

Слайд 106Фон-Неймановская архитектура ЭВМ

Процессор выполняет логические и арифметические операции, определяет их

порядок, указывает источники данныхи приемники результатов, работает под управлением программы.

Условно считают, что процессор состоит из арифметико-логического устройства (АЛУ), устройства управления (УУ), регистров общего назначения (РОН) и кэш-памяти.

АЛУ выполняет арифметические и логические операции, в РОН хранятся промежуточные данные. Кэш-память служит для повышения быстродействия процессора, УУ отвечает за порядок выполнения команд программы.

Программа - это набор команд, составленный человеком и выполняемый ЭВМ.

Системная шина служит для передачи информации между процессором и остальными устройствами.

Оперативное запоминающее устройство (ОЗУ) используется для кратковременного хранения текущей информации

Слайд 107Фон-Неймановская архитектура ЭВМ (2)

В постоянном запоминающем устройстве (ПЗУ) хранится информация,

которая не изменяется при работе ЭВМ.

Внешние запоминающие устройства (ВЗУ)

предназначены для долговременного хранения информации.

К устройствам ввода информации относятся клавиатура, мышь, сканер, цифровая видеокамера, микрофон и другие.

К устройствам вывода относятся монитор, принтер, плоттер, колонки и другие. Модем относится и к устройствам ввода, и к устройствам вывода информации.

Слайд 109Принципы создания элементов структур современных ЭВМ: модульность построения, магистральность, иерархия

управления

Модульность это - построение компьютера на основе набора модулей. Модуль

представляет собой конструктивно и функционально законченный электронный блок в стандартном исполнении. Магистральность - это способ связи между различными модулями компьютеров, т.е. входные все и выходные устройства подсоединены одними и теми же проводами, называемыми шинами.

Слайд 110Тема 4

Функциональная и структурная организация ЭВМ и ВС, периферийные устройства,

организация ввода-вывода

Слайд 111Учебные вопросы:

Общие принципы функциональной и структурной организации современных ЭВМ и

ВС.

Организация функционирования ЭВМ с магистральной архитектурой.

Основные характеристики центральных и периферийных

устройств, системной шины. Взаимодействие центральных и периферийных устройств, организация ввода-вывода информации.

Классификация периферийных устройств.

Структурная организация и взаимодействие узлов и устройств ЭВМ при выполнении основных команд ЭВМ.

Системы адресации.

Технология выполнения основных команд ЭВМ.

Слайд 112Общие принципы функциональной и структурной организации современных ЭВМ и ВС

Электронные

вычислительные машины включают, кроме аппаратурной части и программного обеспечения (ПО),

большое количество функциональных средств. К ним относятся коды, с помощью которых обрабатываемая информация представляется в цифровом виде: арифметические коды - для выполнения арифметических преобразований числовой информации; помехозащищенные коды, используемые для защиты информации от искажений; коды формы, определяющие, как должна выглядеть обрабатываемая в ЭВМ информация при отображении; цифровые коды аналоговых величин (звука, “живого видео”) и др.Слайд 113Общие принципы функциональной и структурной организации современных ЭВМ и ВС

Кроме

кодов на функционирование ЭВМ оказывают влияние алгоритмы их формирования и

обработки, технология выполнения различных процедур (например, начальной загрузки операционной системы, принятой в системе технологии обработки заданий пользователей и др.); способы использования различных устройств и организация их работы (например, организация системы прерываний или организация прямого доступа к памяти), устранение негативных явлений (например, таких, как фрагментация памяти) и др.Слайд 114Организация функционирования ЭВМ с магистральной архитектурой

1 шаг:

Адрес очередной команды->ША

Выборка из ОП->ШУ

2 шаг:

ОП получает сигнал «выборка из ОП»,

считывает адрес с ША, находит заданную ячейку и совершает следующие действия: Содержимое ячейки->ШД Сигнал «выполнено ОП» ->ШУ 3 шаг: Процесор получает сигнал «выполнено ОП» и тело команды (с ШД) и направляет тело через внутренюю магистраль в регистр команд ШД->регистр команд

Слайд 115Организация функционирования ЭВМ с магистральной архитектурой

4 шаг:

В регистре команд анализируются

адресная и операционная часть Операционная часть->в блок управления (для выработки