Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

ЭВМ И ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА

Содержание

- 1. ЭВМ И ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА

- 2. СТРУКТУРА КУРСАЛекции + практические 2. Лабораторные работы3. Зачет4. Курсовая работа5. Экзамен

- 3. Литература1. Горнец Н.Н. Периферийные устройства современных вычислительных

- 4. Классы задач 1. Научно-технические задачи.Требования.

- 5. Слайд 5

- 6. Слайд 6

- 7. Слайд 7

- 8. Классификация интерфейсов

- 9. Слайд 9

- 10. Слайд 10

- 11. Способы повышения производительности ВСувеличением быстродействия всех его

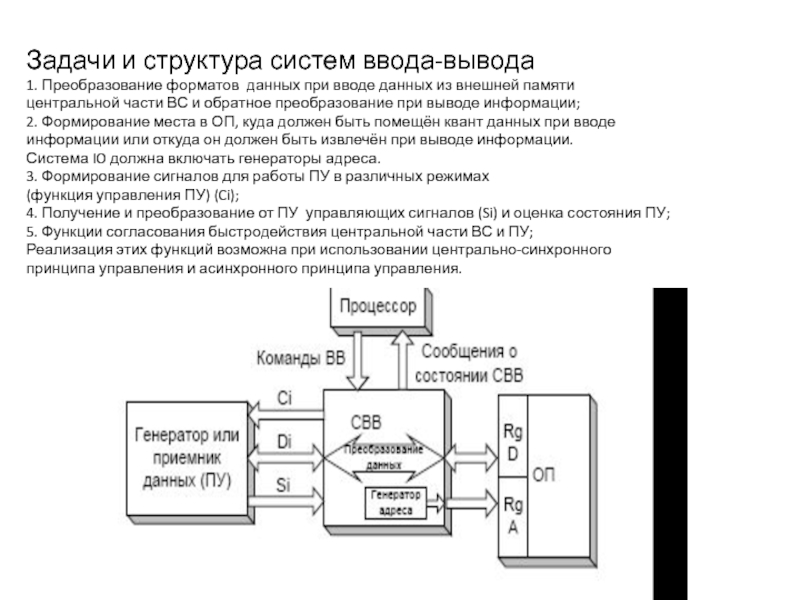

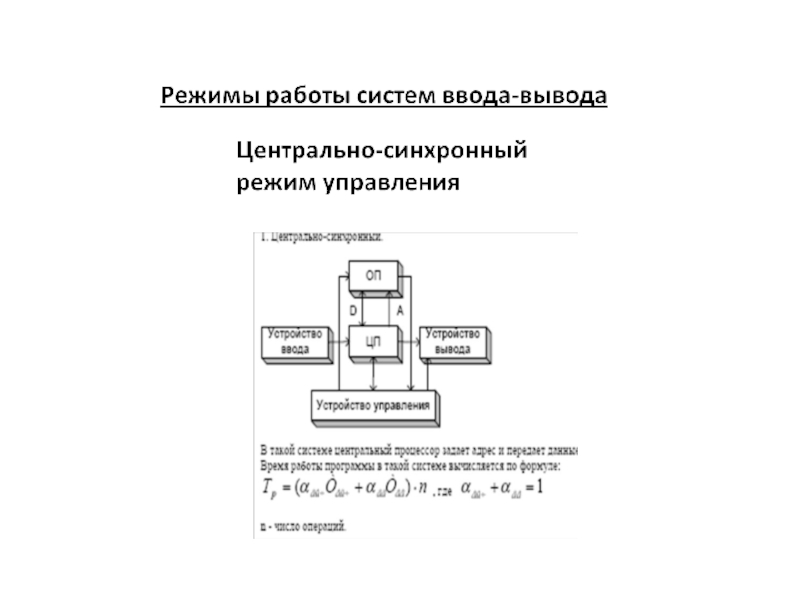

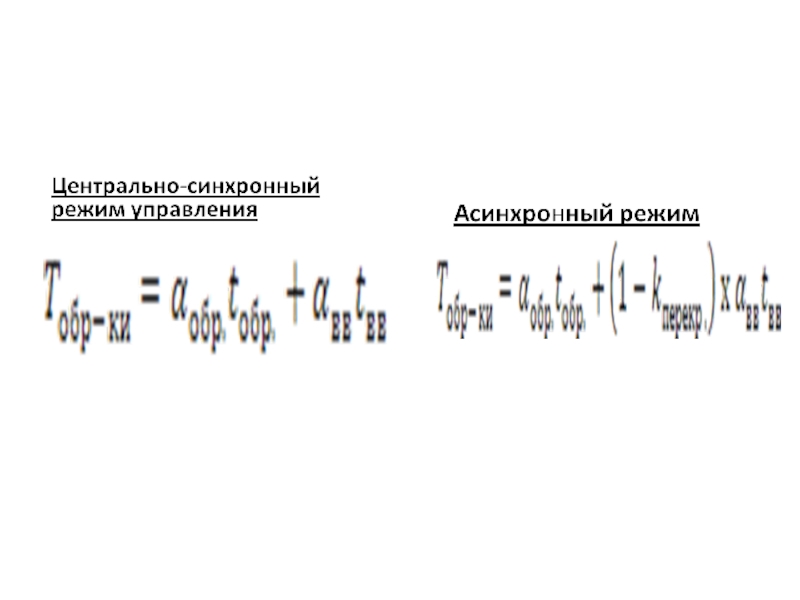

- 12. Задачи и структура систем ввода-вывода 1. Преобразование

- 13. Слайд 13

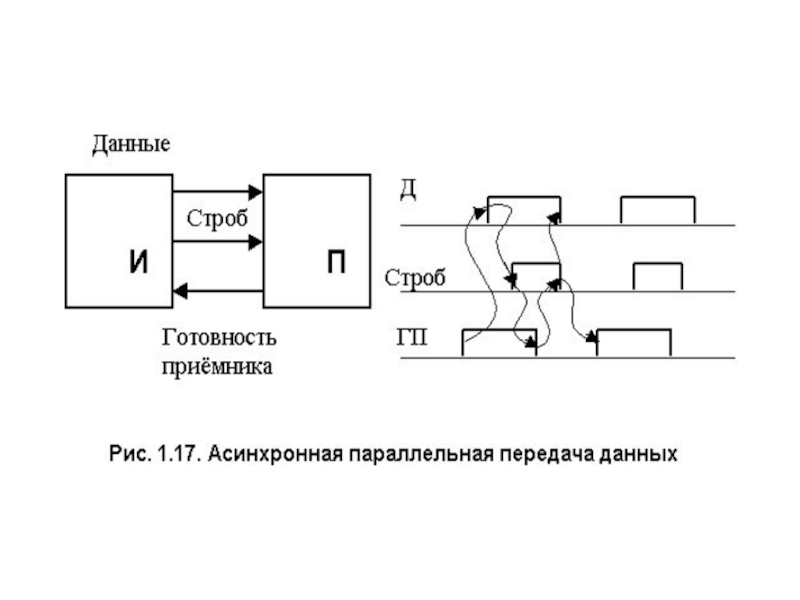

- 14. Асинхронный режим

- 15. Слайд 15

- 16. Параллелизм работы ВС обеспечиваетсяВо время подготовки квантов

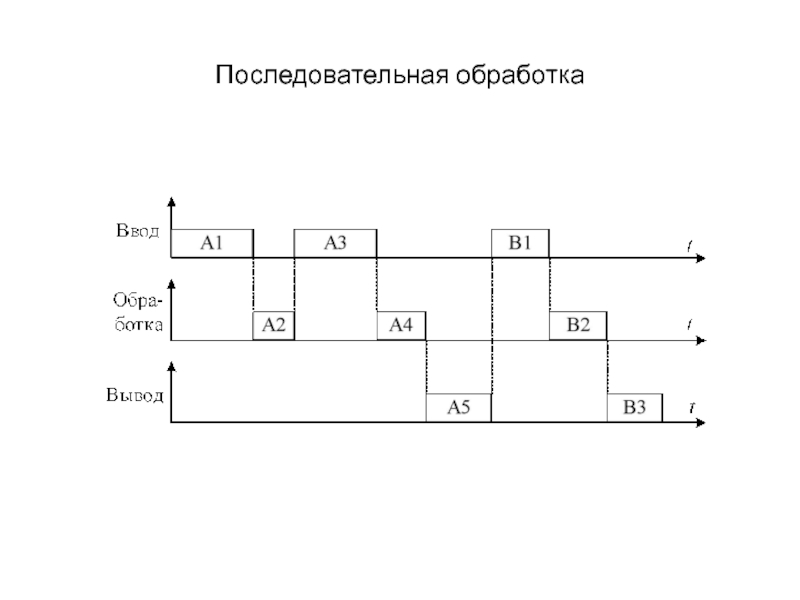

- 17. Последовательная обработка

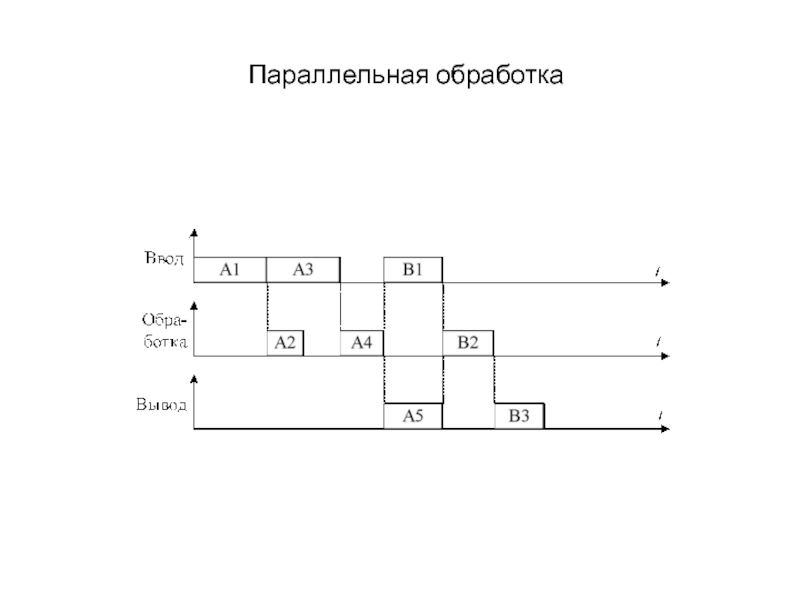

- 18. Параллельная обработка

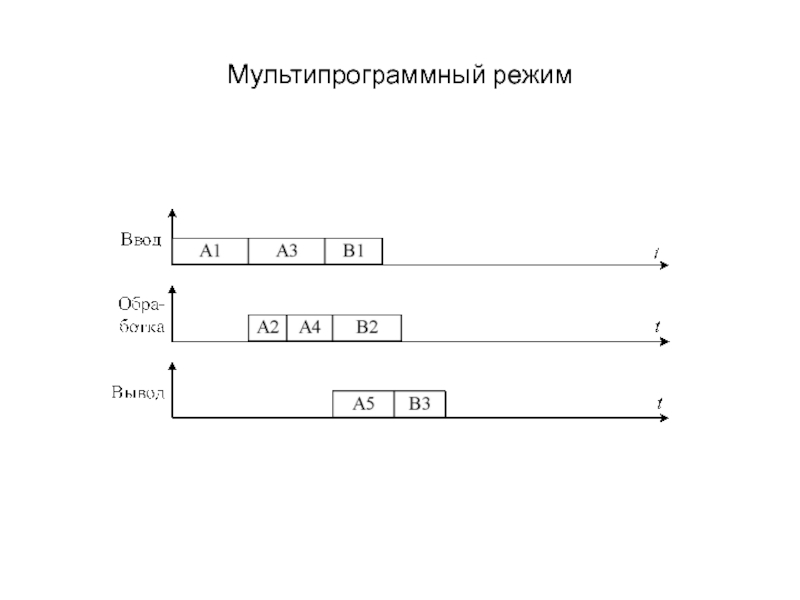

- 19. Мультипрограммный режим

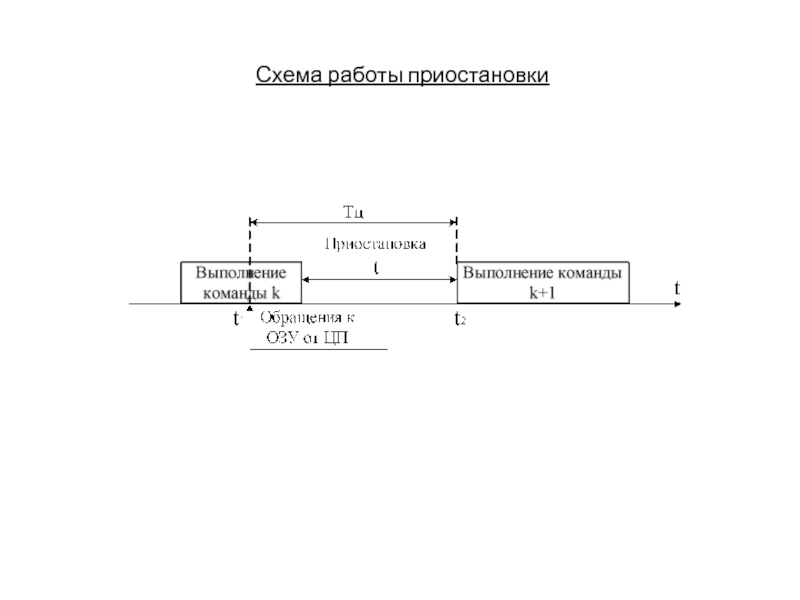

- 20. Схема работы приостановки

- 21. Слайд 21

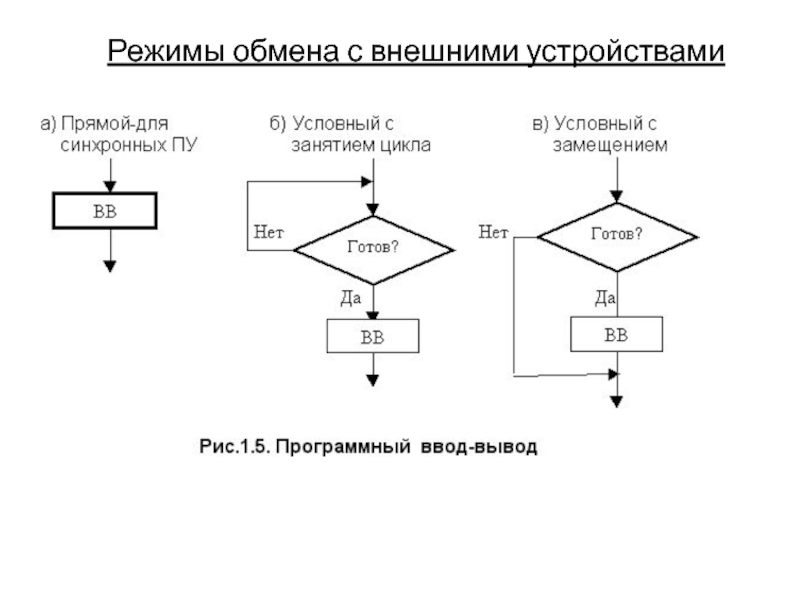

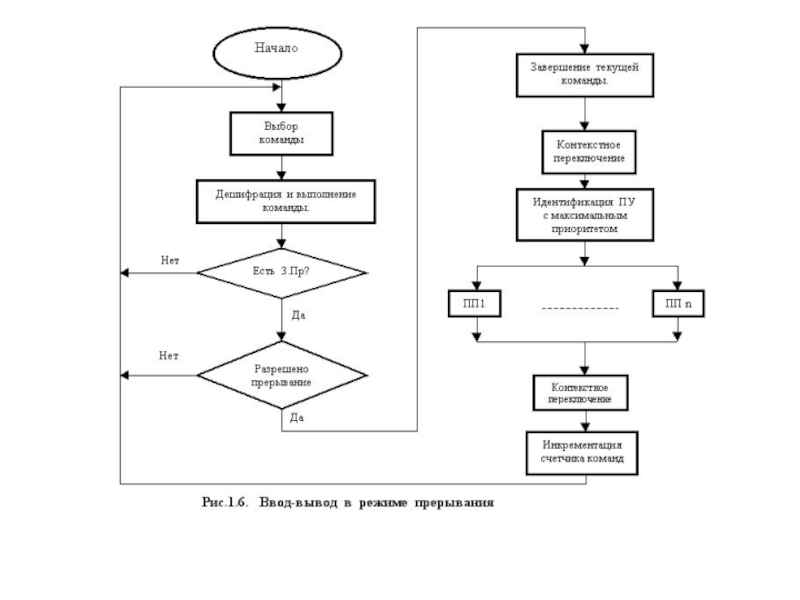

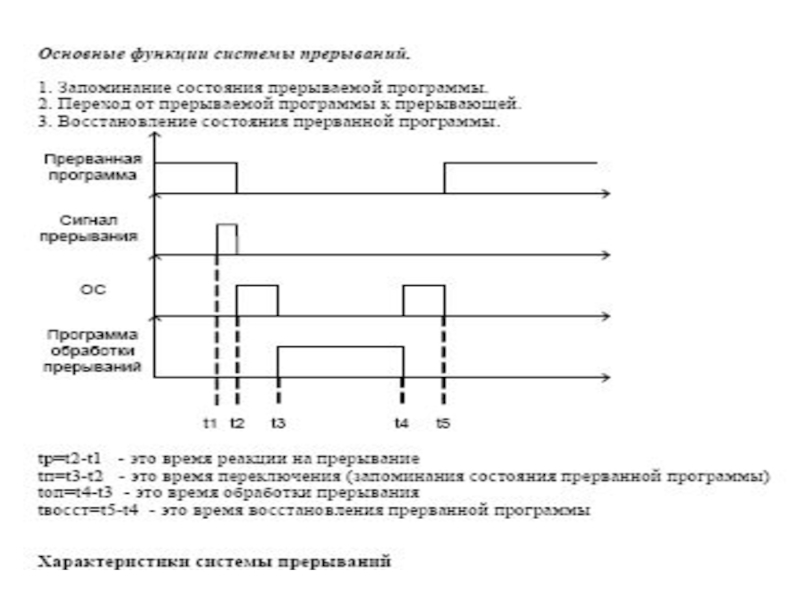

- 22. Режимы обмена с внешними устройствами

- 23. Слайд 23

- 24. Слайд 24

- 25. Слайд 25

- 26. Слайд 26

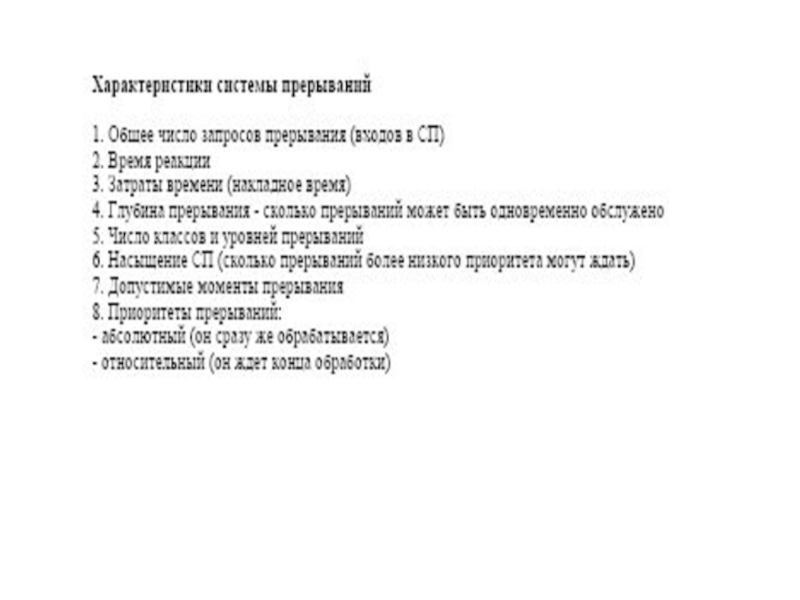

- 27. Глубина прерываний

- 28. Слайд 28

- 29. Слайд 29

- 30. Слайд 30

- 31. Слайд 31

- 32. Слайд 32

- 33. Слайд 33

- 34. Слайд 34

- 35. Маскирование прерываний

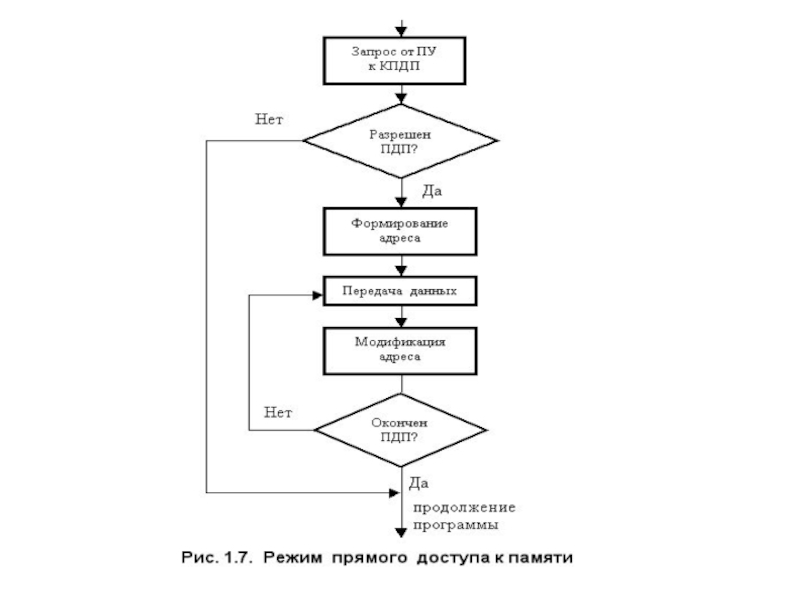

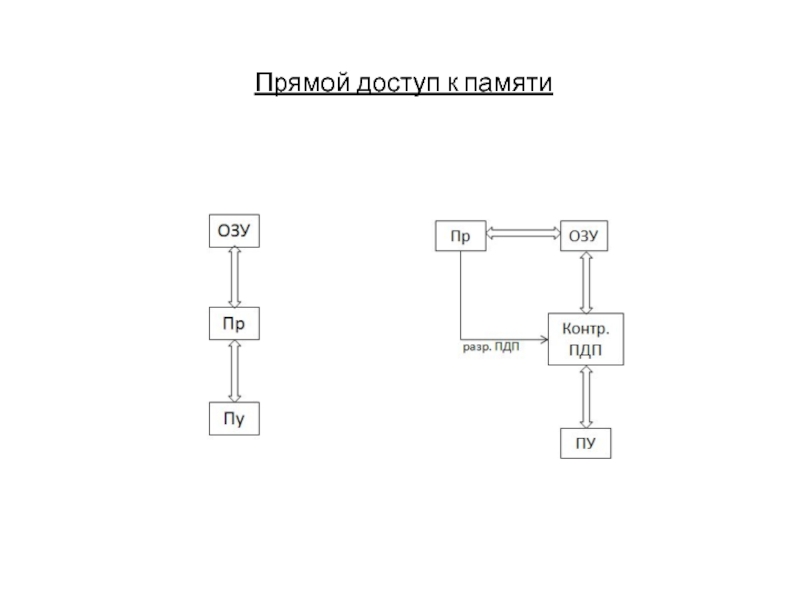

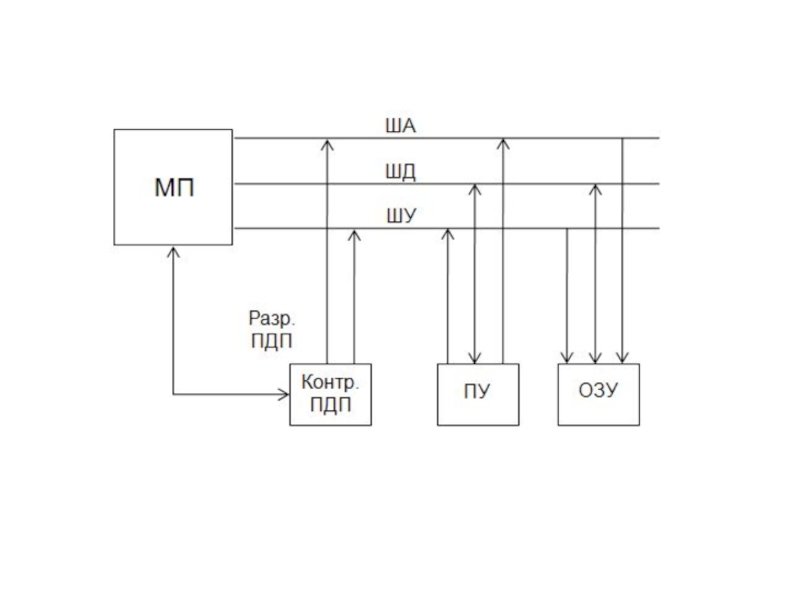

- 36. Прямой доступ к памяти

- 37. Слайд 37

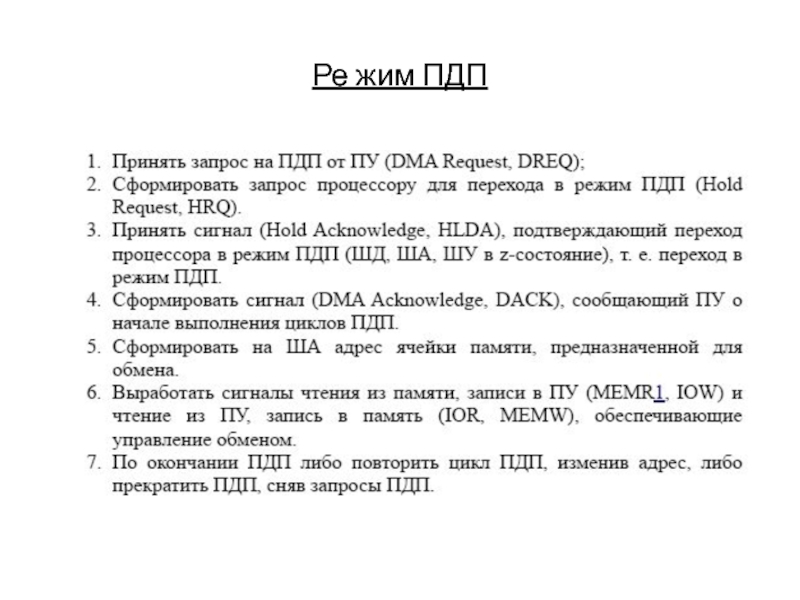

- 38. Ре жим ПДП

- 39. Слайд 39

- 40. Слайд 40

- 41. Слайд 41

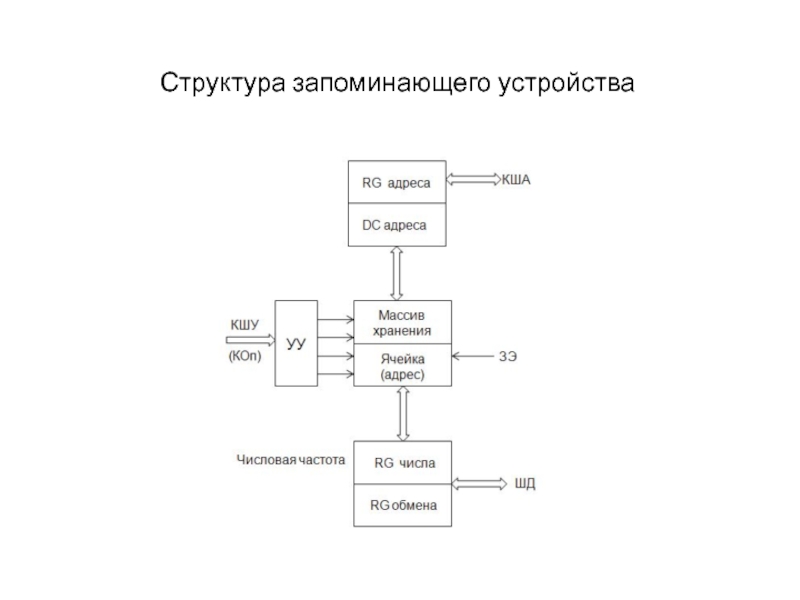

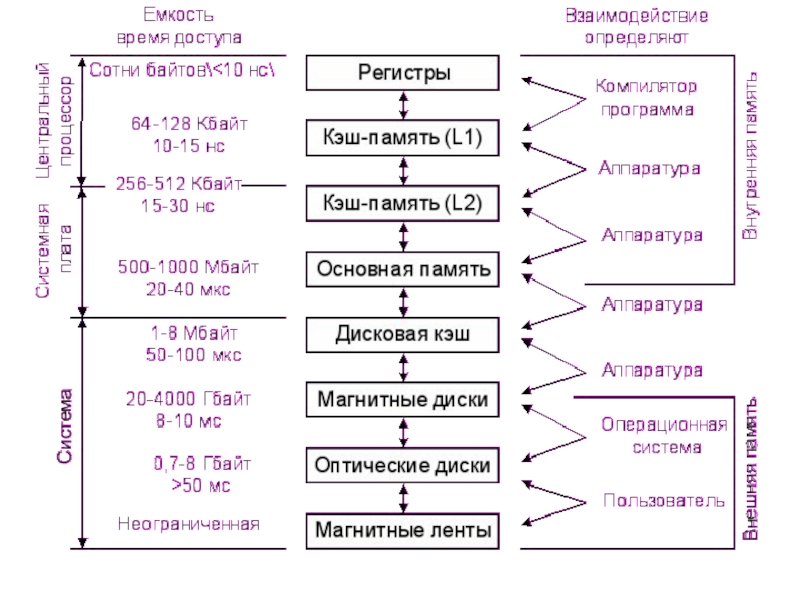

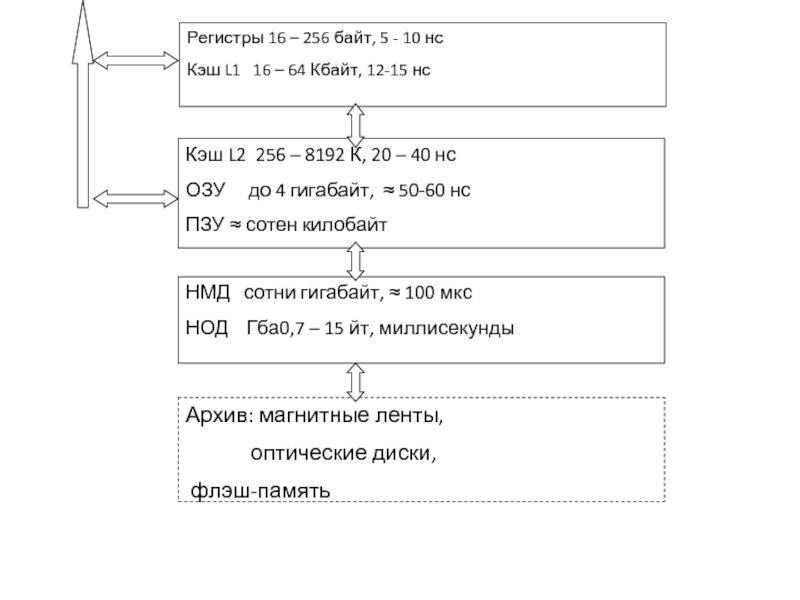

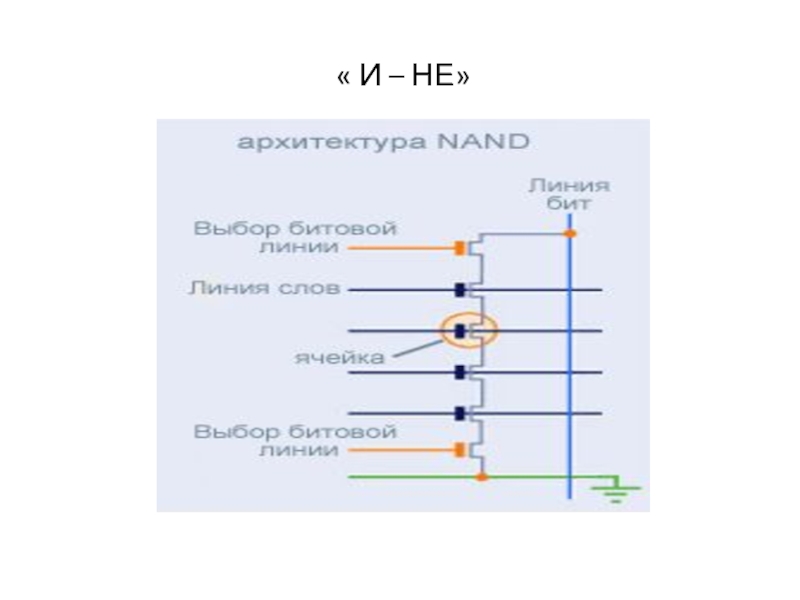

- 42. Структура запоминающего устройства

- 43. Слайд 43

- 44. Слайд 44

- 45. Слайд 45

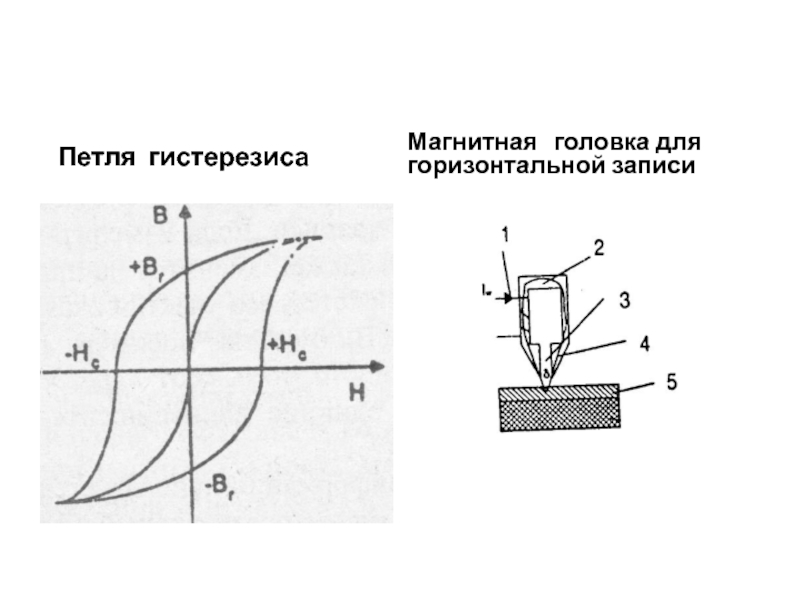

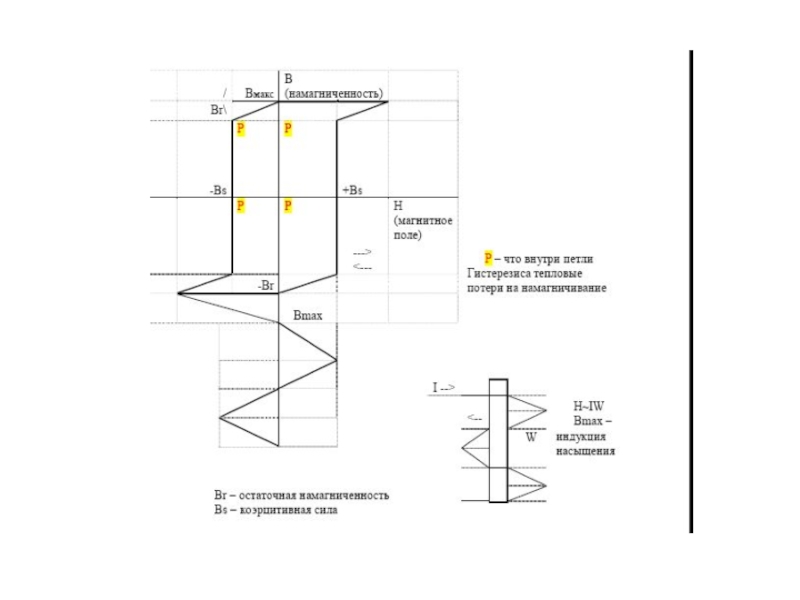

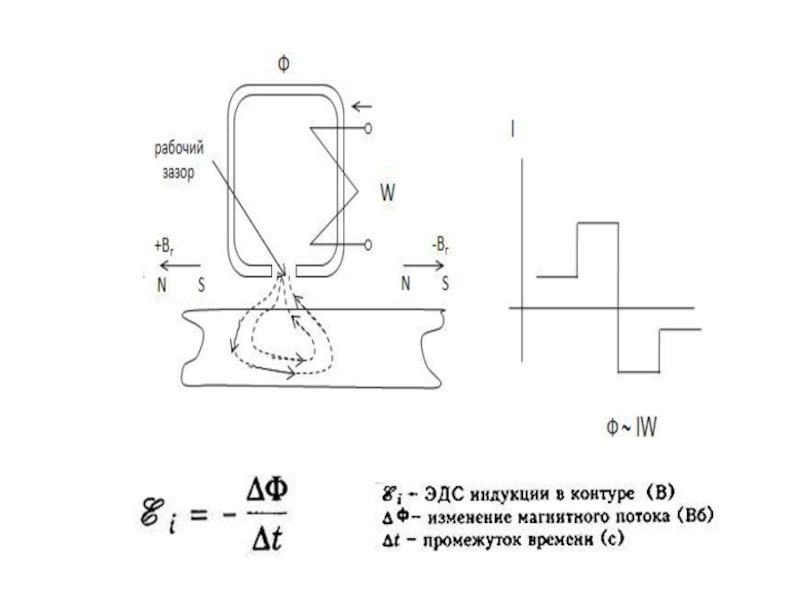

- 46. Петля гистерезисаМагнитная головка для горизонтальной записи

- 47. Слайд 47

- 48. Слайд 48

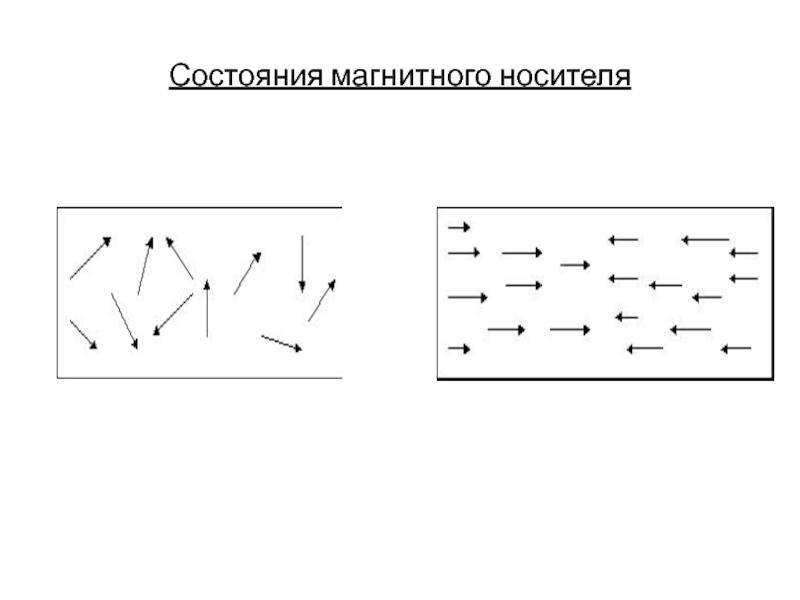

- 49. Состояния магнитного носителя

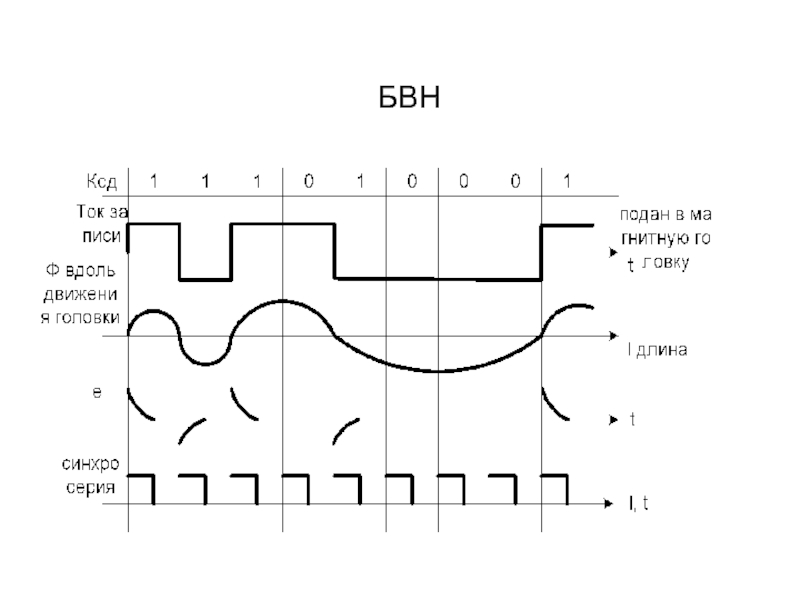

- 50. БВН

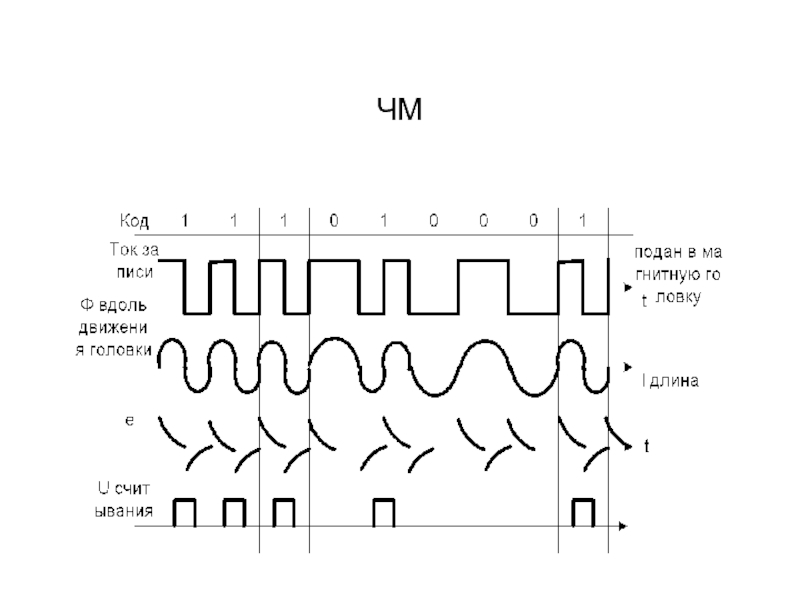

- 51. ЧМ

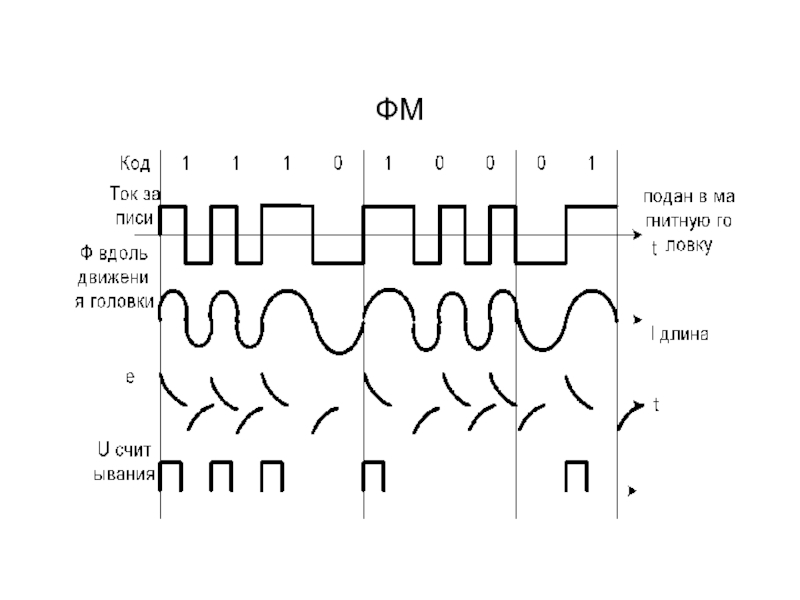

- 52. ФМ

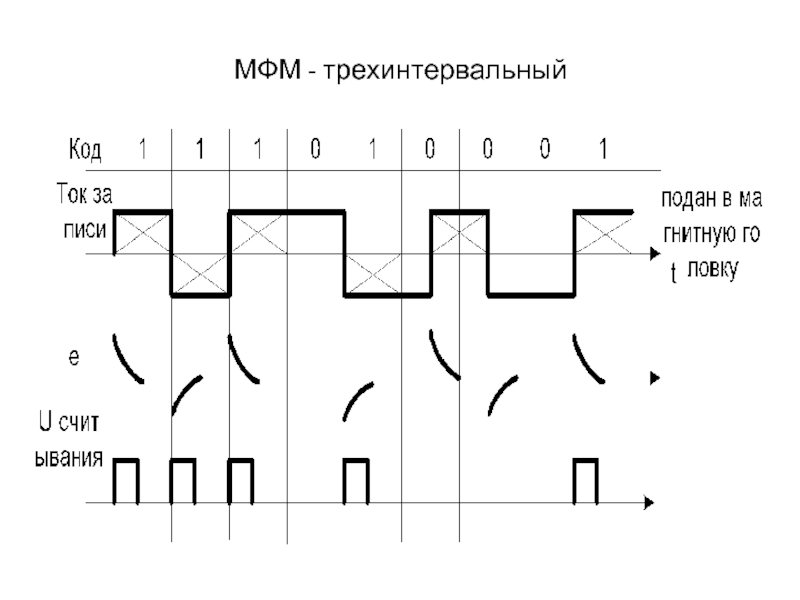

- 53. МФМ - трехинтервальный

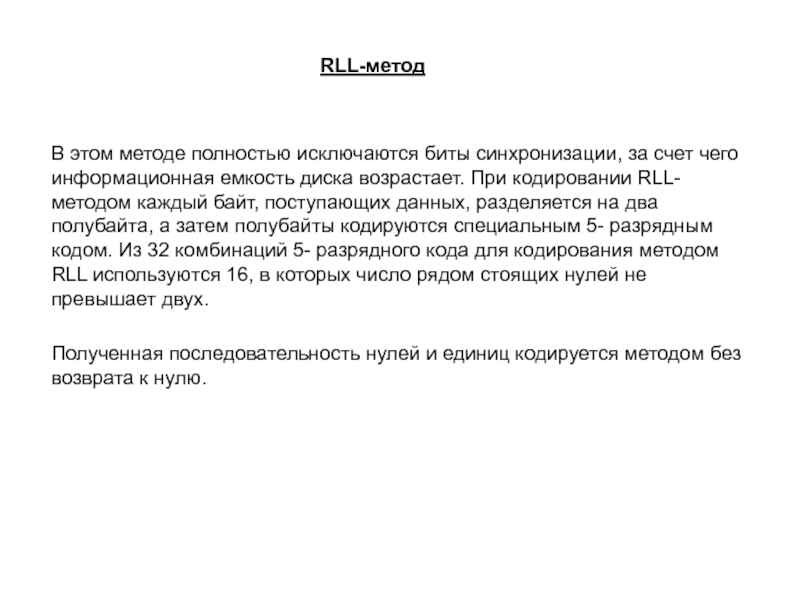

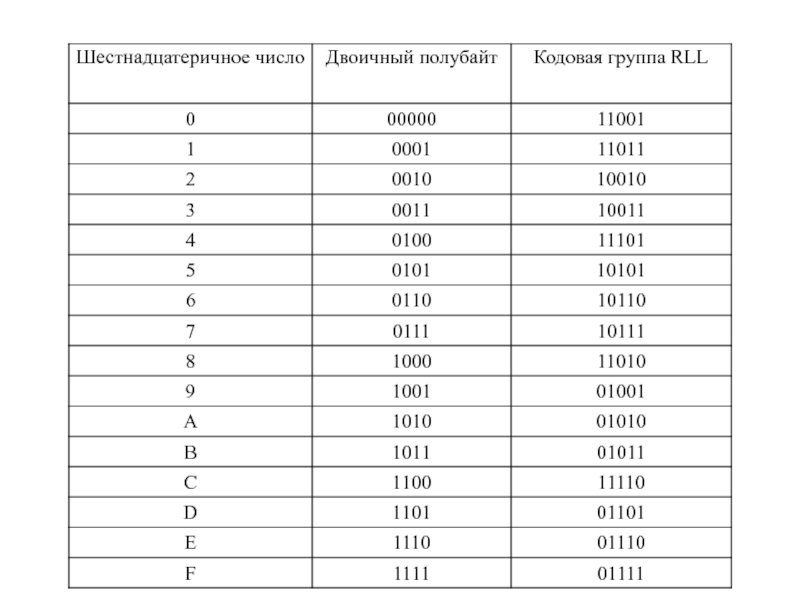

- 54. RLL-методВ этом методе полностью исключаются биты синхронизации,

- 55. Слайд 55

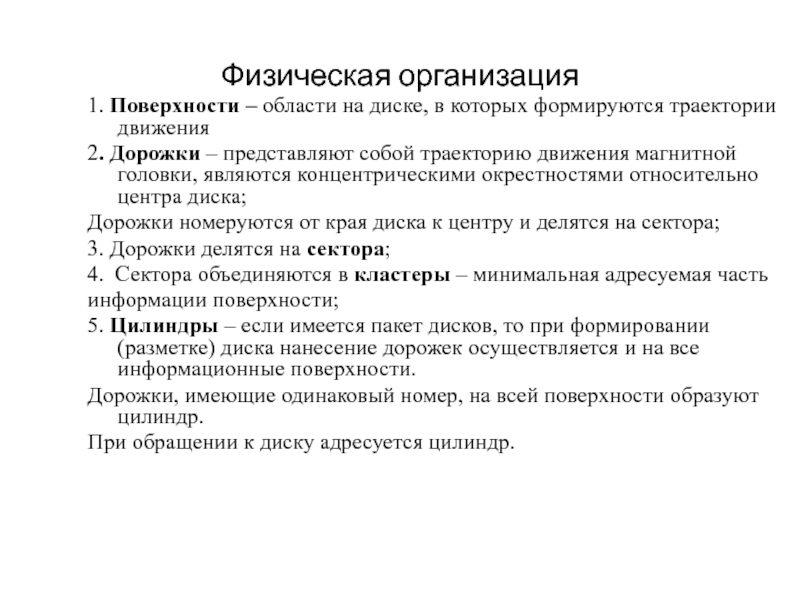

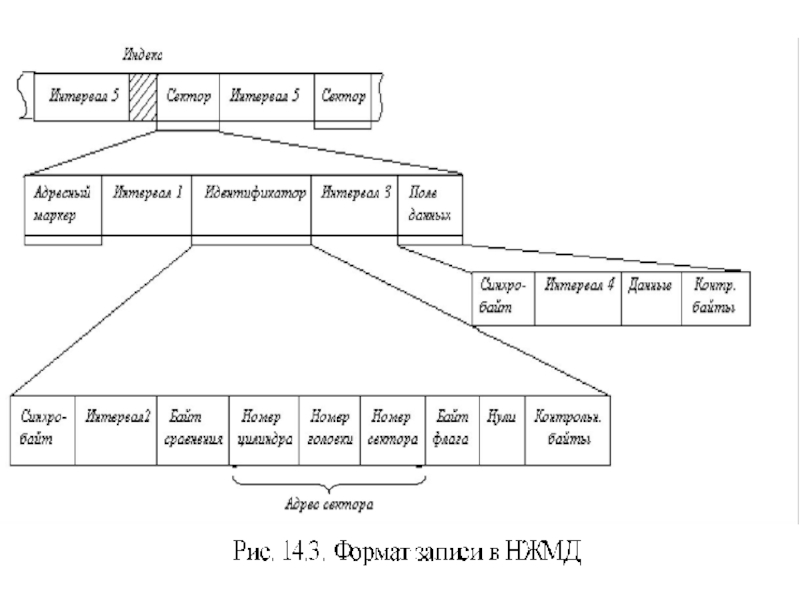

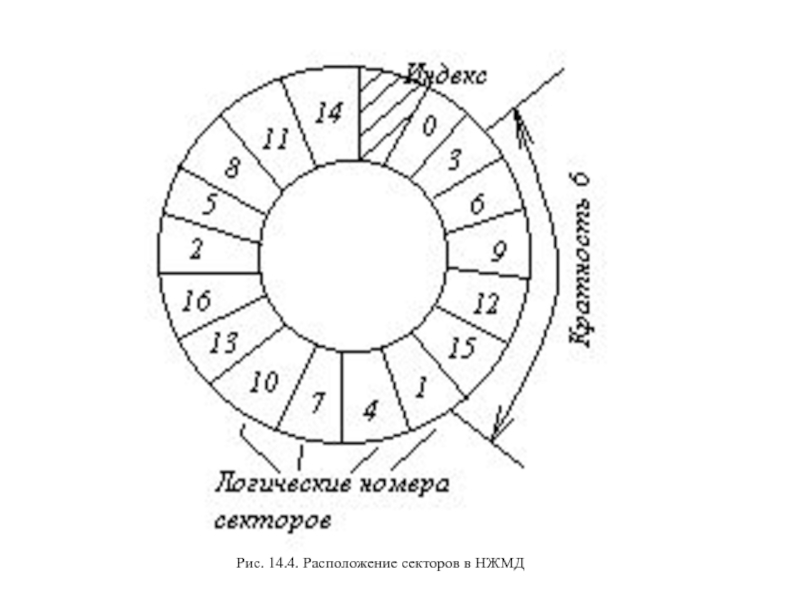

- 56. Физическая организация1. Поверхности – области на диске,

- 57. Слайд 57

- 58. Слайд 58

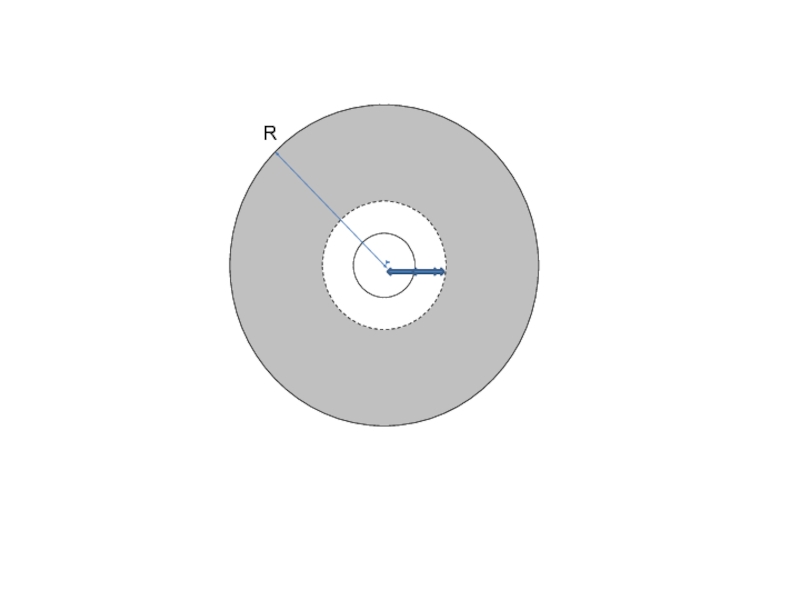

- 59. Расчет характеристикплотность поперечной записи информации на диске

- 60. R

- 61. Логическая организация1. загрузочный сектор, включающий программу начала

- 62. Слайд 62

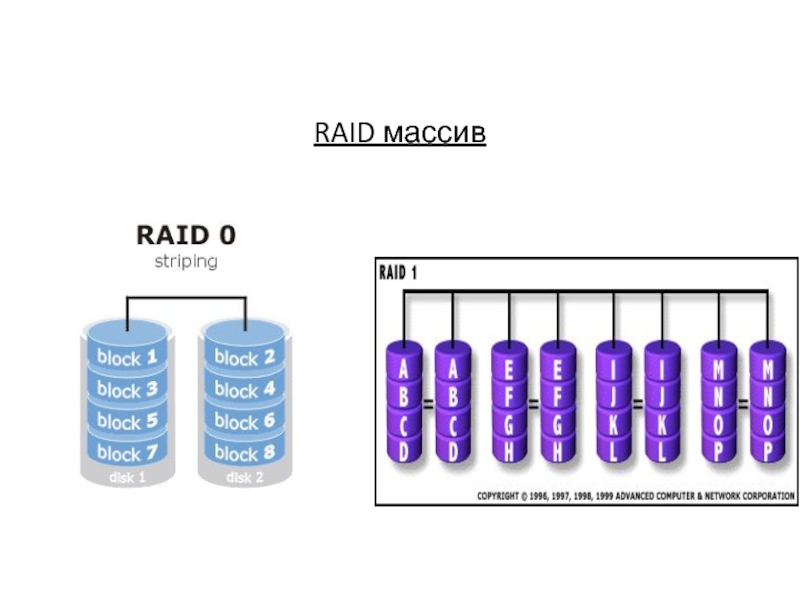

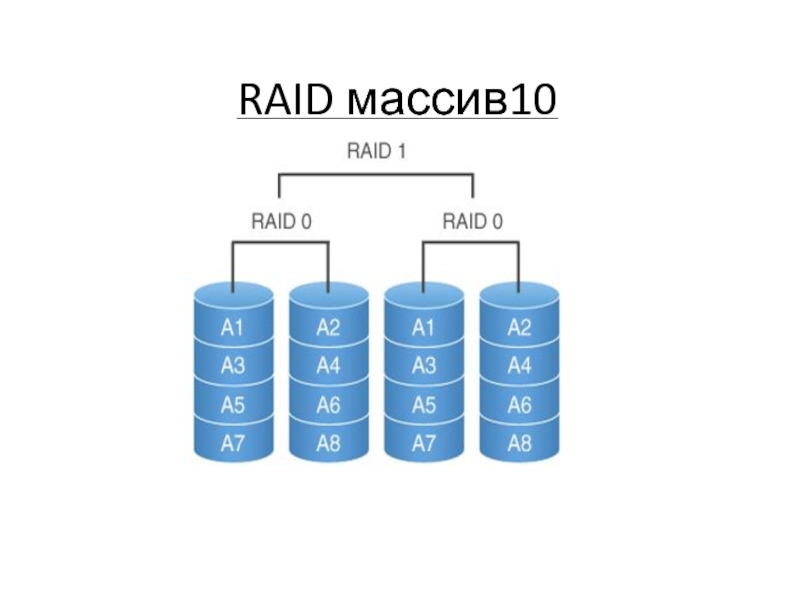

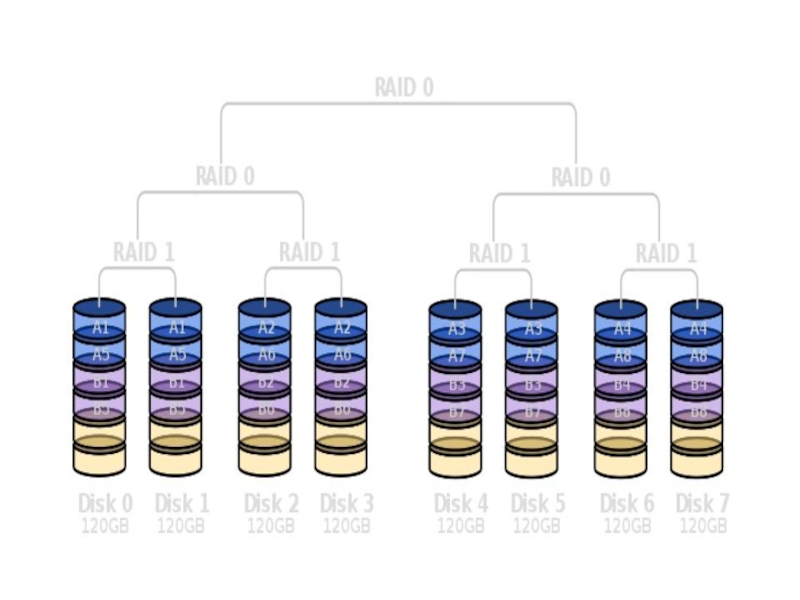

- 63. .RAID-0Представляет собой виртуальный диск, разбитый на зоны,

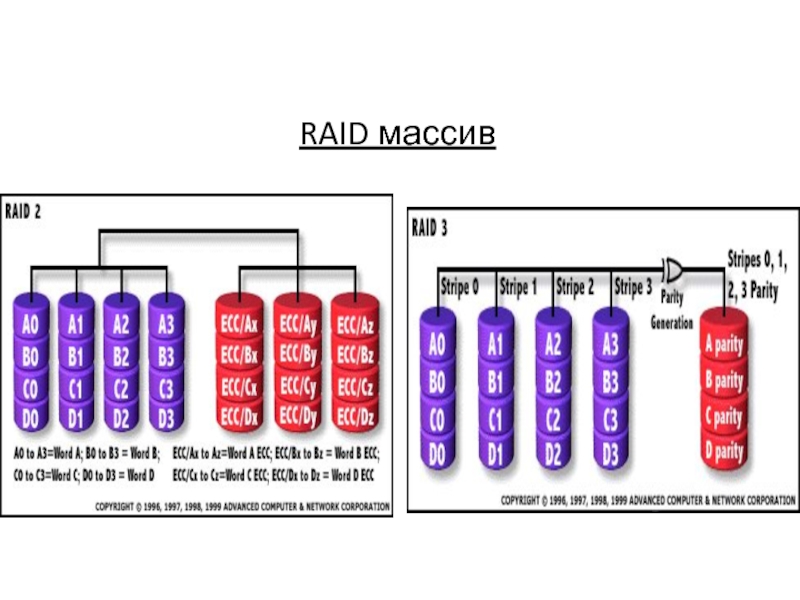

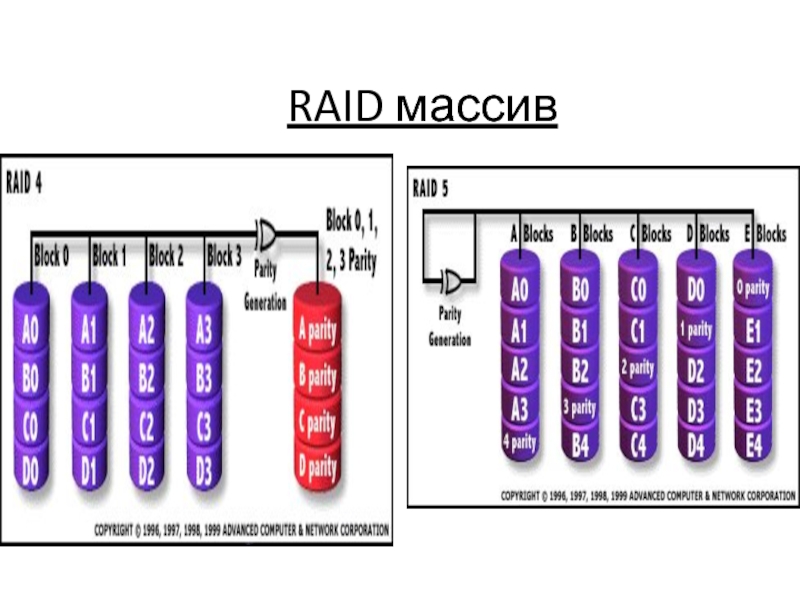

- 64. RAID-2Запись осуществляется параллельно на все диски сразу.

- 65. RAID массив

- 66. RAID массив

- 67. RAID массив

- 68. RAID массив10

- 69. Слайд 69

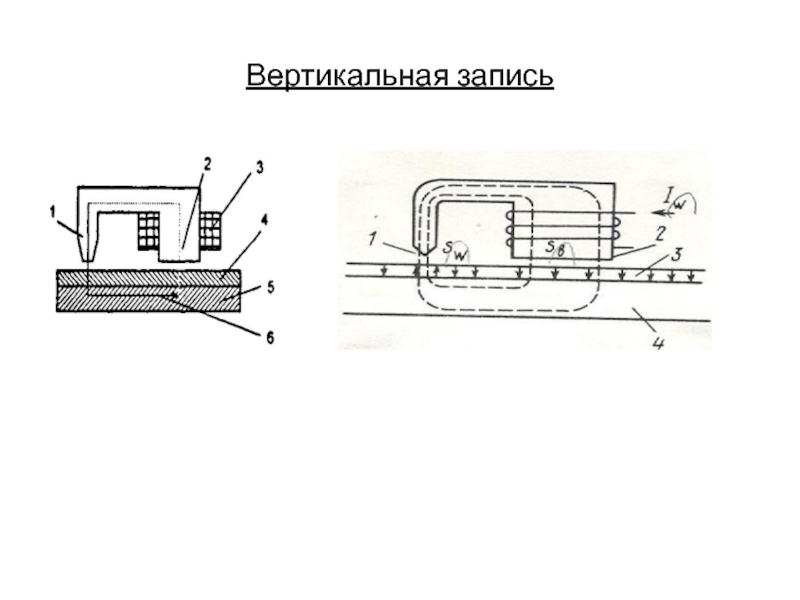

- 70. Вертикальная запись

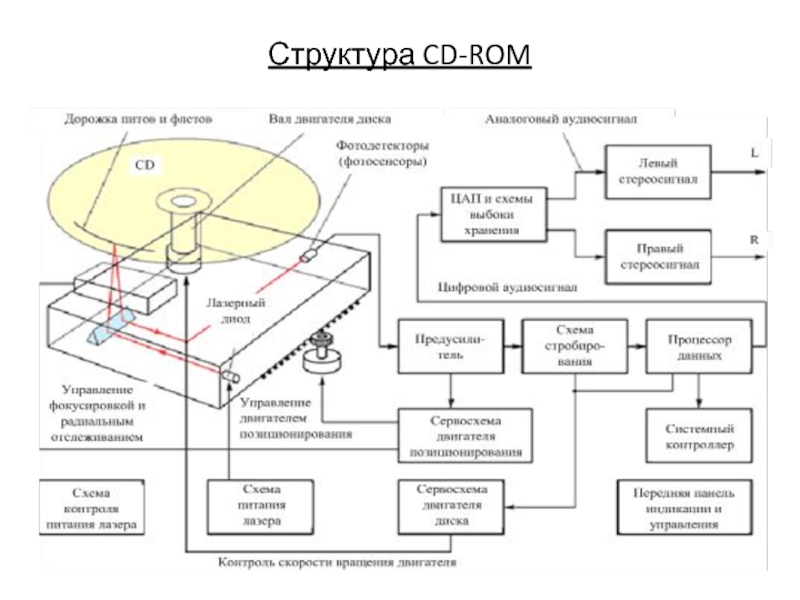

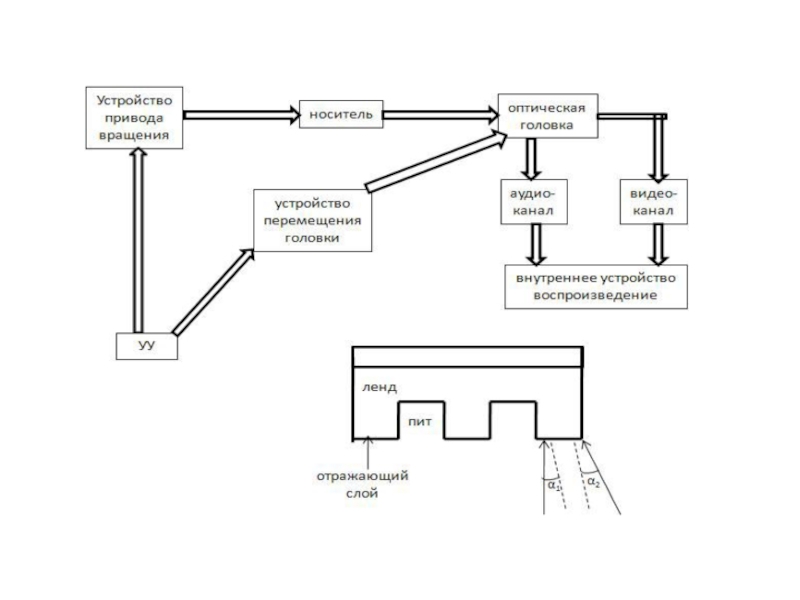

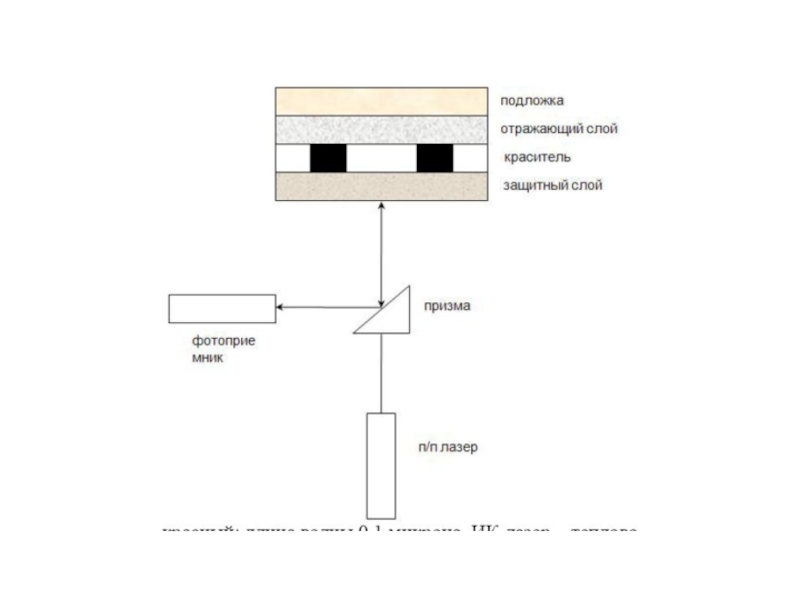

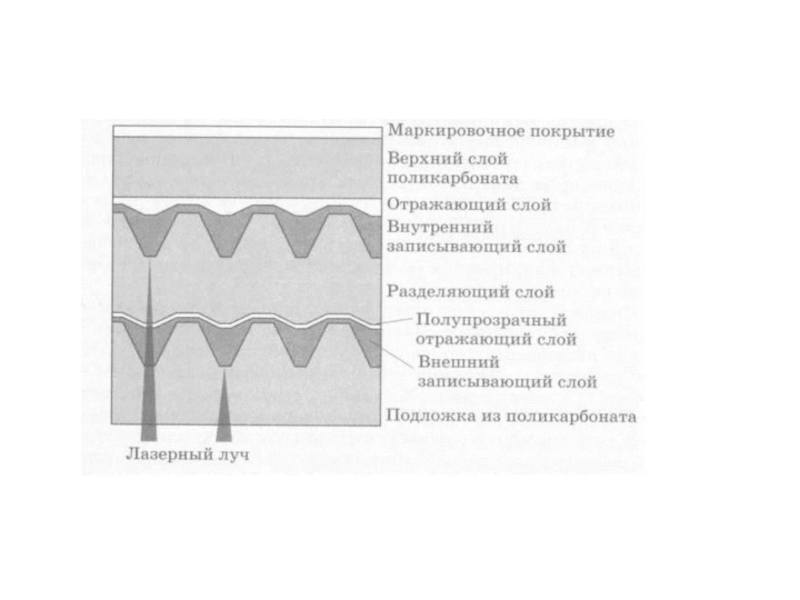

- 71. Структура CD-ROM

- 72. Слайд 72

- 73. Слайд 73

- 74. Слайд 74

- 75. Слайд 75

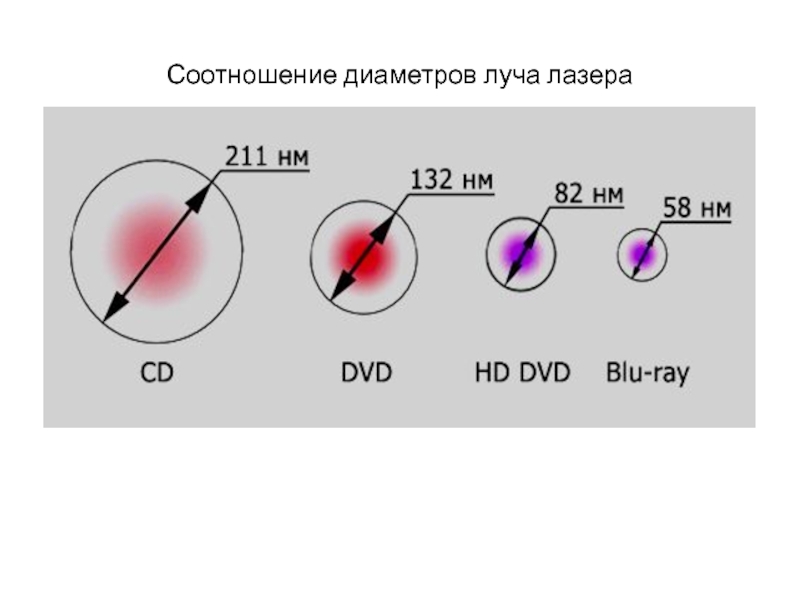

- 76. Соотношение диаметров луча лазера

- 77. Слайд 77

- 78. Магнитооптический диск

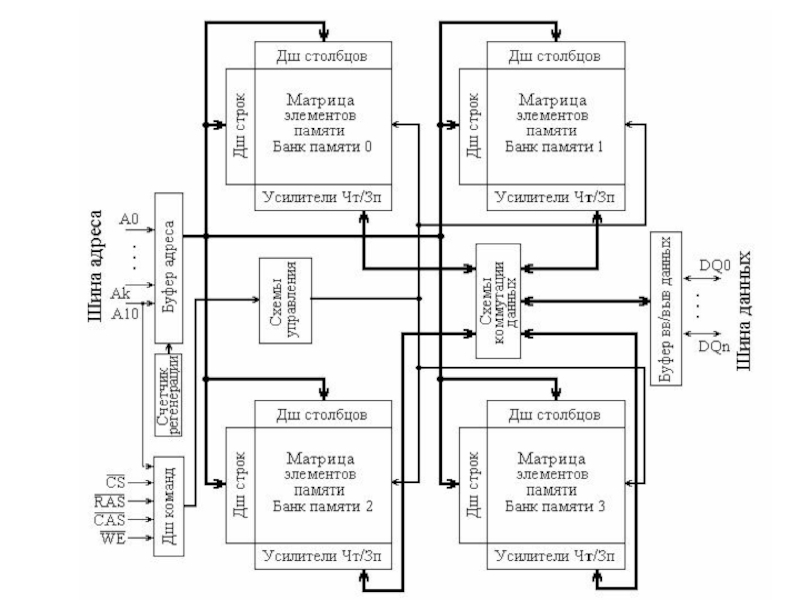

- 79. Главный недостаток NAND SSD — ограниченное количество циклов перезаписи. Обычная

- 80. Ячейка NOR (« Отрицание ИЛИ

- 81. « ИЛИ – НЕ»

- 82. « И – НЕ»

- 83. Слайд 83

- 84. Голографическая память. Запись.

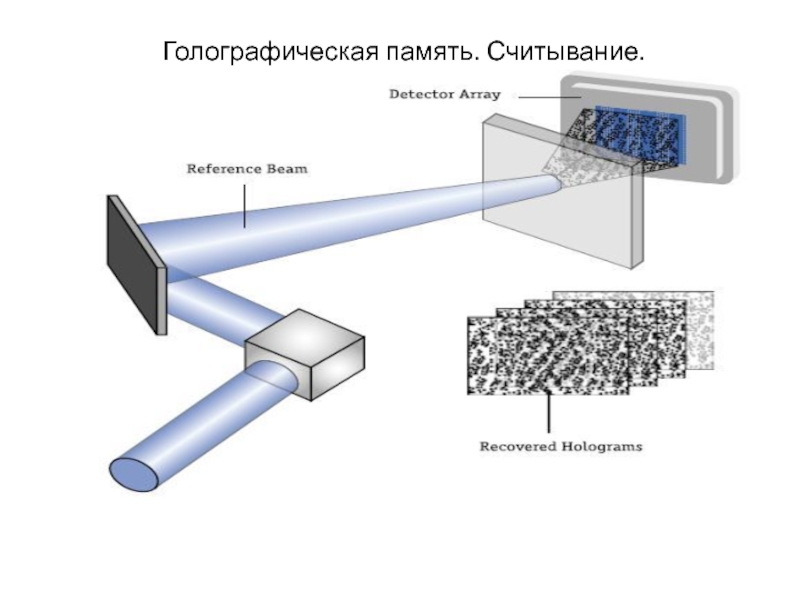

- 85. Голографическая память. Считывание.

- 86. Слайд 86

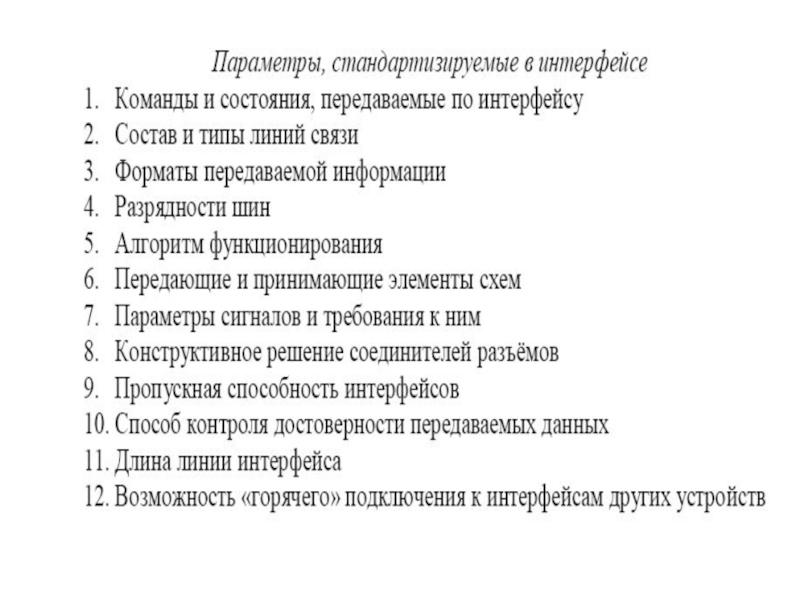

- 87. Параметры интерфейсов· Пропускная способность· Максимальная частота передачи

- 88. Классификация интерфейсов1. По типу связи:· дуплексный (в

- 89. Признаки интерфейсаСпособ соединения компонентов системы:магистральный;радиальный;цепочечный;смешанный.Способ передачи информации:параллельный;последовательный;параллельно-последовательный.Принцип обмена:синхронный;асинхронный.Режим передачи информации:односторонняя передача;двусторонняя поочередная передача;двусторонняя одновременная передача.

- 90. Слайд 90

- 91. Слайд 91

- 92. Слайд 92

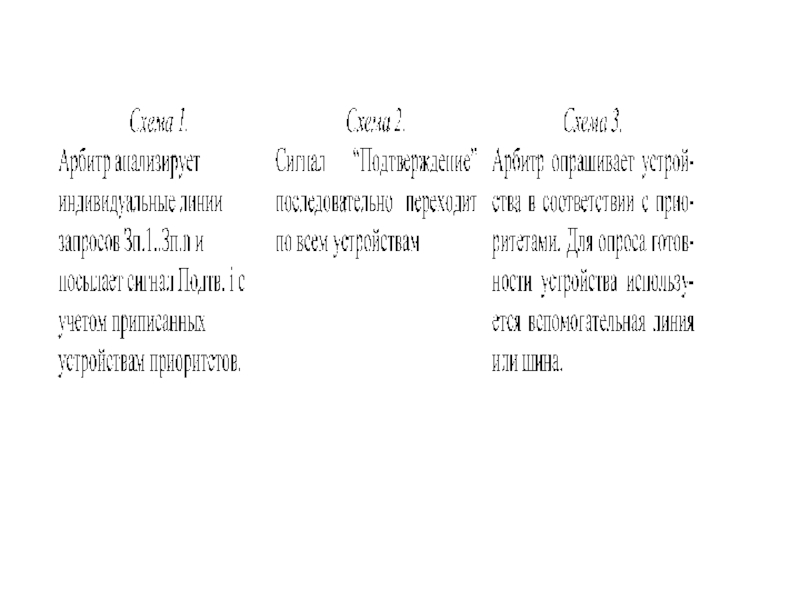

- 93. Централизованный арбитраж

- 94. Слайд 94

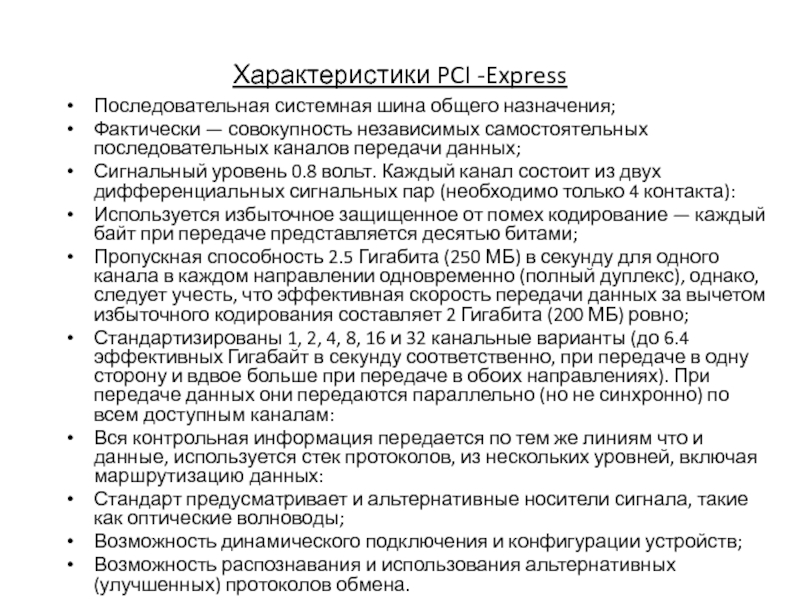

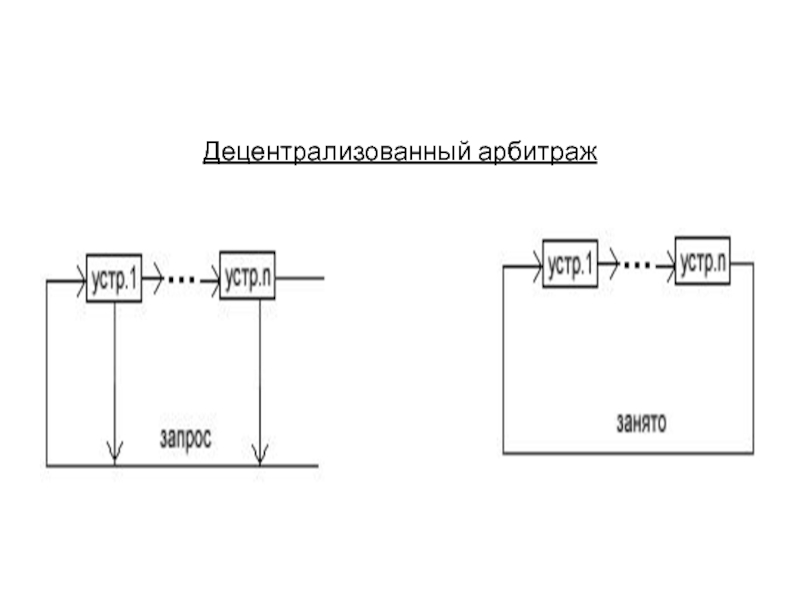

- 95. Децентрализованный арбитраж

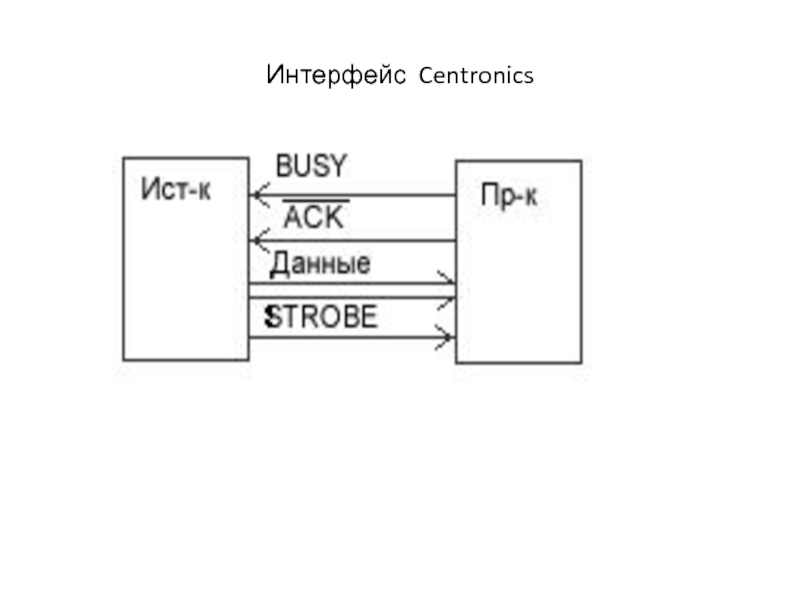

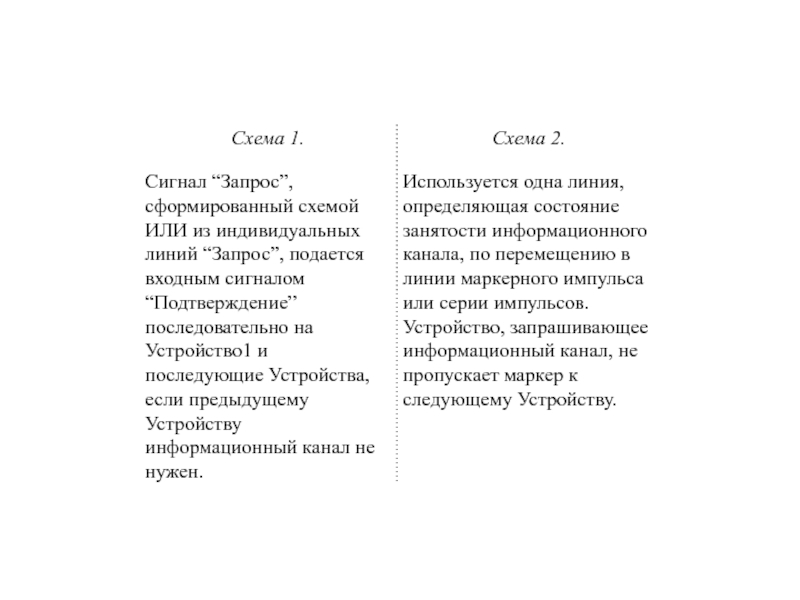

- 96. Слайд 96

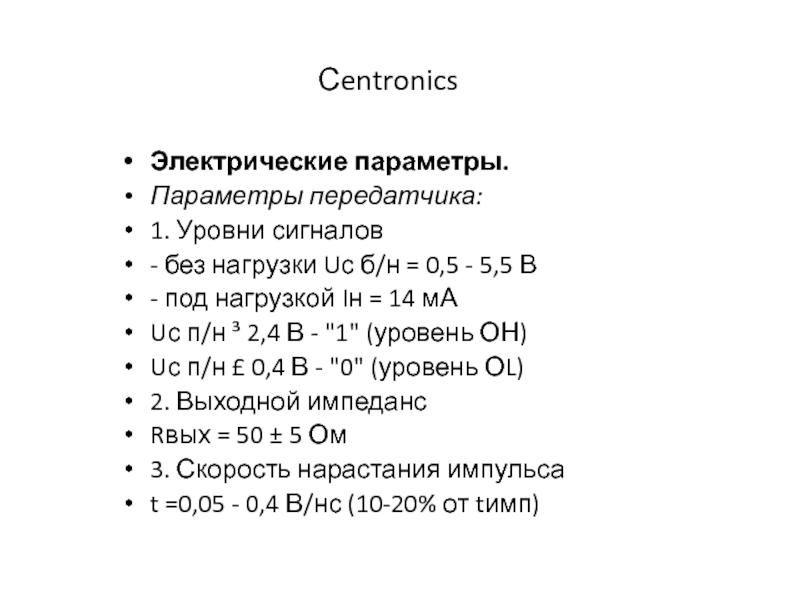

- 97. Слайд 97

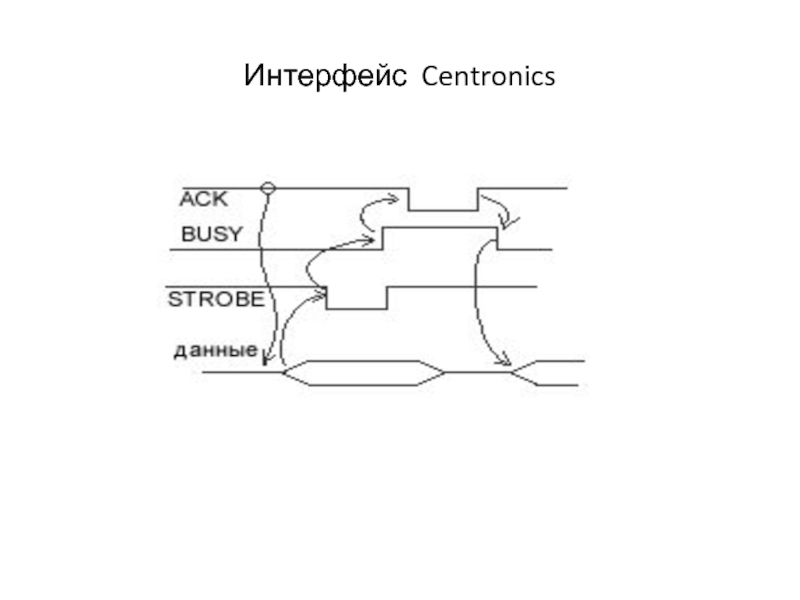

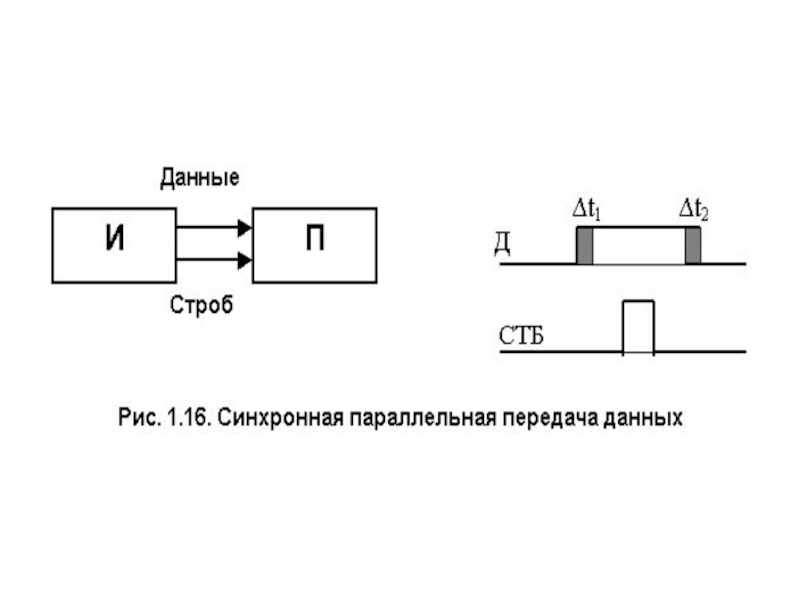

- 98. Слайд 98

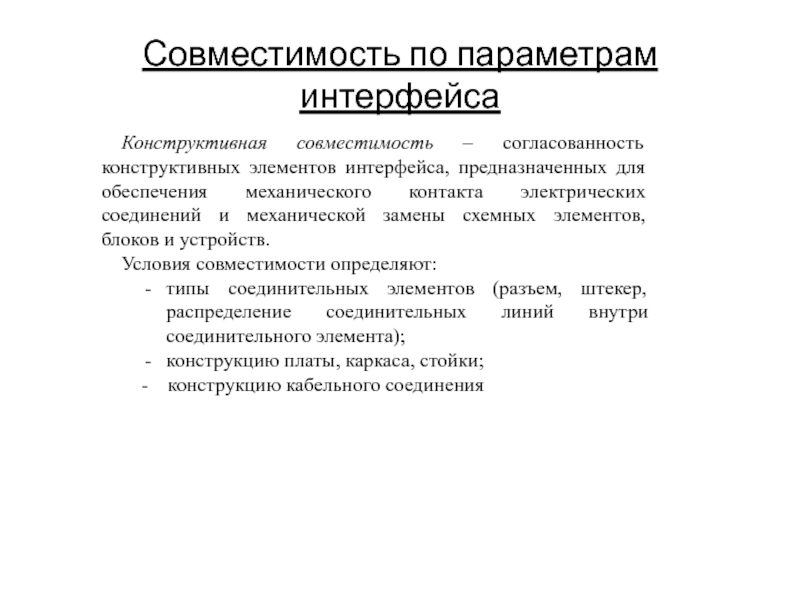

- 99. Совместимость по параметрам интерфейсаКонструктивная совместимость – согласованность

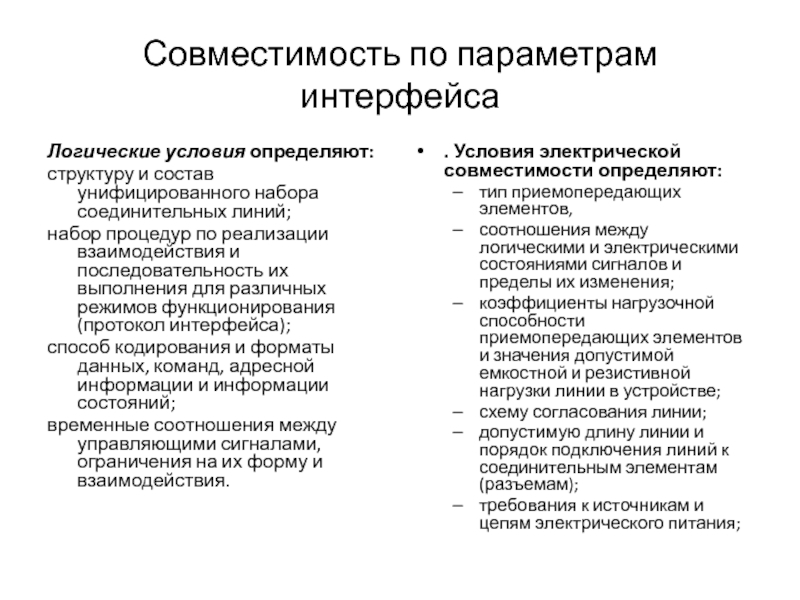

- 100. Совместимость по параметрам интерфейсаЛогические условия определяют:структуру и

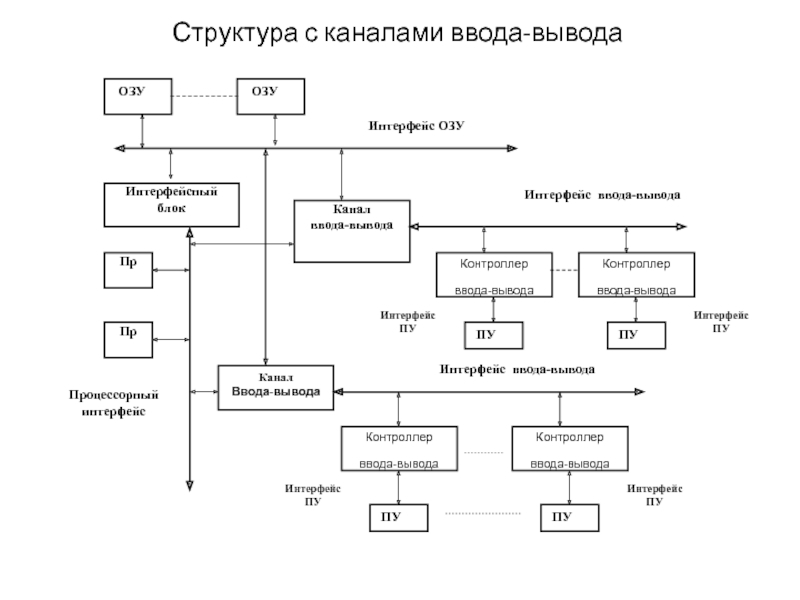

- 101. Структура с каналами ввода-вывода

- 102. Магистральная структура

- 103. Слайд 103

- 104. Слайд 104

- 105. Слайд 105

- 106. Слайд 106

- 107. Слайд 107

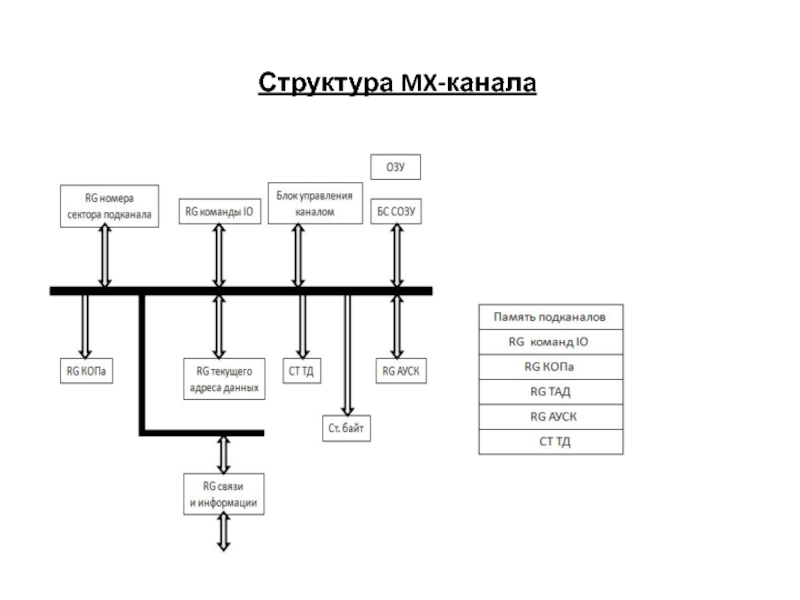

- 108. Структура MX-канала

- 109. Селекторные каналы

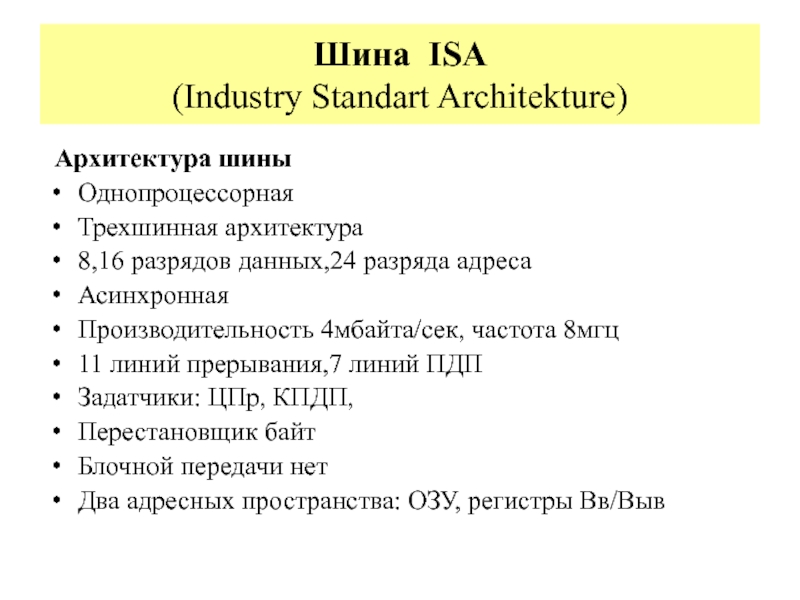

- 110. Шина ISA (Industry Standart Architekture) Архитектура шиныОднопроцессорнаяТрехшинная

- 111. Сигналы адреса и данных

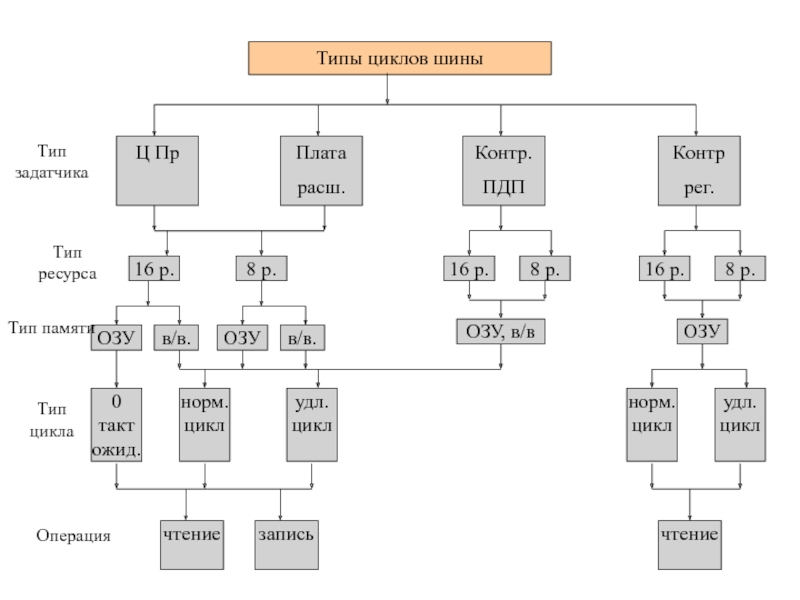

- 112. Типы циклов шины Ц ПрПлатарасш.Контр.ПДПКонтррег.16 р.8 р.16

- 113. Сигналы управления # Master

- 114. Шина PCI (Peripheral Component Interconnect) Базовая версия

- 115. Позже появляются следующие ключевые модификации шины:PCI 2.2

- 116. Основные возможности шины PCI 1.Синхронный 32-х или

- 117. 4.Полная поддержка multiply bus master (например, несколько

- 118. 8.PCI-устройства оборудованы таймером, который используется для определения

- 119. Слайд 119

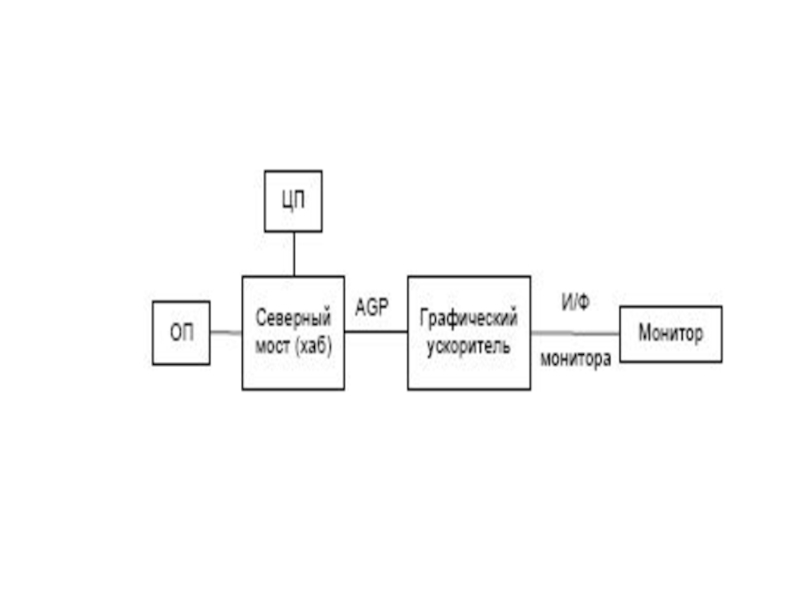

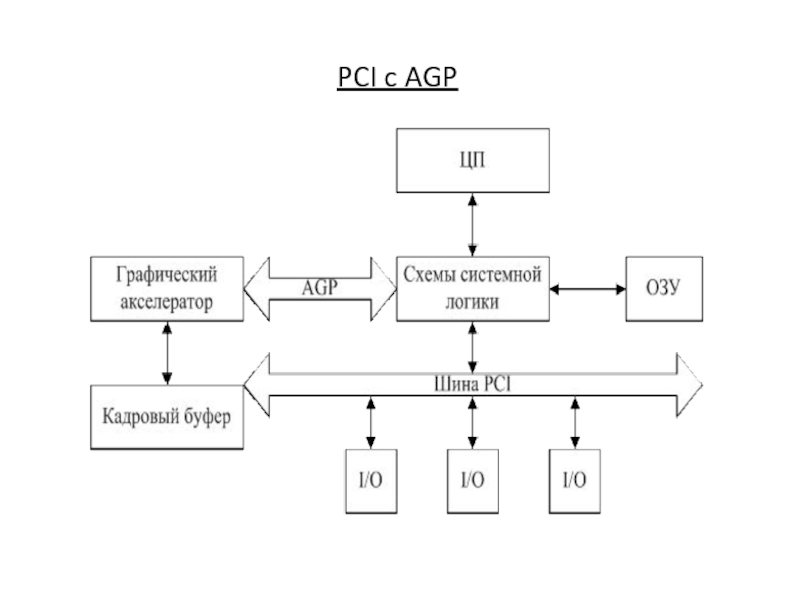

- 120. PCI c AGP

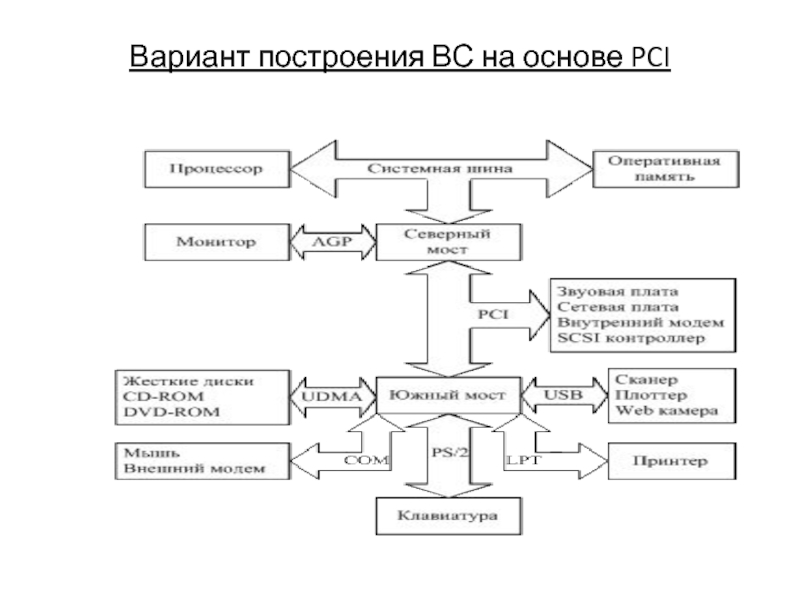

- 121. Вариант построения ВС на основе PCI

- 122. Базовые сигналы шины PCIAD[31-0] – адрес –

- 123. Слайд 123

- 124. Слайд 124

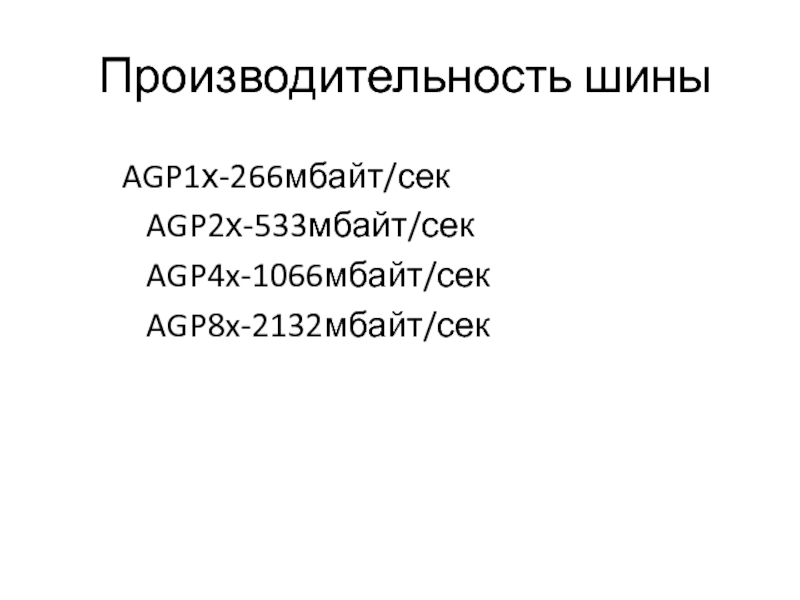

- 125. Производительность шины AGP1х-266мбайт/сек AGP2х-533мбайт/сек AGP4x-1066мбайт/сек AGP8x-2132мбайт/сек

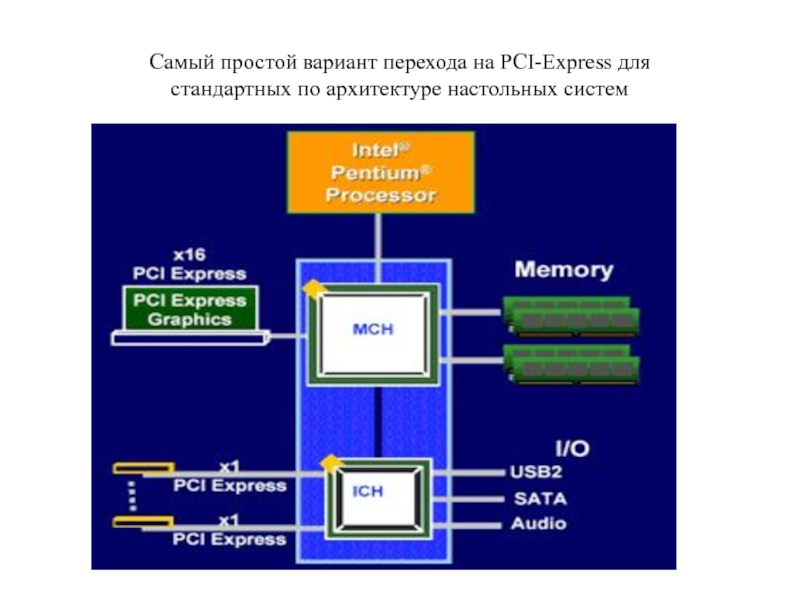

- 126. Самый простой вариант перехода на PCI-Express для стандартных по архитектуре настольных систем

- 127. Характеристики PCI -Express Последовательная системная шина общего

- 128. Интерфейс Centronics

- 129. СentronicsЭлектрические параметры.Параметры передатчика:1. Уровни сигналов- без нагрузки

- 130. Интерфейс Centronics

- 131. Слайд 131

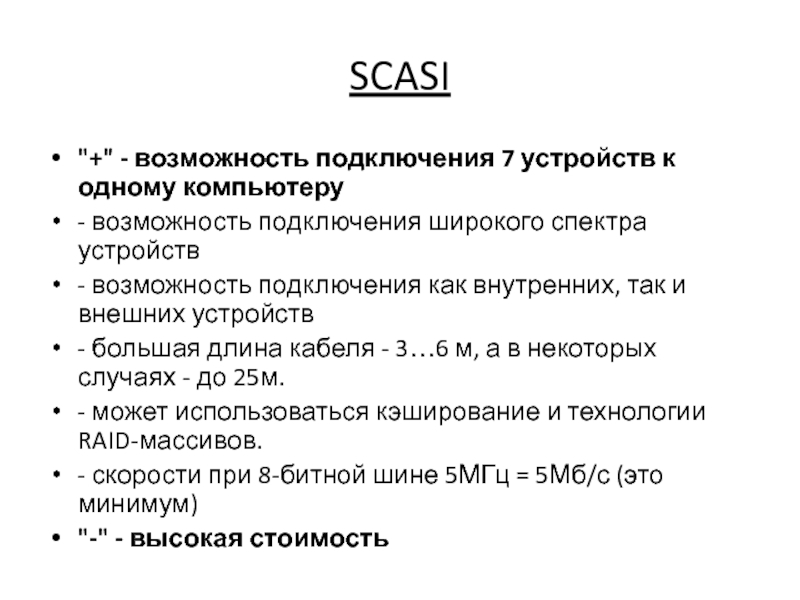

- 132. SCASI"+" - возможность подключения 7 устройств к

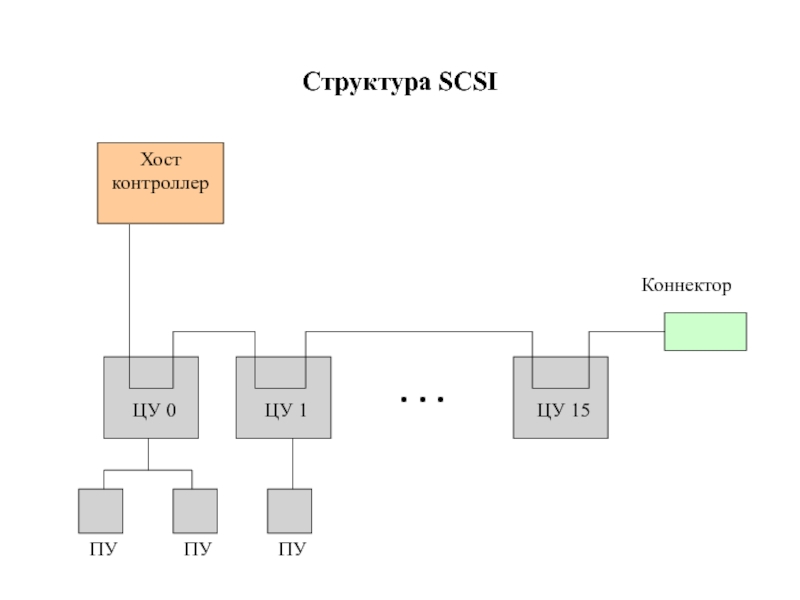

- 133. Структура SCSIХост контроллерЦУ 0ЦУ 1ЦУ 15ПУПУПУКоннектор…

- 134. Слайд 134

- 135. Слайд 135

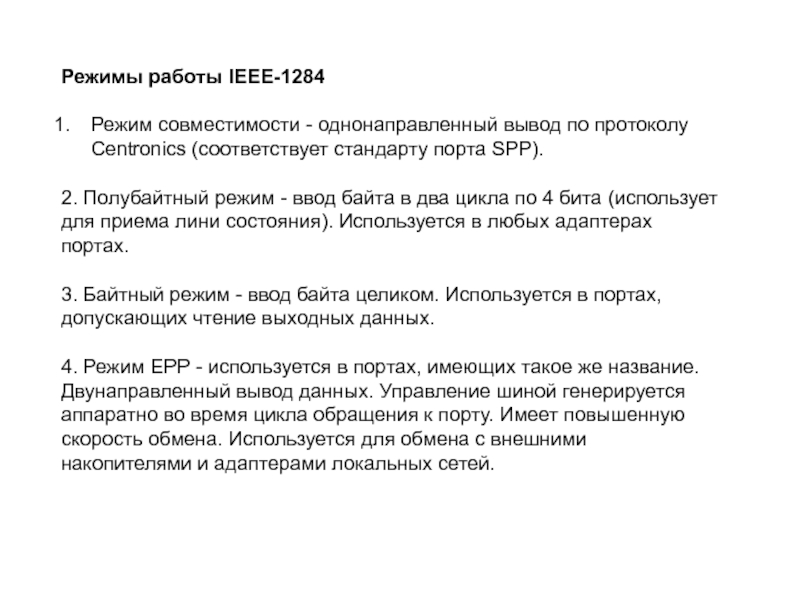

- 136. Режимы работы IEEE-1284Режим совместимости - однонаправленный вывод

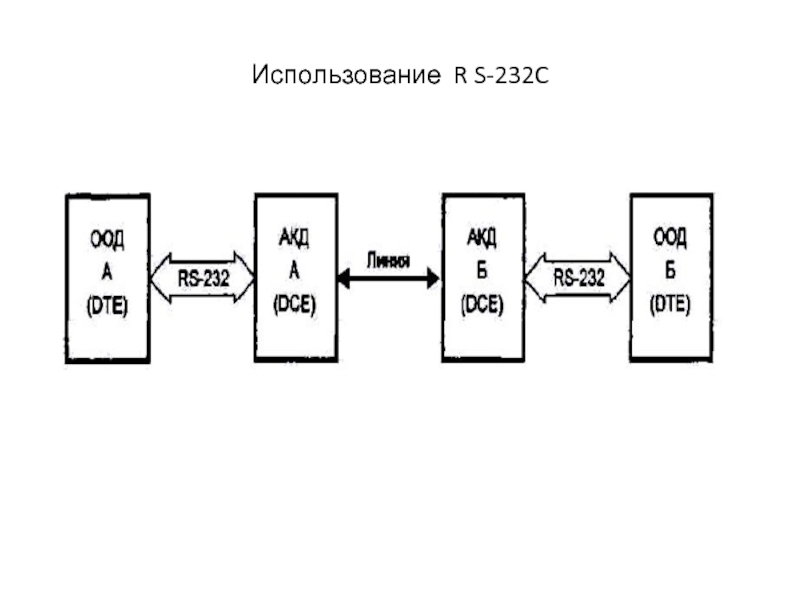

- 137. Использование R S-232C

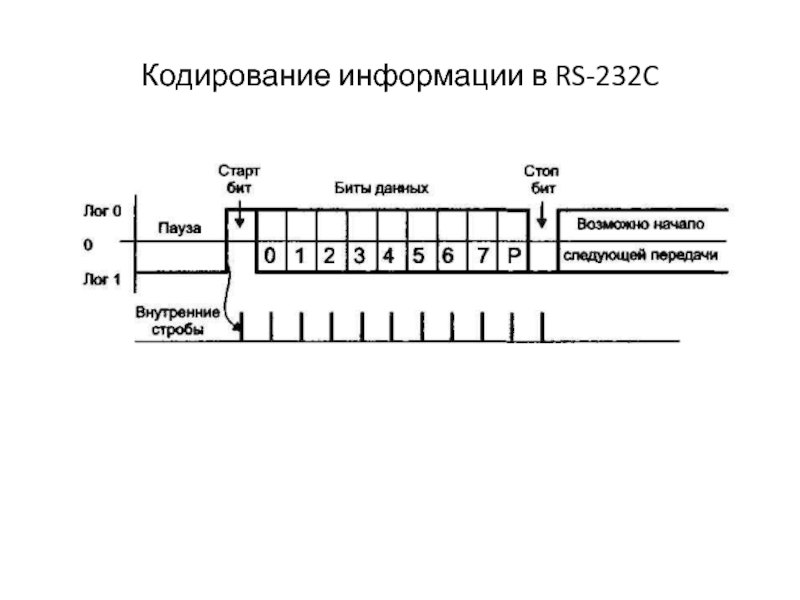

- 138. Кодирование информации в RS-232C

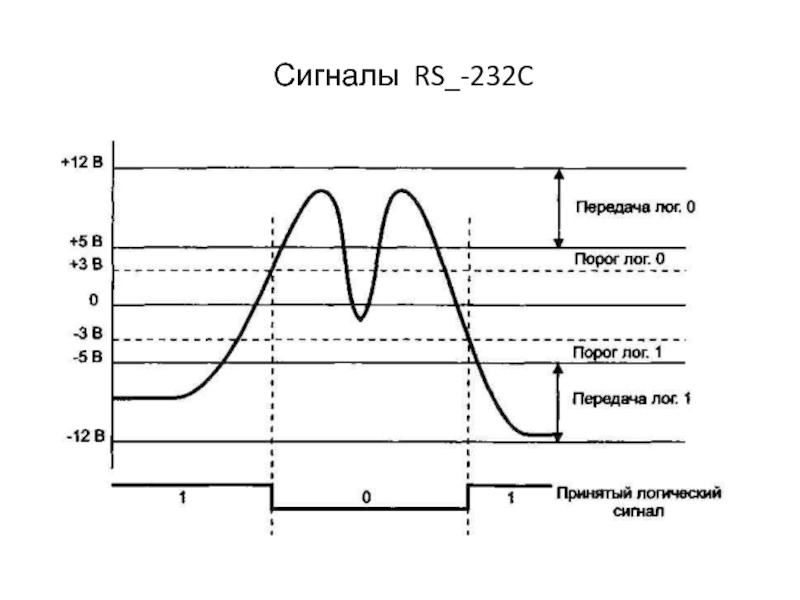

- 139. Сигналы RS_-232C

- 140. Слайд 140

- 141. Слайд 141

- 142. Слайд 142

- 143. Слайд 143

- 144. Слайд 144

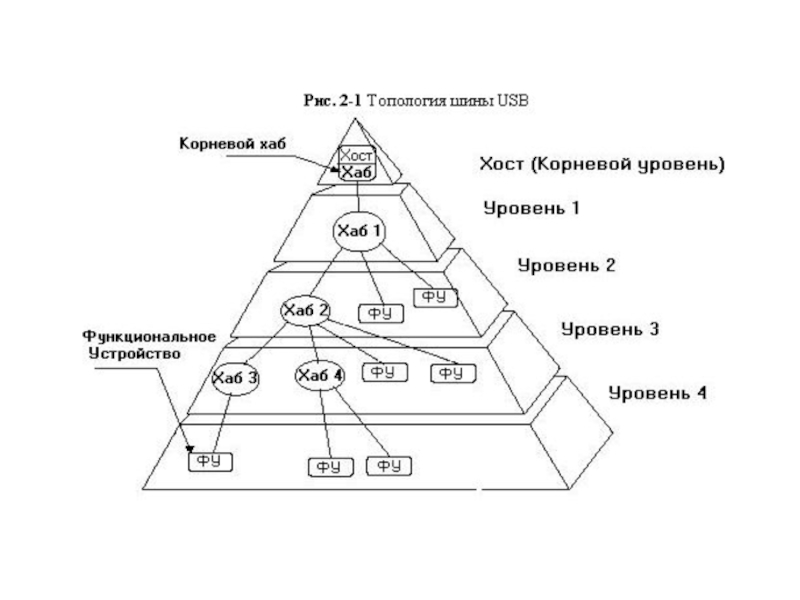

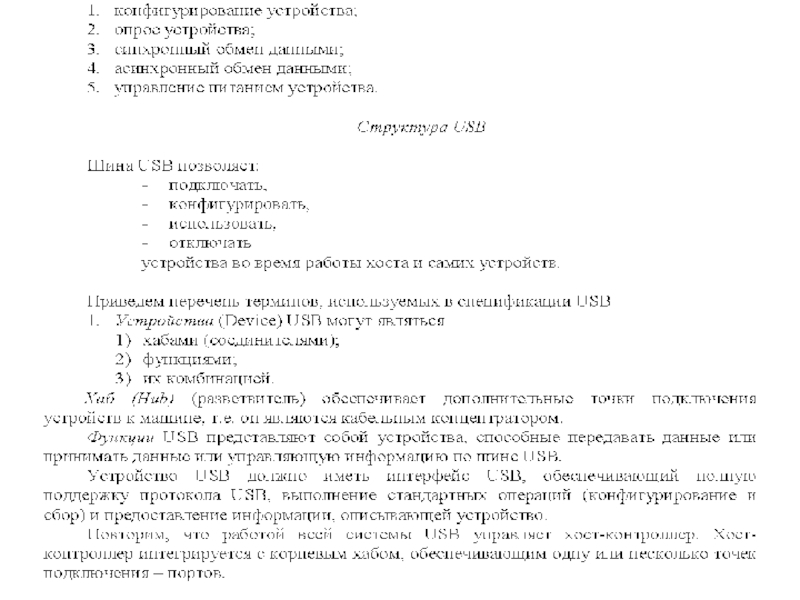

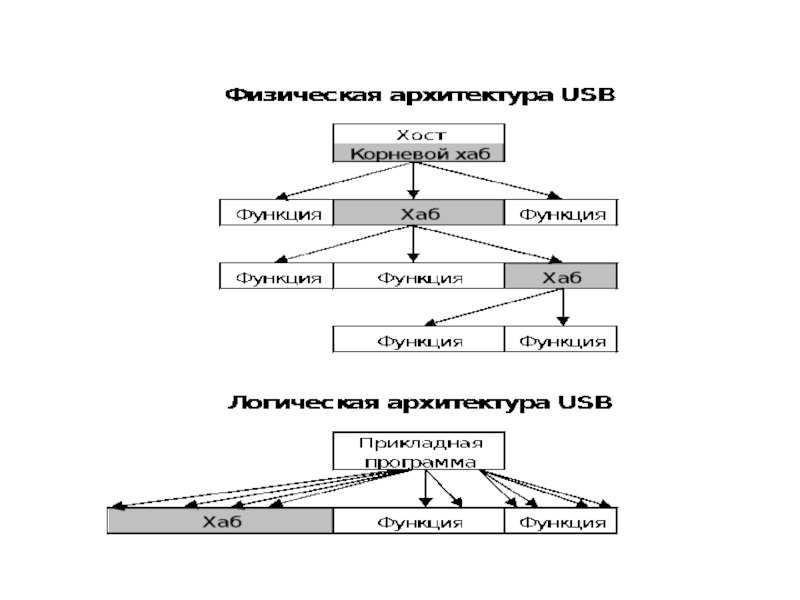

- 145. Интерфейс USB

- 146. Физический интерфейс USB

- 147. Слайд 147

- 148. Слайд 148

- 149. Слайд 149

- 150. Окончательная спецификация USB 3.0 появилась в 2008 году.

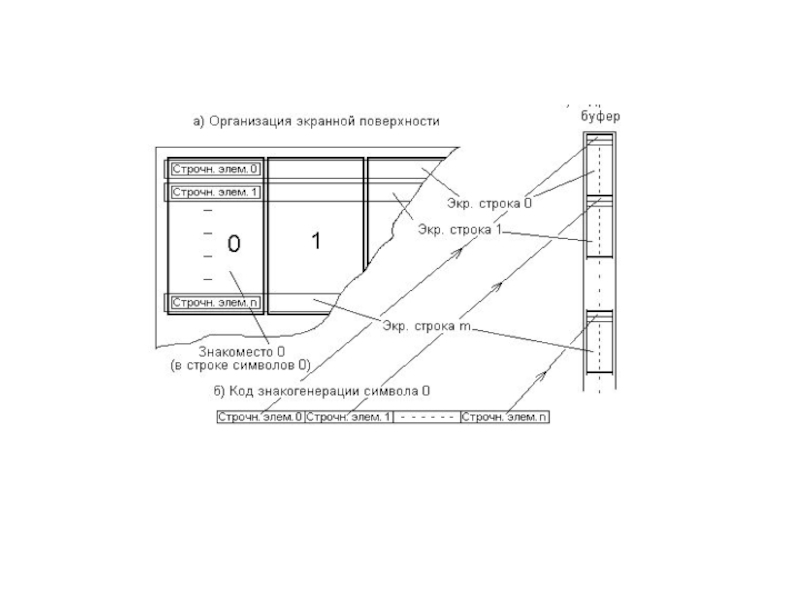

- 151. Формирование изображения на ЭЛТ

- 152. Слайд 152

- 153. Слайд 153

- 154. Слайд 154

- 155. Слайд 155

- 156. Слайд 156

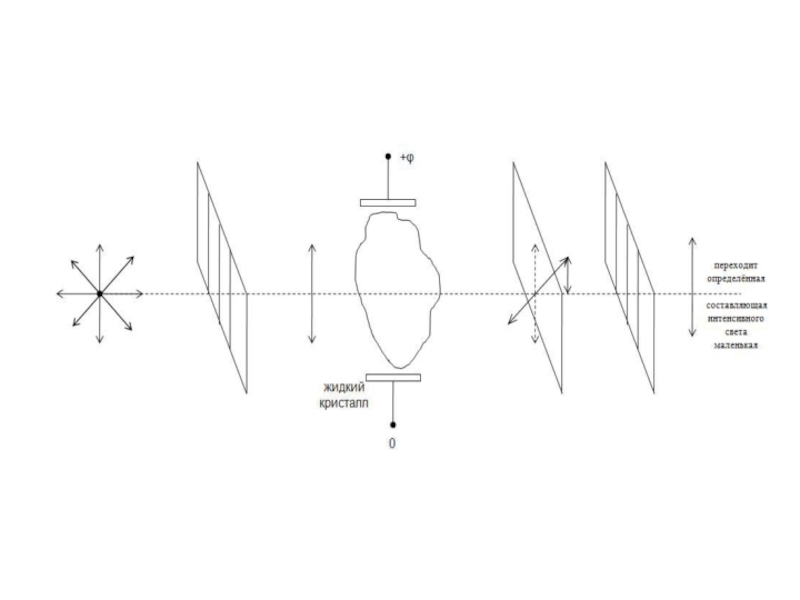

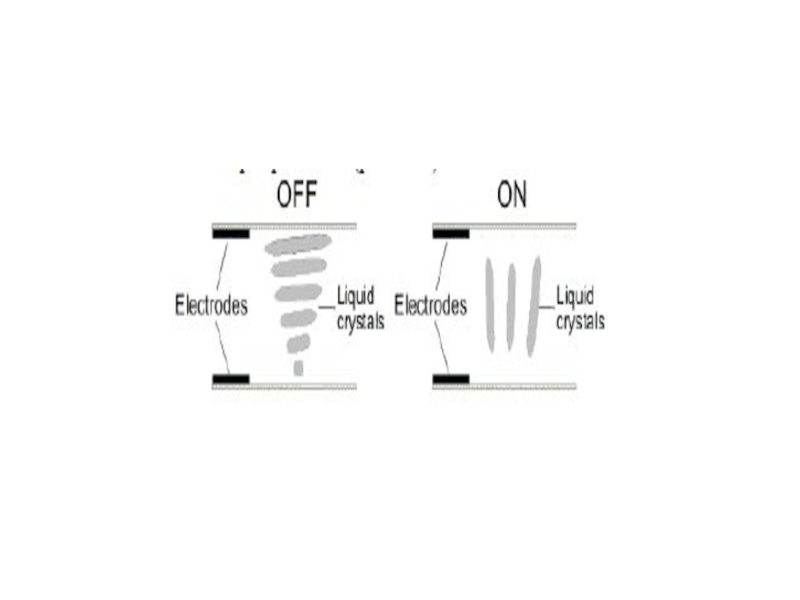

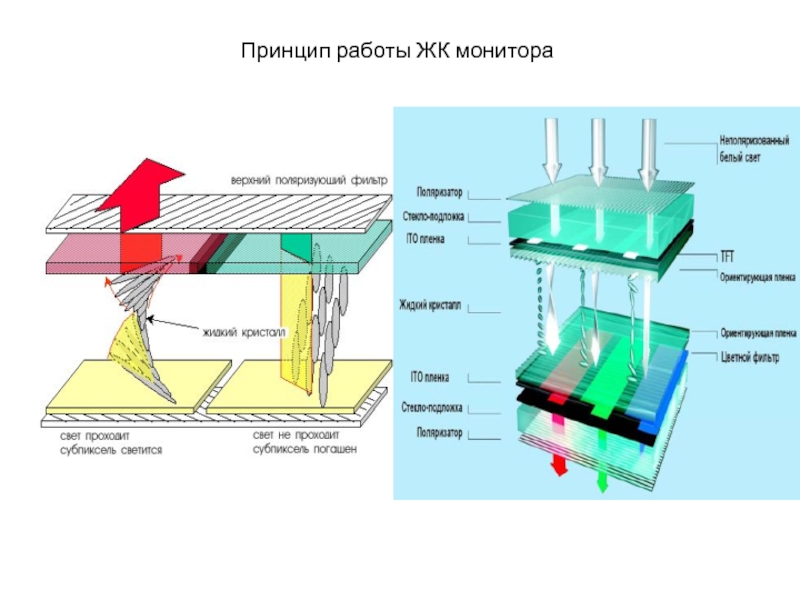

- 157. Принцип работы ЖК монитора

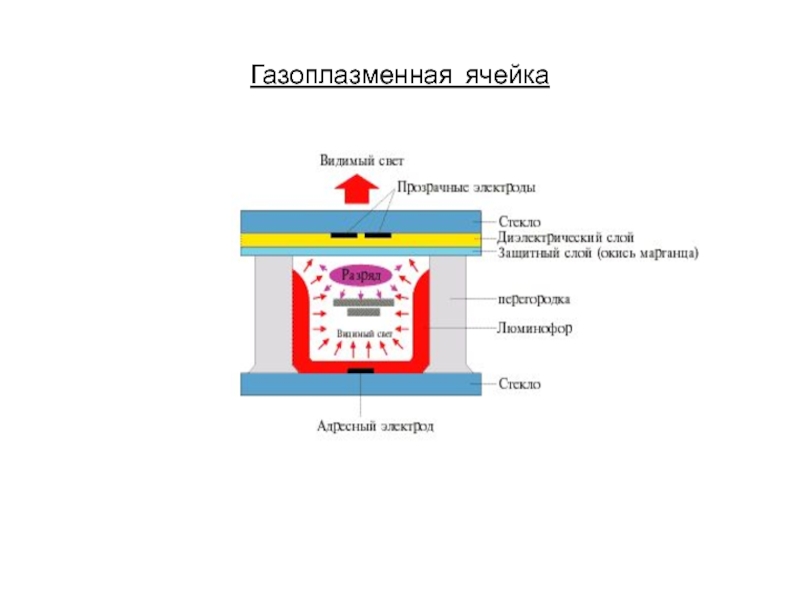

- 158. Газоплазменная ячейка

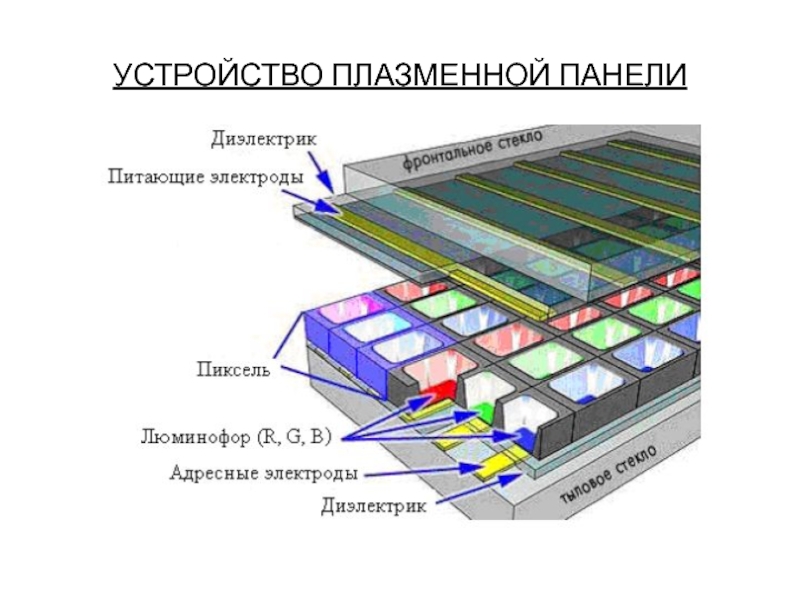

- 159. УСТРОЙСТВО ПЛАЗМЕННОЙ ПАНЕЛИ

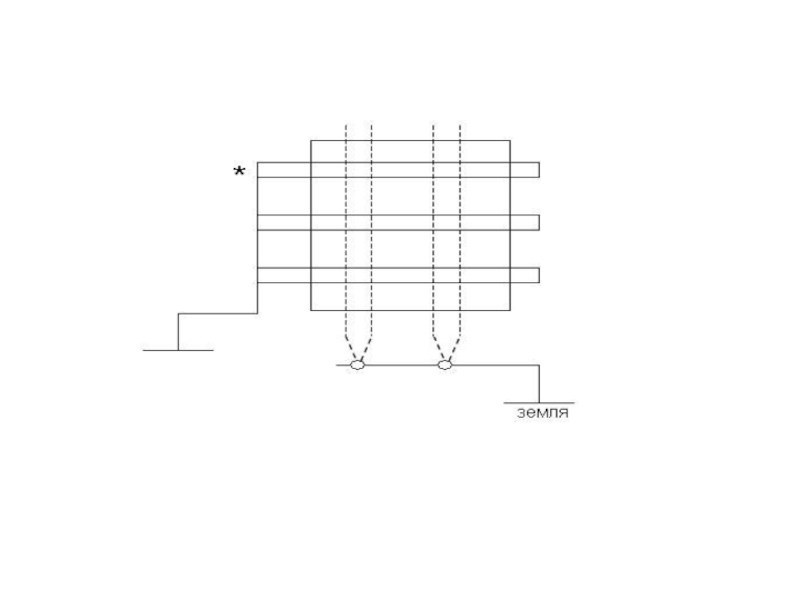

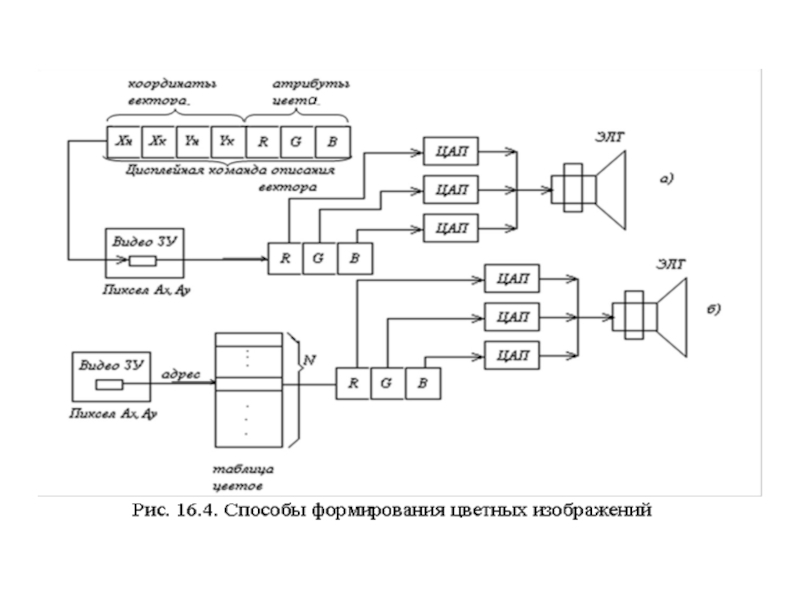

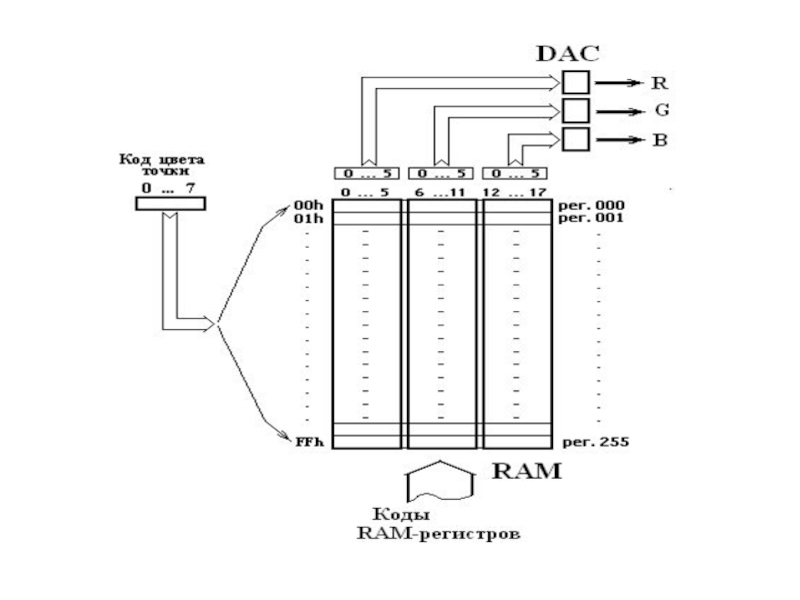

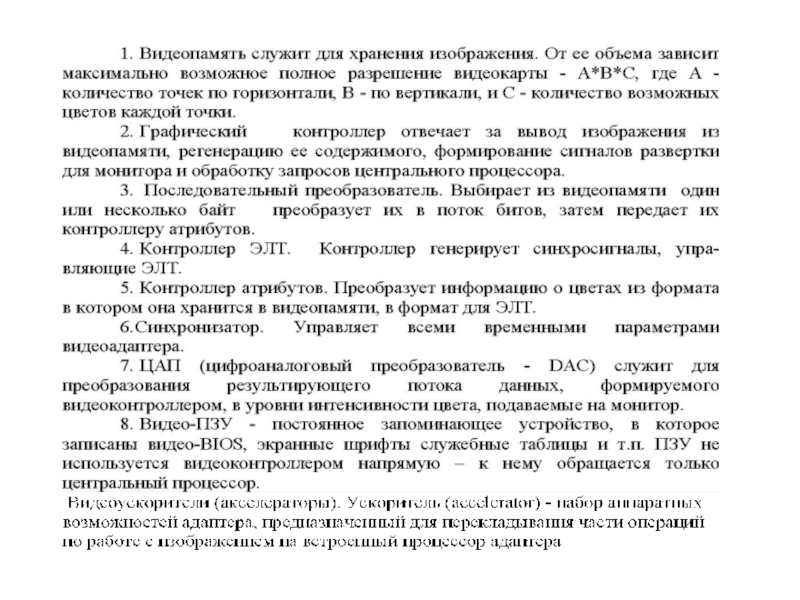

- 160. Структура видеоадаптера

- 161. Слайд 161

- 162. Слайд 162

- 163. Структура видеоадаптера

- 164. Слайд 164

- 165. Структура звуковой карты

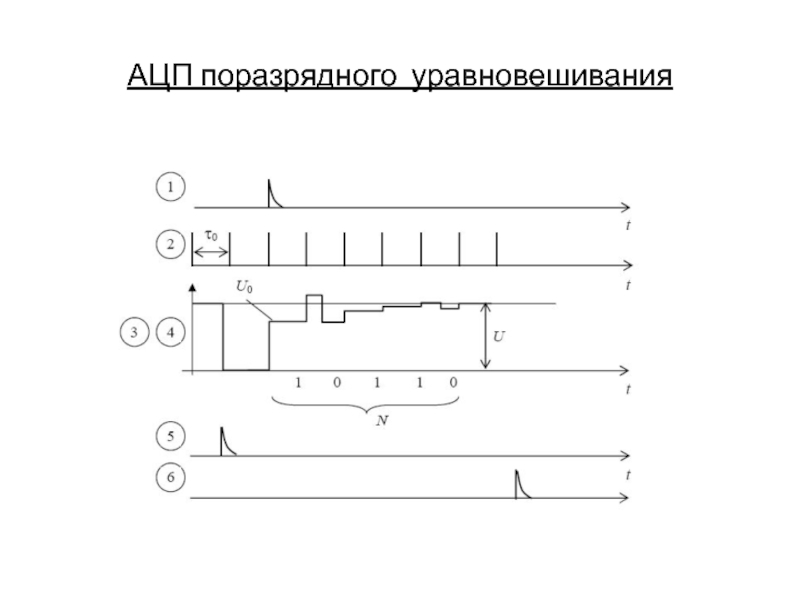

- 166. АЦП поразрядного уравновешивания

- 167. АЦП поразрядного уравновешивания

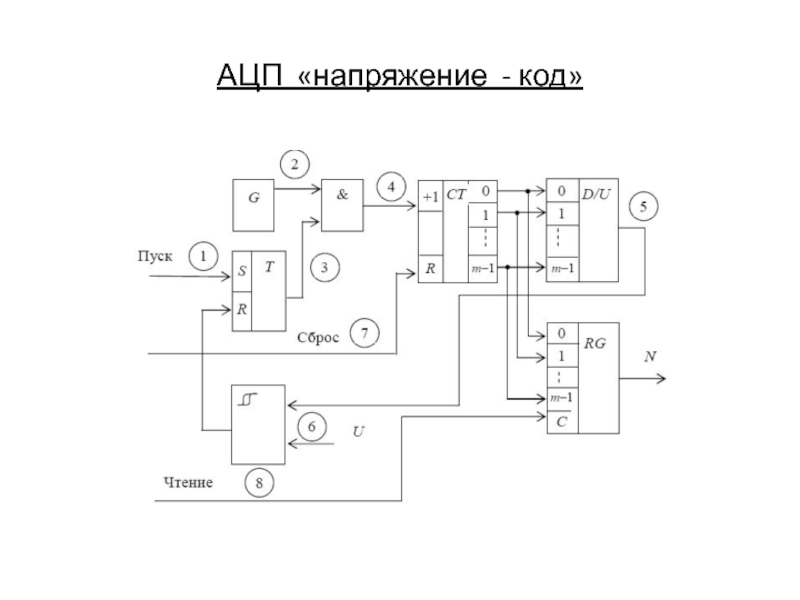

- 168. АЦП «напряжение - код»

- 169. АЦП «напряжение - код»

- 170. Слайд 170

- 171. Скачать презентанцию

Слайды и текст этой презентации

Слайд 2СТРУКТУРА КУРСА

Лекции + практические

2. Лабораторные работы

3. Зачет

4. Курсовая работа

5.

Экзамен

Слайд 3Литература

1. Горнец Н.Н. Периферийные устройства современных вычислительных систем. Дрофа, М.,

2006 г.

2. Горнец Н.Н., Рощин. ЭВМ и периферийные устройства. Компьютеры

и вычислительные системы., Академия, М., 2012 г.

3. Горнец Н.Н., Рощин. ЭВМ и периферийные устройства.

Устройства ввода-вывода. Академия, М., 2012 г.

4. Гук М. Аппаратные интерфейсы ПК. Энциклопедия. Питер,

2003 г.

5. Гук М. Аппаратные средства IBM PC. Энциклопедия. Питер, 2004 г.

6. Танненбаум Э. Архитектура компьютера. Питер, 2004 г.

7. Ларионов А.М., Горнец Н.Н. Периферийные устройства вычислительных систем. Энергия, М., 1996 г.

Слайд 4Классы задач

1. Научно-технические задачи.

Требования. Высокое быстродействие ВС, больше

количество вычислений

и ограниченная точность вычислений. Используются многопроцессорные

ВС с большим объёмом

ОП и быстродействующими устройствами внешнейпамяти.

2. Информационно-справочные и экономические задачи.

Особенности. Большое количество однотипных вычислений. Использование

многоразрядных слов переменной длины. Большое количество символов.

Высокоточные вычисления.

Требования к периферийным устройствам. Широкий спектр устройств

отображений информации, высокая точность вычислений, большой объём

внешней памяти.

3. Задача управления объектами.

Особенности. Работа в режиме реального масштаба времени. Под режимом реального

масштаба времени следует понимать такой режим , при котором реакция ВС

на вводимый блок данных будет завершена до поступления следующего

блока информации.

Требования к периферийным устройствам для управляющих

вычислительных систем. Большое количество цифро-аналоговых, А ЦП преобразователей, наличие ввода/вывода дискретных сигналов.

Слайд 11Способы повышения производительности ВС

увеличением быстродействия всех его устройств, в то

числе и ПУ, но быстродействие ПУ ограничено электромеханическими принципами действия

большинства ПУ, а также возможностями пользователя;совмещением операций обработки и ввода-вывода, для чего в компьютере необходимо предусмотреть автономные устройства управления вводом-выводом;

совмещением нескольких операций ввода-вывода при наличии в компьютере нескольких устройств ввода-вывода;

Слайд 12Задачи и структура систем ввода-вывода 1. Преобразование форматов данных при вводе

данных из внешней памяти центральной части ВС и обратное преобразование при

выводе информации; 2. Формирование места в ОП, куда должен быть помещён квант данных при вводе информации или откуда он должен быть извлечён при выводе информации. Система IO должна включать генераторы адреса. 3. Формирование сигналов для работы ПУ в различных режимах (функция управления ПУ) (Ci); 4. Получение и преобразование от ПУ управляющих сигналов (Si) и оценка состояния ПУ; 5. Функции согласования быстродействия центральной части ВС и ПУ; Реализация этих функций возможна при использовании центрально-синхронного принципа управления и асинхронного принципа управления.Слайд 16Параллелизм работы ВС обеспечивается

Во время подготовки квантов информации управление ПУ

должно выполняться автономными схемами самого ПУ независимо от ЦП;

Передача в

оперативную память компьютера подготовленных в ПУ квантов информации должна осуществляться, минуя АЛУ, для чего необходимы специальные средства управления ПУ, а, возможно, и дополнительные входные регистры ОП;Для синхронизации асинхронных процессов обработки информации в ЦП и подготовки квантов информации в ПУ должны быть предусмотрены особые аппаратные средства.

Слайд 54RLL-метод

В этом методе полностью исключаются биты синхронизации, за счет чего

информационная емкость диска возрастает. При кодировании RLL-методом каждый байт, поступающих

данных, разделяется на два полубайта, а затем полубайты кодируются специальным 5- разрядным кодом. Из 32 комбинаций 5- разрядного кода для кодирования методом RLL используются 16, в которых число рядом стоящих нулей не превышает двух.Полученная последовательность нулей и единиц кодируется методом без возврата к нулю.

Слайд 56Физическая организация

1. Поверхности – области на диске, в которых формируются

траектории движения

2. Дорожки – представляют собой траекторию движения магнитной головки,

являются концентрическими окрестностями относительно центра диска;Дорожки номеруются от края диска к центру и делятся на сектора;

3. Дорожки делятся на сектора;

4. Сектора объединяются в кластеры – минимальная адресуемая часть

информации поверхности;

5. Цилиндры – если имеется пакет дисков, то при формировании (разметке) диска нанесение дорожек осуществляется и на все информационные поверхности.

Дорожки, имеющие одинаковый номер, на всей поверхности образуют цилиндр.

При обращении к диску адресуется цилиндр.

Слайд 59Расчет характеристик

плотность поперечной записи информации на диске - Рпоп. [дор/мм]

плотность

продольной записи информации на диске – Рпр. [бит/мм]

емкость накопителя –

Сн.= Сдор.*nдор.*Nпов.Сдор.= Рпр.Lдор.; Lдор.=2Пr (r – внутренняя дорожка);

nдор.= Рпоп.*H

H=R-r

- максимальная скорость передачи информации - V=Pпр*v , где v-линейная скорость

среднее время доступа – Тдоступа = Тпоиска + Тоб/2

Тпоиска = ½(Tmin+Tmax) .

Tmin – время поиска на соседнюю дорожку

Tmax – время поиска на удаленную дорожку

Слайд 61Логическая организация

1. загрузочный сектор, включающий программу начала загрузки;

2. таблица размещения

файлов – 2 копии;

3. корневой каталог;

4. файлы ОС;

5. остальное –

область данных.Слайд 63.

RAID-0

Представляет собой виртуальный диск, разбитый на зоны, информация записывается на

диске, разбивая на сектора, каждый сектор информации записывается в определённую

зону. Зоны записываются последовательно по кругу. При считывании информации контроллер разбивает команду на несколько подкоманд, число которых равно числу дисков. При этом осуществляется параллельное обращение ко всем дискам сразу.Преимущество: высокая производительность при запросах информации большой ёмкости.

Недостатки: низкая надёжность;невысокая производительность при работе в режиме один запрос – один сектор.

RAID-1 – зеркальные диски

Запись информации аналогичен RAID0 уровню, но все диски дублируются; число основных дисков равно числу дублирующих. При считывании возможен доступ к любой зоне основного или дублирующего пакета.

Преимущество: высокое быстродействие и надёжность хранения данных.

Недостатки: значительный объём аппаратных средств.

Слайд 64RAID-2

Запись осуществляется параллельно на все диски сразу. Записываемая информация разбивается

на байты или слоги и каждый байт или слог записывается

на соответствующем диске, т.е. число дисков должно быть равно числу байт или слов. Используется контроль по чётности и корректирующие коды Хемминга.Преимущества: мощный контроль правильности записи информации, высокая производительность.

Недостатки: сложность контроллера, необходимость синхронизации вращения дисков, требуется большое количество дисков.

RAID-3

Упрощённый RAID2, используется только контроль по чётности.

RAID-4

Принцип организации аналогичен RAID0 уровню; для контроля имеется отдельный диск чётности.

RAID-5

Аналогичен RAID0, но контрольные разряды чётности распределены по всем дискам по кругу.

Слайд 79Главный недостаток NAND SSD — ограниченное количество циклов перезаписи. Обычная (MLC, Multi-level cell, многоуровневые

ячейки памяти) флеш-память позволяет записывать данные примерно 3000–10 000 раз

(гарантированный ресурс); в самых дешёвых накопителях (USB, SD, uSD) может использоваться ещё более плотная память типа TLC (MLC-3) с ресурсом порядка единиц тысяч циклов или менее1.Отсутствие движущихся частей, отсюда:

2. стабильность времени считывания файлов вне зависимости от их расположения или фрагментации;

3. скорость чтения/записи выше, чем у распространённых жёстких дисков, и в ряде операций может быть близка к пропускной способности интерфейсов (SAS/SATA II 300 МБ/с, SAS/SATA III 600 МБ/с). Твердотельные накопители могут реализовываться с более быстрыми интерфейсами: SATA III, PCI Express, NGFF (M.2, в вариантах с PCIe), SATA Express, NVM Express (стандарт на подключение SSD по шинам PCI Express), U.2.

4. количество произвольных операций ввода-вывода в секунду (IOPS) у SSD на порядок выше, чем у жёстких дисков, за счёт возможности одновременного запуска множества операций и более низкой латентности каждой операции (нет необходимости ожидать оборота диска перед доступом);

5. низкое энергопотребление;

6. намного меньшая чувствительность к внешним электромагнитным полям;

7. малые габариты и вес.

Слайд 87Параметры интерфейсов

· Пропускная способность

· Максимальная частота передачи сигнала

· Допустимое расстояние

передачи

· Динамические параметры:

1. передача слова

2. передача блока (с учетом процедур

подготовки и разрешения канала)· Общее число линий интерфейса

· Количество бит передаваемых параллельно

Слайд 88Классификация интерфейсов

1. По типу связи:

· дуплексный (в двух направлениях одновременно)

·

полудуплексный (информация передается раздельно во времени, но в 2 направлениях)

·

симплексный (в одном направлении)2. По среде передачи информации

· Электрическая (провода, кабели)

· Оптическая (оптоволокно, ИК-порт)

· Электромагнитная (волноводы, радиоволны)

3. По типу кабеля

· Коаксиальный кабель

· Витая пара

· Световод, оптоволокно

· Электромагнитная среда

· Волновод

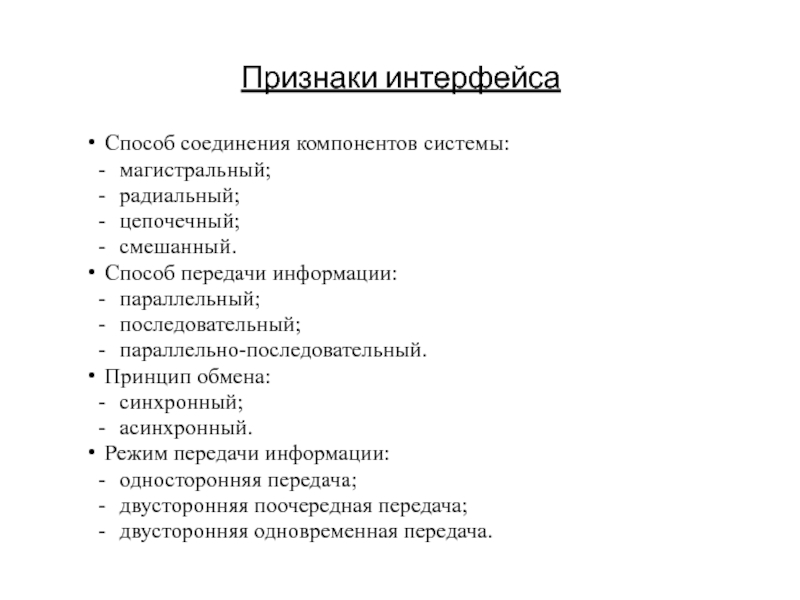

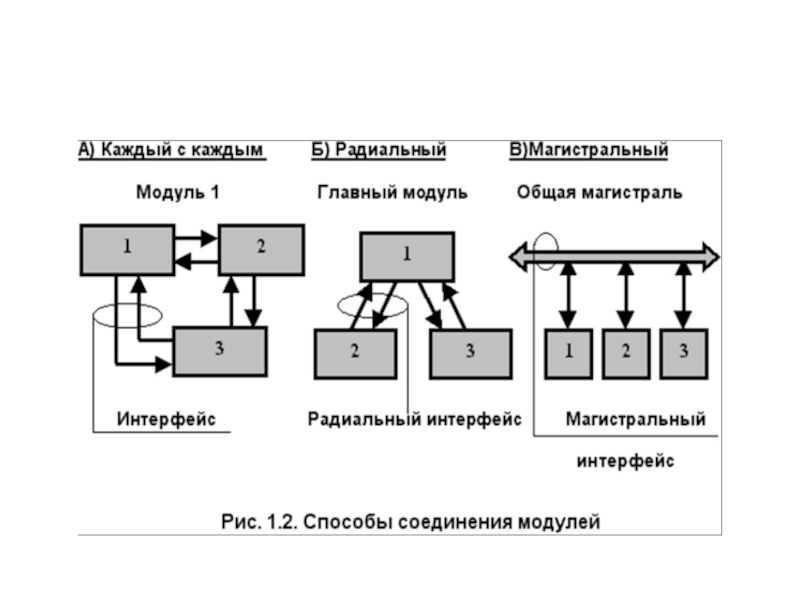

Слайд 89Признаки интерфейса

Способ соединения компонентов системы:

магистральный;

радиальный;

цепочечный;

смешанный.

Способ передачи информации:

параллельный;

последовательный;

параллельно-последовательный.

Принцип обмена:

синхронный;

асинхронный.

Режим передачи информации:

односторонняя

передача;

двусторонняя поочередная передача;

двусторонняя одновременная передача.

Слайд 99Совместимость по параметрам интерфейса

Конструктивная совместимость – согласованность конструктивных элементов интерфейса,

предназначенных для обеспечения механического контакта электрических соединений и механической замены

схемных элементов, блоков и устройств.Условия совместимости определяют:

типы соединительных элементов (разъем, штекер, распределение соединительных линий внутри соединительного элемента);

конструкцию платы, каркаса, стойки;

- конструкцию кабельного соединения

Слайд 100Совместимость по параметрам интерфейса

Логические условия определяют:

структуру и состав унифицированного набора

соединительных линий;

набор процедур по реализации взаимодействия и последовательность их выполнения

для различных режимов функционирования (протокол интерфейса);способ кодирования и форматы данных, команд, адресной информации и информации состояний;

временные соотношения между управляющими сигналами, ограничения на их форму и взаимодействия.

. Условия электрической совместимости определяют:

тип приемопередающих элементов,

соотношения между логическими и электрическими состояниями сигналов и пределы их изменения;

коэффициенты нагрузочной способности приемопередающих элементов и значения допустимой емкостной и резистивной нагрузки линии в устройстве;

схему согласования линии;

допустимую длину линии и порядок подключения линий к соединительным элементам (разъемам);

требования к источникам и цепям электрического питания;

Слайд 110Шина ISA

(Industry Standart Architekture)

Архитектура шины

Однопроцессорная

Трехшинная архитектура

8,16 разрядов данных,24

разряда адреса

Асинхронная

Производительность 4мбайта/сек, частота 8мгц

11 линий прерывания,7 линий ПДП

Задатчики: ЦПр,

КПДП,Перестановщик байт

Блочной передачи нет

Два адресных пространства: ОЗУ, регистры Вв/Выв

Слайд 111Сигналы адреса и данных

SA(System

Adres)[19-0] - адрес с «защелкиванием»

LA(Latchable Adres)[24-17] -

адрес без «защелкивания»SD(System data)[15-0] – данные

# SBHE(System Bus High Enable) – передача старшего байта

BALE(Bus Adres Latch Enable) – строб адреса

AEN(Adres Enable) – разрешение ПДП

Сигналы команд

# MEMR(Memory Read) – чтение ОЗУ

# MEMW(Memory Write) – запись ОЗУ

# I/OR(Input Output Read) – чтение Вв-Выв

# I/OU(Input Output Write) – запись Вв-Выв

# MEMCS16(Memory Cycle Select) – 16раз. ОЗУ

# I/OCS16(Input Output Cycle Select) – 16раз. Вв-Выв

I/OCHRDY(I/O Cannel Ready) – готовность Вв-Выв

#OWS(O Wite States) – 0 циклов ожидания

# REFRESH – регенерация ОЗУ

Слайд 112Типы циклов шины

Ц Пр

Плата

расш.

Контр.

ПДП

Контр

рег.

16 р.

8 р.

16 р.

8 р.

16 р.

8

р.

ОЗУ

в/в.

ОЗУ

в/в.

ОЗУ, в/в

ОЗУ

0 такт ожид.

норм. цикл

удл. цикл

норм. цикл

удл. цикл

чтение

запись

чтение

Тип задатчика

Тип ресурса

Тип

памятиТип

цикла

Операция

Слайд 113 Сигналы управления

# Master – задатчик внешней

платы

# I/O CH CK(I/O Channel Check) –

ошибкаRESET – сброс

SYSCLC(System Clock) – синхроимпульсы,8мгц

OSC – генерация сигналов с частотой 12.3818мгц

Сигналы прерывания

IRQ(Interrup ReQuest) – сигналы прерывания

[15,14,12,11,10],[976543]

DRQ(Direct memory access ReQuest) – запрос ПДП

[7,6,5,0],[3,2,1]

DACK(DMA Request Acknowledge] – разрешение ПДП

[7,6,5,0],[3,2,1]

T/C(Terminal Count) – окончание ПДП

Слайд 114Шина PCI

(Peripheral Component Interconnect)

Базовая версия PCI:

Тактовая частота шины 33 МГц, используется синхронная передача данных;

Пиковая

пропускная способность 133 МБ в секунду; Параллельная шина данных шириною 32-бита;

Адресное пространство 32-бита (4 ГБ);

Сигнальный уровень 3.3 или 5 вольт.

Слайд 115Позже появляются следующие ключевые модификации шины:

PCI 2.2 — допускается 64-бит

ширина шины и/или тактовая частота 66 МГц, т.е. пиковая пропускная

способность до 533 МБ/сек.;PCI-X, 64-бит версия PCI 2.2 с увеличенной до 133 МГц частотой (пиковая пропускная полоса 1066 МБ/сек.);

PCI-X 266 (PCI-X DDR), DDR версия PCI-X (эффективная частота 266 МГц, реальная 133 МГц с передачей по обоим фронтам тактового сигнала, пиковая пропускная полоса 2.1 ГБ/сек);

PCI-X 533 (PCI-X QDR), QDR версия PCI-X (эффективная частота 533 МГц, пиковая пропускная полоса 4.3 ГБ/сек.);

Mini PCI — PCI с разъемом в стиле SO-DIMM, применяется преимущественно для миниатюрных сетевых, модемных и прочих карточек в ноутбуках;

Compact PCI — стандарт на форм фактор (модули вставляются с торца в шкаф с общей шиной на задней плоскости) и разъем, предназначенные в первую очередь для промышленных компьютеров и других критических применений;

Слайд 116Основные возможности шины PCI

1.Синхронный 32-х или 64-х разрядный обмен

данными. При этом для уменьшения числа контактов используется мультиплексирование, то

есть адрес и данные передаются по одним и тем же линиям.2.Поддержка 5V и 3.3V логики. Разъемы для 5 и 3.3V плат различаются расположением ключей (cуществуют универсальные платы, поддерживающие оба напряжения, но частота 66MHz поддерживается только 3.3V логикой).

3.Частота работы шины 33MHz или 66MHz (в версии 2.1) позволяет обеспечить широкий диапазон пропускных способностей (с использованием пакетного режима):

132 МВ/сек при 32-bit/33MHz;

264 MB/сек при 32-bit/66MHz;

264 MB/сек при 64-bit/33MHz;

528 МВ/сек при 64-bit/66MHz.

Для работы шины на частоте 66MHz необходимо, чтобы все периферийные устройства работали на этой частоте.

Слайд 1174.Полная поддержка multiply bus master (например, несколько контроллеров жестких дисков

могут одновременно работать на шине).

5.Автоматическое конфигурирование карт расширения при

включении питания. 6.Спецификация шины позволяет комбинировать до восьми функций на одной карте (например, видео + звук и т.д.).

7.Шина позволяет устанавливать до 5 слотов расширения, однако возможно использование моста PCI-PCI для увеличения количества карт расширения.

Слайд 1188.PCI-устройства оборудованы таймером, который используется для определения максимального промежутка времени,

в течении которого устройство может занимать шину.

9.Шина поддерживает метод передачи

данных, называемый метод линейных пакетов. Этот метод предполагает, что пакет информации считывается (или записывается) в непрерывное пространство памяти, то есть адрес автоматически увеличивается для следующего байта. Естественным образом при этом увеличивается скорость передачи собственно данных за счет уменьшения числа передаваемых адресовСлайд 122Базовые сигналы шины PCI

AD[31-0] – адрес – данные;

C/BE[3-0] – код

команды, указатель байт;

#FRAME – начало и конец транзакции;

#DEVSEL – исполнитель

найден;#IRDY – готовность задатчика, строб данных;

#TRDY – готовность исполнителя, строб данных;

#STOP – прерывание транзакции от исполнителя;

#LOCK – выполнение нескольких транзакций;

#REQ – запрос на захват шины;

#GNT – разрешение на захват шины;

IDSEL – выбор устройства при автоконфигурации;

PAR – контроль по четности A/D, C/BE;

#PERR – ошибка паритета;

#SERR – системная ошибка;

#RST – сброс;

CLK – синхроимпульс

Слайд 125 Производительность шины

AGP1х-266мбайт/сек

AGP2х-533мбайт/сек

AGP4x-1066мбайт/сек

AGP8x-2132мбайт/сек

Слайд 126Самый простой вариант перехода на PCI-Express для стандартных по архитектуре настольных

систем

Слайд 127Характеристики PCI -Express

Последовательная системная шина общего назначения;

Фактически —

совокупность независимых самостоятельных последовательных каналов передачи данных;

Сигнальный уровень 0.8

вольт. Каждый канал состоит из двух дифференциальных сигнальных пар (необходимо только 4 контакта): Используется избыточное защищенное от помех кодирование — каждый байт при передаче представляется десятью битами;

Пропускная способность 2.5 Гигабита (250 МБ) в секунду для одного канала в каждом направлении одновременно (полный дуплекс), однако, следует учесть, что эффективная скорость передачи данных за вычетом избыточного кодирования составляет 2 Гигабита (200 МБ) ровно;

Стандартизированы 1, 2, 4, 8, 16 и 32 канальные варианты (до 6.4 эффективных Гигабайт в секунду соответственно, при передаче в одну сторону и вдвое больше при передаче в обоих направлениях). При передаче данных они передаются параллельно (но не синхронно) по всем доступным каналам:

Вся контрольная информация передается по тем же линиям что и данные, используется стек протоколов, из нескольких уровней, включая маршрутизацию данных:

Стандарт предусматривает и альтернативные носители сигнала, такие как оптические волноводы;

Возможность динамического подключения и конфигурации устройств;

Возможность распознавания и использования альтернативных (улучшенных) протоколов обмена.

Слайд 129Сentronics

Электрические параметры.

Параметры передатчика:

1. Уровни сигналов

- без нагрузки Uс б/н =

0,5 - 5,5 В

- под нагрузкой Iн = 14 мА

Uс

п/н ³ 2,4 В - "1" (уровень ОН)Uс п/н £ 0,4 В - "0" (уровень ОL)

2. Выходной импеданс

Rвых = 50 ± 5 Ом

3. Скорость нарастания импульса

t =0,05 - 0,4 В/нс (10-20% от tимп)

Слайд 132SCASI

"+" - возможность подключения 7 устройств к одному компьютеру

- возможность

подключения широкого спектра устройств

- возможность подключения как внутренних, так и

внешних устройств- большая длина кабеля - 3…6 м, а в некоторых случаях - до 25м.

- может использоваться кэширование и технологии RAID-массивов.

- скорости при 8-битной шине 5МГц = 5Мб/с (это минимум)

"-" - высокая стоимость

Слайд 136Режимы работы IEEE-1284

Режим совместимости - однонаправленный вывод по протоколу Centronics

(соответствует стандарту порта SPP).

2. Полубайтный режим - ввод байта в

два цикла по 4 бита (использует для приема лини состояния). Используется в любых адаптерах портах.3. Байтный режим - ввод байта целиком. Используется в портах, допускающих чтение выходных данных.

4. Режим ЕРР - используется в портах, имеющих такое же название. Двунаправленный вывод данных. Управление шиной генерируется аппаратно во время цикла обращения к порту. Имеет повышенную скорость обмена. Используется для обмена с внешними

накопителями и адаптерами локальных сетей.

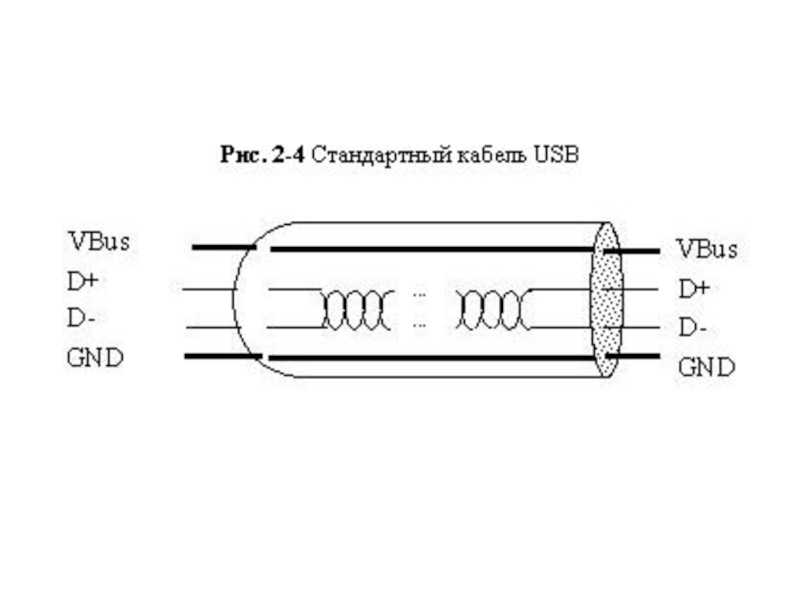

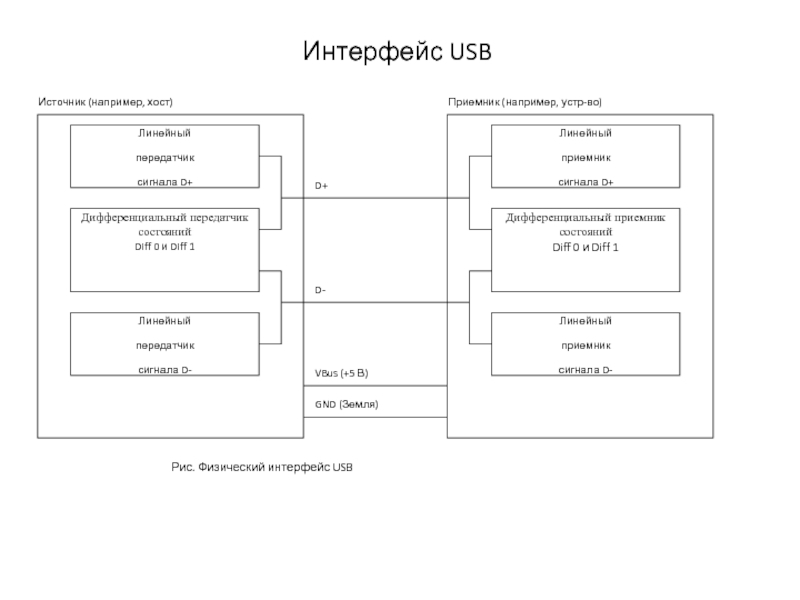

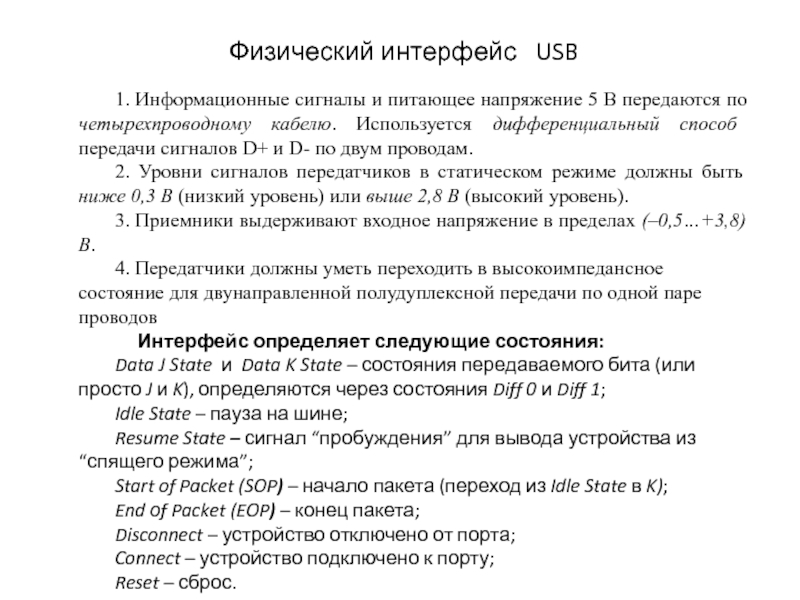

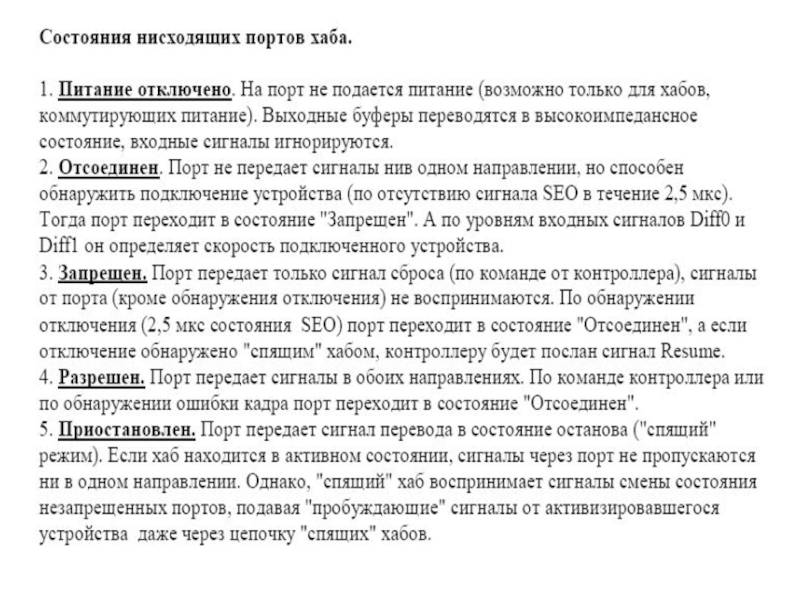

Слайд 146Физический интерфейс USB

1. Информационные сигналы и

питающее напряжение 5 В передаются по четырехпроводному кабелю. Используется дифференциальный способ передачи сигналов D+ и D- по двум проводам.2. Уровни сигналов передатчиков в статическом режиме должны быть ниже 0,3 В (низкий уровень) или выше 2,8 В (высокий уровень).

3. Приемники выдерживают входное напряжение в пределах (–0,5…+3,8) В.

4. Передатчики должны уметь переходить в высокоимпедансное состояние для двунаправленной полудуплексной передачи по одной паре проводов

Интерфейс определяет следующие состояния:

Data J State и Data K State – состояния передаваемого бита (или просто J и K), определяются через состояния Diff 0 и Diff 1;

Idle State – пауза на шине;

Resume State – сигнал “пробуждения” для вывода устройства из “спящего режима”;

Start of Packet (SOP) – начало пакета (переход из Idle State в K);

End оf Packet (EOP) – конец пакета;

Disconnect – устройство отключено от порта;

Connect – устройство подключено к порту;

Reset – сброс.

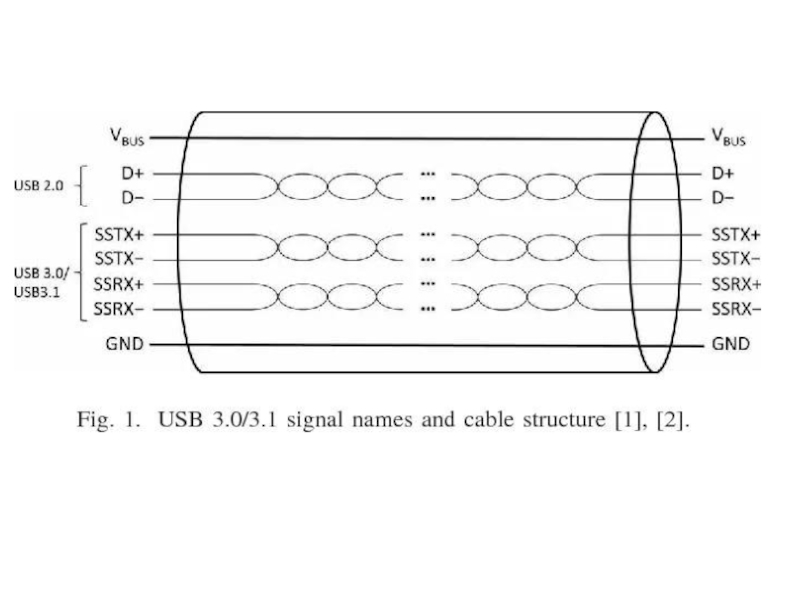

Слайд 150Окончательная спецификация USB 3.0 появилась в 2008 году. Созданием USB 3.0

занимались компании Intel, Microsoft, Hewlett-Packard, Texas Instruments, NEC и NXP Semiconductors.

Спецификация USB 3.0 повышает максимальную скорость передачи информации до

5 Гбит/с, что на порядок больше 480 Мбит/с, которые может обеспечить USB 2.0. Таким образом, скорость передачи возрастает с 60 МБ/с (30 МБ/с эффективных) до 600 МБ/с.Версия 3.0 отличается не только более высокой скоростью передачи информации, но и увеличенной силой тока с 500 мА до 900 мА.

В спецификации USB 3.0 разъёмы и кабели обновлённого стандарта физически и функционально совместимы с USB 2.0, причём для однозначной идентификации разъёмы USB 3.0 принято изготавливать из пластика синего цвета (у некоторых производителей — красного цвета).

Для передачи высокоскоростных SuperSpeed сигналов в USB 3.0 добавлено ещё четыре линии связи (две витые пары) и один контакт сигнальной земли (GND_DRAIN), в результате чего кабель стал гораздо толще.

Новые контакты в разъёмах USB 3.0 расположены отдельно от старых в другом контактном ряду.

![ЭВМ И ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА Расчет характеристикплотность поперечной записи информации на диске - Рпоп. [дор/мм]плотность продольной Расчет характеристикплотность поперечной записи информации на диске - Рпоп. [дор/мм]плотность продольной записи информации на диске – Рпр.](/img/thumbs/48714b769049c1d60bb7b43b0d175e7a-800x.jpg)

![ЭВМ И ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА Сигналы адреса и данных SA(System Adres)[19-0] - адрес с Сигналы адреса и данных SA(System Adres)[19-0] - адрес с «защелкиванием»](/img/thumbs/d6340645d8452906c5fbd03275c07cf3-800x.jpg)

![ЭВМ И ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА Базовые сигналы шины PCIAD[31-0] – адрес – данные;C/BE[3-0] – код команды, Базовые сигналы шины PCIAD[31-0] – адрес – данные;C/BE[3-0] – код команды, указатель байт;#FRAME – начало и конец](/img/thumbs/0a022db695cedea952959fc026f5b73d-800x.jpg)