Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Маршрут проектирования цифровых ИМС

Содержание

- 1. Маршрут проектирования цифровых ИМС

- 2. Суть блочно-иерархического подходарасчленение представлений об объекте проектирования,

- 3. Блочно-иерархический подход (Уровни представления интегральных схем)Уровень черного

- 4. Типовой маршрут проектирования Формирование ТЗСистемное проектированиеФункциональное проектированиеЛогическое

- 5. Формирование Технического Задания (ТЗ) Техническое задание –

- 6. Состав ТЗФункциональность ИМС (какую функцию она должна

- 7. Системное проектирование определяется архитектура будущей ИМС (какие

- 8. Верификация описания схемы Верификация – проверка правильности

- 9. Технология повторного использования разработок Некоторые блоки в

- 10. Функциональное проектирование Производится детализация поведенческого описания, до

- 11. Логическое проектирование На основе описания на RTL

- 12. Библиотека элементов (БЭ)это база данных логических вентилей.

- 13. БЭ (библиотека элементов)это набор кирпичиков, которые проектировщик

- 14. Схемотехническое проектирование На данном этапе согласно полученной

- 15. Топологическое проектирование Этап проектирования топологи требует гораздо

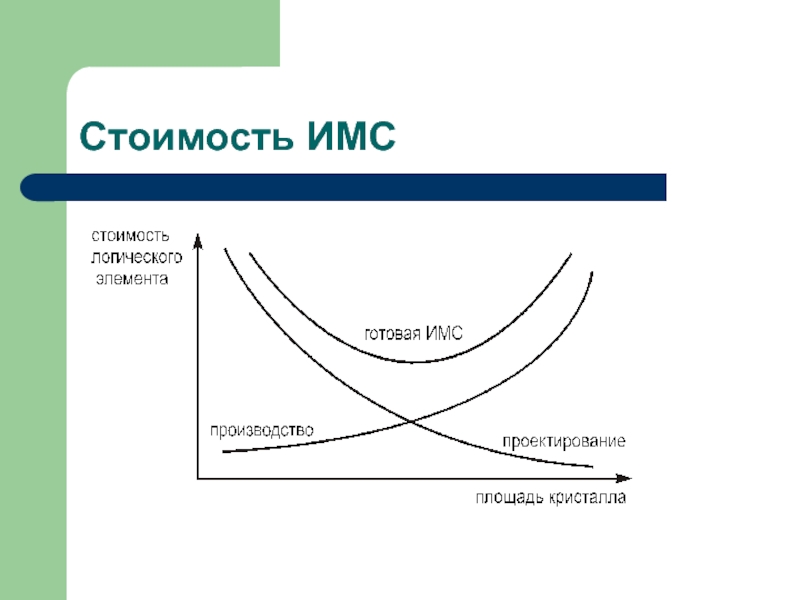

- 16. Стоимость ИМС

- 17. Маршрут топологического проектирования Разработка общего плана топологии Разработка топологииВерификация топологииЭкспертная проверкаИзготовление фотошаблонов

- 18. Разработка общего плана топологии Спланировать разводку шин

- 19. Разработка топологии Топология – дерево со стволом

- 20. Верификация (проверка топологии) Визуальный контроль топологии Design

- 21. Экспертная проверкаПроведение проверки правильности выполнения топологии независимым

- 22. Последний этапПеревод топологического представления в формат, стандартный

- 23. Скачать презентанцию

Суть блочно-иерархического подходарасчленение представлений об объекте проектирования, включая модели, постановка проектных задач, проектной документации и т.п. на ряд иерархических уровней, иначе называемых уровнями абстрагированияЦель расчленения – замена малого числа проектных задач

Слайды и текст этой презентации

Слайд 2Суть блочно-иерархического подхода

расчленение представлений об объекте проектирования, включая модели, постановка

проектных задач, проектной документации и т.п. на ряд иерархических уровней,

иначе называемых уровнями абстрагированияЦель расчленения – замена малого числа проектных задач чрезмерной сложности бОльшим числом задач допустимой сложности

Слайд 3Блочно-иерархический подход (Уровни представления интегральных схем)

Уровень черного ящика

Архитектурный уровень

Системный уровень

Логический

(вентильный) уровень

Схемотехнический уровень

Топологический уровень

(Каждый последующий уровень является детализацией предыдущего)

Слайд 4Типовой маршрут проектирования

Формирование ТЗ

Системное проектирование

Функциональное проектирование

Логическое проектирование

Схемотехническое проектирование

Топологическое проектирование

Изготовление

тестового кристалла

Производство

(с любого нижнего уровня можно вернуться на любой из

верхних)Слайд 5Формирование Технического Задания (ТЗ)

Техническое задание – это документ на

разработку микросхемы, который формируется в тесном сотрудничестве заказчика и проектировщика.

Исходя из требований заказчика и возможностей проектировщика, в этом документе определяются:Слайд 6Состав ТЗ

Функциональность ИМС (какую функцию она должна выполнять)

Параметры работы ИМС

(напряжение питания, тактовая частота, потребляемая мощность, рабочий диапазон температур, устойчивость

к излучениям и т.д.)технология производства ИМС

маршрут проектирования

сроки окончания этапов проектирования

порядок передачи проекта на производство и приемки изделия заказчиком

Слайд 7Системное проектирование

определяется архитектура будущей ИМС (какие блоки будут входить

в ее состав, как они будут взаимодействовать, определяются потоки данных

между блоками)соотношение «харда» и «софта» для наиболее оптимальной реализации функции, определенной в ТЗ

Составляется и моделируется поведенческое описание проекта, где каждый блок представляется в виде «черного ящика», выполняющего определенную функцию

Слайд 8Верификация описания схемы

Верификация – проверка правильности функционирования схемы на

данном уровне представления. На каждом этапе кроме топологического производится путем

моделирования описания схемы с использованием тестовых воздействий.если после верификации выясняется, что схема не удовлетворяет требованиям ТЗ или нормам проектирования, то производится модификация или выбирается другой вариант описания на данном уровне

Если все возможные варианты описаний исчерпаны, то проект возвращается на уровень вверх, где производится доработка описания или выбор иного варианта

Слайд 9Технология повторного использования разработок

Некоторые блоки в разных ИМС имеют

одинаковую функциональность и структуру

возможно повторное использование этих блоков для новых

разработок Это позволяет значительно сократить время проектирования

На этапе системного проектирования определяется возможность использования IP-блоков

Слайд 10Функциональное проектирование

Производится детализация поведенческого описания, до уровня регистровых передач

(RTL - Register Transfer Level)

Т.е. блоки, определенные декомпозицией на

предыдущем этапе представляются в виде набора регистров, сумматоров, логических блоков, триггеров, счетчиков и т.д. с описанием потоков данных между ними Слайд 11Логическое проектирование

На основе описания на RTL уровне разрабатывается описание

на вентильном уровне

Трансляция описания на регистровом уровне в логическую схему

производится средствами САПР, называемыми синтезаторами, а сам процесс трансляции синтезом. Синтезатор создает список вентилей и межсоединений между ними (Этот список может быть представлен в различных форматах, что удобно для интеграции различных САПР )Синтез логической схемы производится с использованием библиотеки элементов

Слайд 12Библиотека элементов (БЭ)

это база данных логических вентилей. Каждая запись в

такой базе данных содержит информацию о вентиле, которая включает в

себя: название элемента, выполняемая им логическая функция, его символическое обозначение, список входов и выходов, электрическая схема на транзисторном уровне, а также описание топологической ячейки, соответствующей этому вентилю. На этапе логического проектирования используется описание логической функции и список входов и выходов вентиля.Слайд 13БЭ (библиотека элементов)

это набор кирпичиков, которые проектировщик с помощью САПР

использует для создания ИМС. Создание БЭ является отдельной задачей, которая,

как правило, решается вне рамок разработки микросхемы. БЭ разрабатывается под конкретный технологический процесс. Но если проектируемая ИМС будет разрабатываться с использованием новой технологии, тогда в маршрут проектирования включается и разработка БЭСлайд 14Схемотехническое проектирование

На данном этапе согласно полученной логической схеме и

БЭ синтезируется электрическая схема. Для цифровых ИМС этот этап также

автоматизирован. Отдельно проектируются вспомогательные блоки, такие как источники напряжения, и входные выходные каскады, или же берутся готовые из библиотекиСлайд 15Топологическое проектирование

Этап проектирования топологи требует гораздо больших экономических и

временных затрат, чем любые другие этапы. Результаты проектирования топологии с

использованием автоматических средств САПР существенно хуже результатов, достигнутых с использованием ручного труда. Однако при ручном проектировании возрастает число ошибок, и увеличиваются сроки разработки, что для СБИС делает такой подход недопустимымСлайд 17Маршрут топологического проектирования

Разработка общего плана топологии

Разработка топологии

Верификация топологии

Экспертная

проверка

Изготовление фотошаблонов

Слайд 18Разработка общего плана топологии

Спланировать разводку шин питания, земли и

глобальных сигналов

Определить расположение контактных площадок для внешних сигналов

Определение

специальных требований к кристаллу Предварительное размещение блоков и приблизительный расчет площади кристалла

Определение требований, необходимых для контроля топологии

Слайд 19Разработка топологии

Топология – дерево со стволом (кристалл в целом),

ветками (блоки), малыми ветками (субблоки), листьями (топологические ячейки)

Разработка топологии

идет по направлению снизу-вверх, т.е. сначала разрабатывается структура топологических ячеек, которые обычно имеют сложность порядка нескольких транзисторовПервыми, на кристалле, размещаются блоки с наиболее критическими требованиями размещения

Слайд 20Верификация (проверка топологии)

Визуальный контроль топологии

Design Rules Check (DRC)

или проверка на соответствие правилам проектирования

Layout versus Schematics (LVS) или

сравнение топологии с электрической схемой Electrical Rules Check (ERC) или проверка на соответствие электрическим правилам проектирования