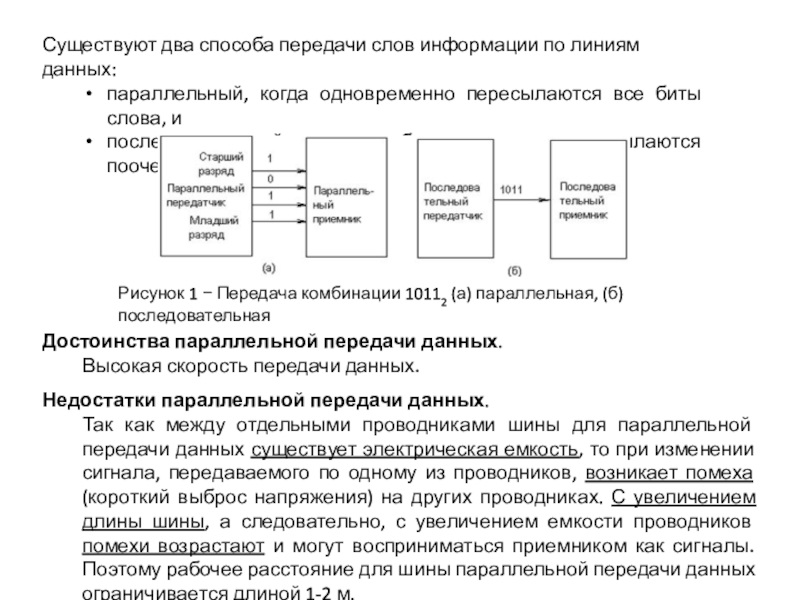

когда одновременно пересылаются все биты слова, и

последовательный, когда биты

слова пересылаются поочередно.Достоинства параллельной передачи данных.

Высокая скорость передачи данных.

Недостатки параллельной передачи данных.

Так как между отдельными проводниками шины для параллельной передачи данных существует электрическая емкость, то при изменении сигнала, передаваемого по одному из проводников, возникает помеха (короткий выброс напряжения) на других проводниках. С увеличением длины шины, а следовательно, с увеличением емкости проводников помехи возрастают и могут восприниматься приемником как сигналы. Поэтому рабочее расстояние для шины параллельной передачи данных ограничивается длиной 1-2 м.

Рисунок 1 Передача комбинации 10112 (а) параллельная, (б) последовательная