Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Микропроцессоры IBM.pptx

Содержание

- 1. Микропроцессоры IBM.pptx

- 2. РАННИЕ ПРОЕКТЫПроект 801 - начат в 1974

- 3. АРХИТЕКТУРАТрадиционая RISC-архитектура:Фиксированная длина командАрхитектура регистр-регистрПростые способы адресацииПростые(не требующие интерпретации) командыБольшой регистровый файлТрехоперандный формат команд

- 4. Отличия от других RISC-архитектур.1) Набор команд основан

- 5. 2) Расширена несколькими "смешанными" командами для сокращения

- 6. 3) Отсутствие механизма "задержанных переходов".Архитектура переходов POWER

- 7. POWER PC (1991)Спроектирован в соответствии с

- 8. При разработке архитектуры PowerPC для удовлетворения потребностей

- 9. POWER 2 (1993)Добавлены второй блок арифметико-логических

- 10. Слайд 10

- 11. Многокристальный набор POWER2 состоит из восьми полузаказных

- 12. POWER 3 (1998)Поддерживал весь набор 64-битных

- 13. POWER 4 (2001)Первый процессор, содержащий

- 14. POWER 5 (2004)Процессор стал двухъядерным, с

- 15. POWER 6 (2007)Привнес в стандарт POWER

- 16. POWER 7 (2010)На базе POWER7 построено

- 17. Компания IBM улучшила интегрированные аппаратно-программные возможности параллельной

- 18. ДРУГИЕ ПРОЦЕССОРЫ, РАЗРАБОТАННЫЕ НА АРХИТЕКТУРЕ POWER.Выпускался процессор

- 19. Дизайн процессора Cell основан на использовании простого

- 20. Скачать презентанцию

Слайды и текст этой презентации

Слайд 1ПРЕЗЕНТАЦИЯ НА ТЕМУ

МИКРОПРОЦЕССОРЫ IBM:

ОТ POWERPC ДО POWER7 И ИХ АРХИТЕКТУРА

Выполнила

студентка группы А-13-08

Слайд 2РАННИЕ ПРОЕКТЫ

Проект 801 - начат в 1974 году

- первый RISC-процессор, однотактовые команды

- внутреннее устройство POWER заимствовано из него

- в 1980-х выпушен компьютер IBM PC/RT

Проект «Америка» - 1985 г

- цель–самый производительный процессор

- вычисления с плавающей точкой

- тридцать два 32-разрядных целочисленных регистра и ещё тридцать два 64-разрядных регистра

Слайд 3АРХИТЕКТУРА

Традиционая RISC-архитектура:

Фиксированная длина команд

Архитектура регистр-регистр

Простые способы адресации

Простые(не требующие интерпретации) команды

Большой

регистровый файл

Трехоперандный формат команд

Слайд 4Отличия от других RISC-архитектур.

1) Набор команд основан на идее суперскалярной

обработки.

Команды распределяются по трем независимым исполнительным устройствам: устройству

переходов, устройству с фиксированной точкой и устройству с плавающей точкой. Любая связь по данным, требующаяся между устройствами, должна анализироваться компилятором.

Поддерживает степень параллелизма по крайней мере равную трем.

Слайд 52) Расширена несколькими "смешанными" командами для сокращения времен выполнения.

Задачи планирования,

разделяемые библиотеки и динамическое связывание как простой, единый механизм.

Возможность

модификации базового регистра вновь вычисленным эффективным адресом при выполнении операций загрузки или записи (аналог автоинкрементной адресации). Обширный набор команд для манипуляции битовыми полями, смешанные команды умножения-сложения с плавающей точкой, установку регистра условий в качестве побочного эффекта нормального выполнения команды и команды загрузки и записи строк.

Слайд 63) Отсутствие механизма "задержанных переходов".

Архитектура переходов POWER была организована для

поддержки методики "предварительного просмотра условных переходов« и методики "свертывания переходов».

4)

Методика реализации условных переходов.Наличие специального бита в коде операции каждой команды, что делает модификацию регистра условий дополнительной возможностью, и тем самым восстанавливает способность компилятора реорганизовать код.

Восемь регистров условий для того, чтобы обойти проблему единственного ресурса и обеспечить большее число имен регистра.

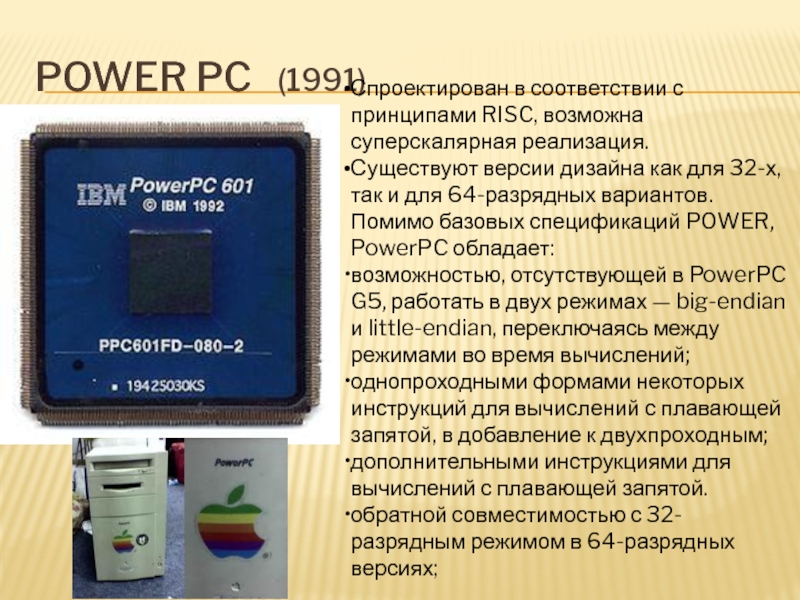

Слайд 7POWER PC (1991)

Спроектирован в соответствии с принципами RISC, возможна

суперскалярная реализация.

Существуют версии дизайна как для 32-х, так и

для 64-разрядных вариантов. Помимо базовых спецификаций POWER, PowerPC обладает:

возможностью, отсутствующей в PowerPC G5, работать в двух режимах — big-endian и little-endian, переключаясь между режимами во время вычислений;

однопроходными формами некоторых инструкций для вычислений с плавающей запятой, в добавление к двухпроходным;

дополнительными инструкциями для вычислений с плавающей запятой.

обратной совместимостью с 32-разрядным режимом в 64-разрядных версиях;

Слайд 8При разработке архитектуры PowerPC для удовлетворения потребностей трех различных компаний

(Apple, IBM и Motorola) было сделано несколько изменений в следующих

направлениях:упрощение архитектуры с целью ее приспособления ее для реализации дешевых однокристальных процессоров;

устранение команд, которые могут стать препятствием повышения тактовой частоты;

устранение архитектурных препятствий суперскалярной обработке и внеочередному выполнению команд;

добавление свойств, необходимых для поддержки симметричной многопроцессорной обработки;

добавление новых свойств, считающихся необходимыми для будущих прикладных программ;

ясное определение линии раздела между "архитектурой" и "реализацией";

обеспечение длительного времени жизни архитектуры путем ее расширения до 64-битовой.

Слайд 9POWER 2 (1993)

Добавлены второй блок арифметико-логических операций и второй

блок вычислений с плавающей точкой.

Был расширен набор команд:

инструкции записи

длиной в 4 машинных слова: перемещали два соседних значения двойной точности в два смежных регистра вычислений с плавающей точкой;вычисление квадратного корня на аппаратном уровне;

конвертация числа с плавающей точкой в целочисленное значение.

Производительность процессора POWER2 по сравнению с POWER значительно повышена: при тактовой частоте 71.5 МГц она достигает 131 SPECint92 и 274 SPECfp92.

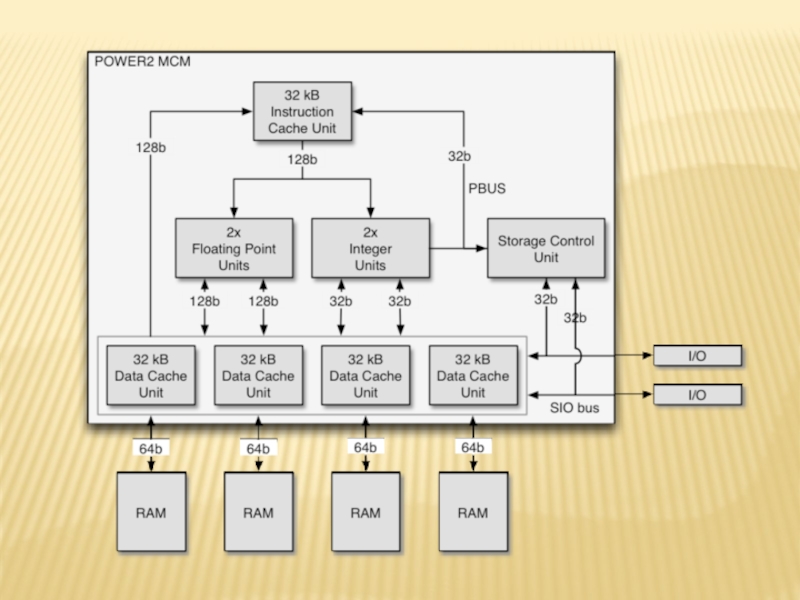

Слайд 11Многокристальный набор POWER2 состоит из восьми полузаказных микросхем (устройств):

Блок кэш-памяти

команд (ICU) - 32 Кбайт, имеет два порта с 128-битовыми

шинами;Блок устройств целочисленной арифметики (FXU) - содержит два целочисленных конвейера и два блока регистров общего назначения (по 32 32-битовых регистра). Выполняет все целочисленные и логические операции, а также все операции обращения к памяти;

Блок устройств плавающей точки (FPU) - содержит два конвейера для выполнения операций с плавающей точкой двойной точности, а также 54 64-битовых регистра плавающей точки;

Четыре блока кэш-памяти данных - максимальный объем кэш-памяти первого уровня составляет 256 Кбайт. Каждый блок имеет два порта. Устройство реализует также ряд функций обнаружения и коррекции ошибок при взаимодействии с системой памяти;

Блок управления памятью (MMU).

Слайд 12POWER 3 (1998)

Поддерживал весь набор 64-битных инструкций POWER, включая

все расширенные команды, имевшиеся на тот момент, и содержал два

блока вычислений с плавающей точкой, три блока с фиксированной точкой и два блока загрузки/выгрузки.Использован в серверах и рабочих станциях IBM RS/6000 на тактовой частоте 200 МГц.

Слайд 13POWER 4 (2001)

Первый процессор, содержащий 2 ядра.

Объединяет два

одинаковых процессора POWER3 на одной микросхеме, сделала их быстрее и

дополнила шинами быстродействующей связи с соседними процессорами (количеством до 3).Слайд 14POWER 5 (2004)

Процессор стал двухъядерным, с поддержкой мультипоточности (одновременного

выполнения двух цепочек команд), таким образом работая как 4 логических

процессора.С помощью технологии «Virtual Vector Architecture» (ViVA) несколько процессоров POWER5 могут объединяться в единый векторный процессор.

Улучшения по сравнению с POWER4 составили: больший по размеру кэш 2-го уровня, контроллер памяти непосредственно на кристалле, мультипоточность (ОС видит несколько процессоров вместо одного), усовершенствованный управление электропитанием, особый одноядерный режим.

Слайд 15POWER 6 (2007)

Привнес в стандарт POWER инструкции VMX (параллельная

обработка данных)

Достигает частот 3,5 ГГц, 4,2 ГГц, 4,7 ГГц, однако

в IBM заявляют, что опытные образцы достигают частоты в 6 ГГц. Процессор имеет два ядра и 128 КБ кэш I уровня.

Одно из главных отличий от архитектуры POWER5 заключается в том, что IBM сознательно отказалась от внеочередного исполнения команд и заменила его последовательным исполнением.

Слайд 16POWER 7 (2010)

На базе POWER7 построено несколько суперкомпьютеров:

PERCS

Blue Waters

IBM

Watson

Серверов

IBM Power 750

IBM Power 755

IBM Power 770

IBM Power 780

IBM

Power 795И блэйд-серверы:

BladeCenter PS700

BladeCenter PS701

BladeCenter PS702

Слайд 17Компания IBM улучшила интегрированные аппаратно-программные возможности параллельной обработки данных в

системах на базе процессоров Power7. Новые серверы Power Systems продолжают

традиции IBM в области скоростной обработки транзакций для приложений баз данных и быстро развиваются в направлении высокопроизводительных вычислительных систем, оптимизированных для выполнения крупномасштабных и ресурсоёмких приложений и сервисов Интернета.Три рабочих режима – обработка данных с высокой скоростью и высокой степенью параллелизма, высокопроизводительные вычисления и аналитические возможности – тесно интегрированы и согласованно управляются программными средствами IBM Systems Director.

Слайд 18ДРУГИЕ ПРОЦЕССОРЫ, РАЗРАБОТАННЫЕ НА АРХИТЕКТУРЕ POWER.

Выпускался процессор RS64, он был

основан на архитектуре PowerPC (а значит, и POWER) и использовался

в системах RS/6000 и AS/400. Оптимизирован для коммерческих расчётов и не обладает большой мощностью при вычислениях с плавающей точкой, характерных для POWER. Постепенно был вытеснен POWER4.Процессор Gekko был создан для игровой приставки Nintendo GameCube, представлял собой модифицированную версию PowerPC 750CXe. Процессор для приставок следующего поколения, Wii, был также разработан в стенах IBM.

Слайд 19Дизайн процессора Cell основан на использовании простого многопоточного ядра, работающего

на высокой тактовой частоте и связанного с восемью отдельными векторными

сопроцессорами. Используется в игровой приставке Sony PlayStation 3 и в некоторых задачах многократно превосходит по производительности настольные процессоры, что вызвало значительный интерес к этой разработке.Игровая приставка XBox 360, самое новое поколение приставок Microsoft, также опирается на процессор IBM Xenon, состоящий из трёх ядер, работающих на частоте 3,2 ГГц.