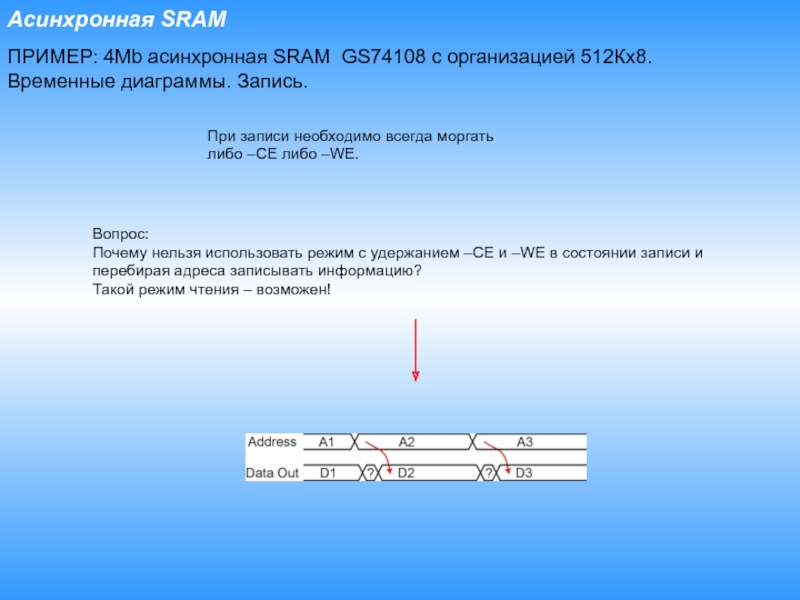

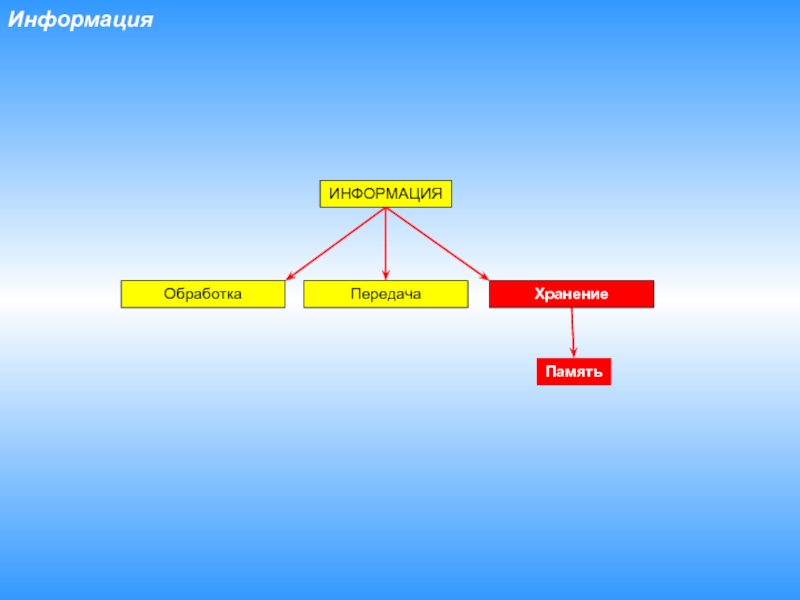

запись

Время доступа на чтение

Потребляемая мощность в режиме хранения

Потребляемая мощность в

режиме доступаПри современных технологиях либо одно, либо другое

![26 Характеристики памятиОбщие характеристикиОбъем [bit]БыстродействиеЭнергозависимостьСтоимостьПлотность [bit/sm3] или [bit/sm2] Время доступа на записьВремя Характеристики памятиОбщие характеристикиОбъем [bit]БыстродействиеЭнергозависимостьСтоимостьПлотность [bit/sm3] или [bit/sm2] Время доступа на записьВремя доступа на чтениеПотребляемая мощность в режиме](/img/thumbs/02019b5297bfe8b9bd1d8610217fdf84-800x.jpg)