n-разрядных чисел (слов).

На базе сумматора можно реализовать другие арифметические

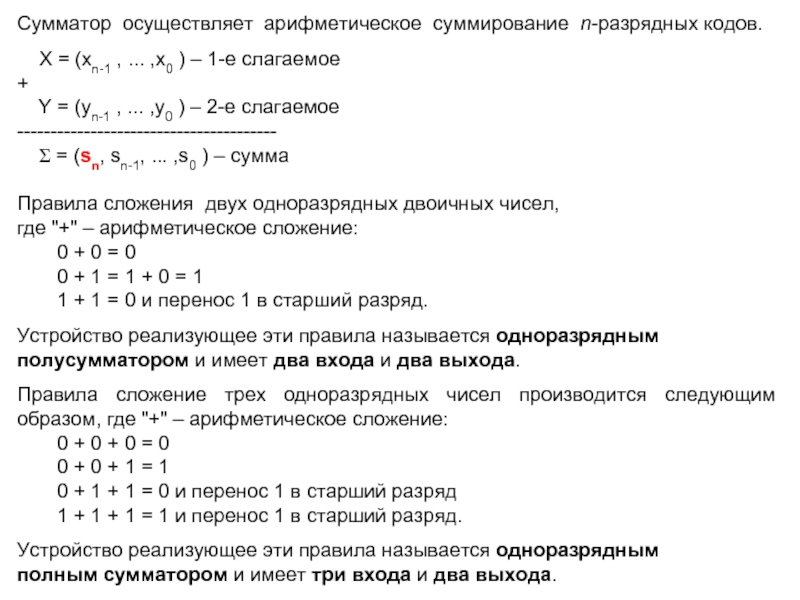

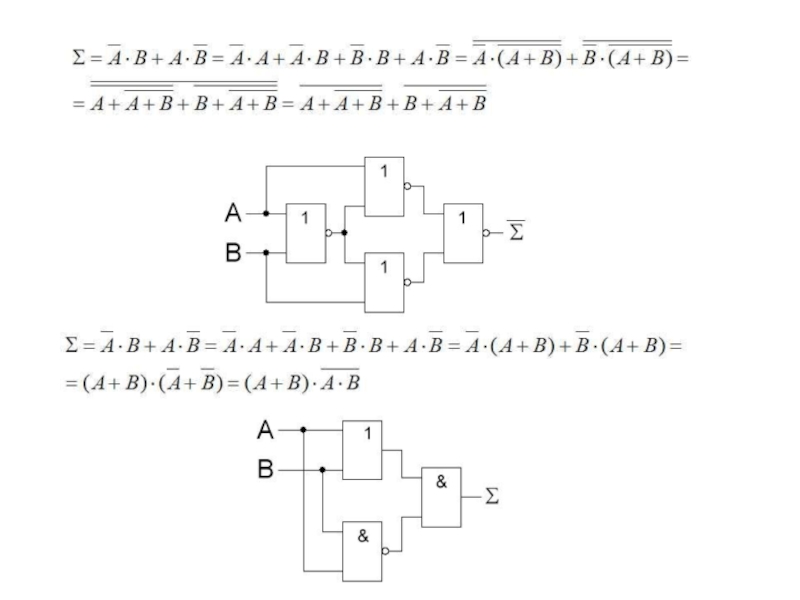

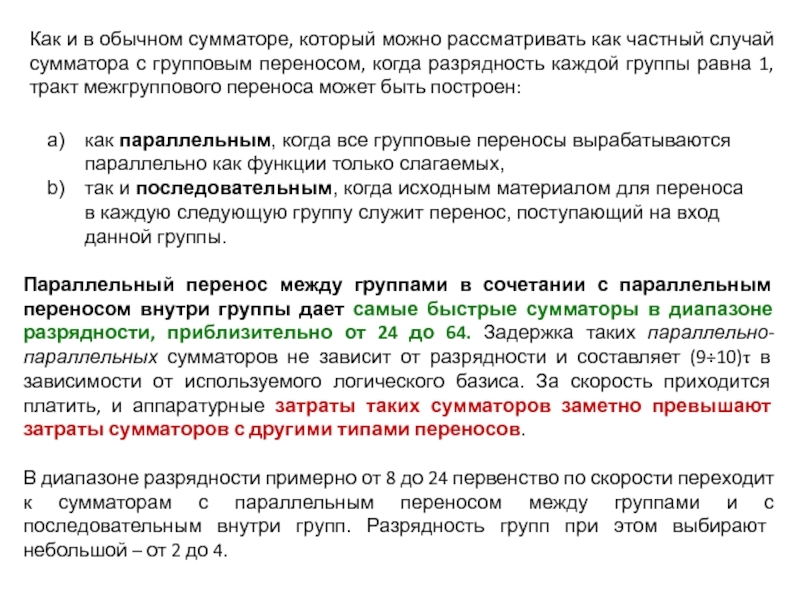

операции:Многоразрядный двоичный сумматор состоит из отдельных схем, которые называются одноразрядными двоичными сумматорами; они выполняют все действия по сложению значений одноименных разрядов двух чисел (операндов).

Поэтому сумматор является важнейшей частью любого арифметико-логического устройства (АЛУ).

Функция сумматора на его условно-графическом обозначении (УГО) на принципиальной электрической схеме обозначается буквами SM или S.

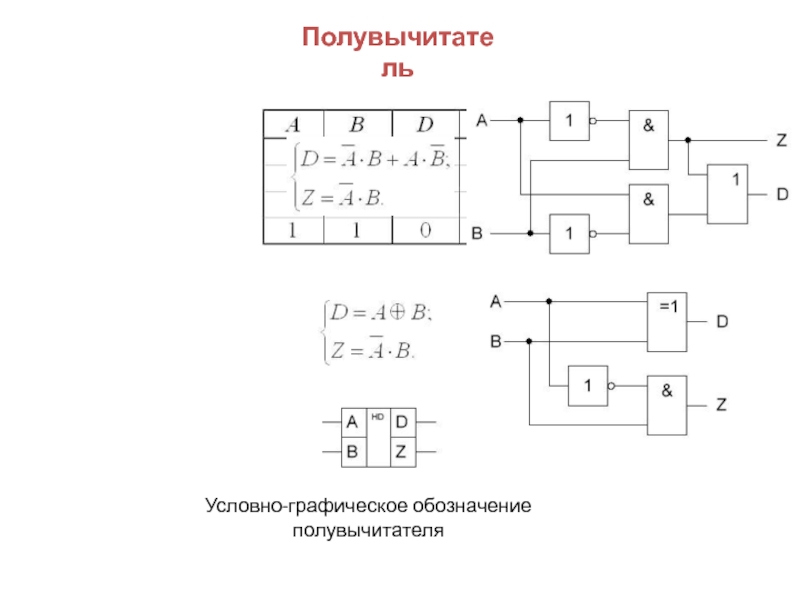

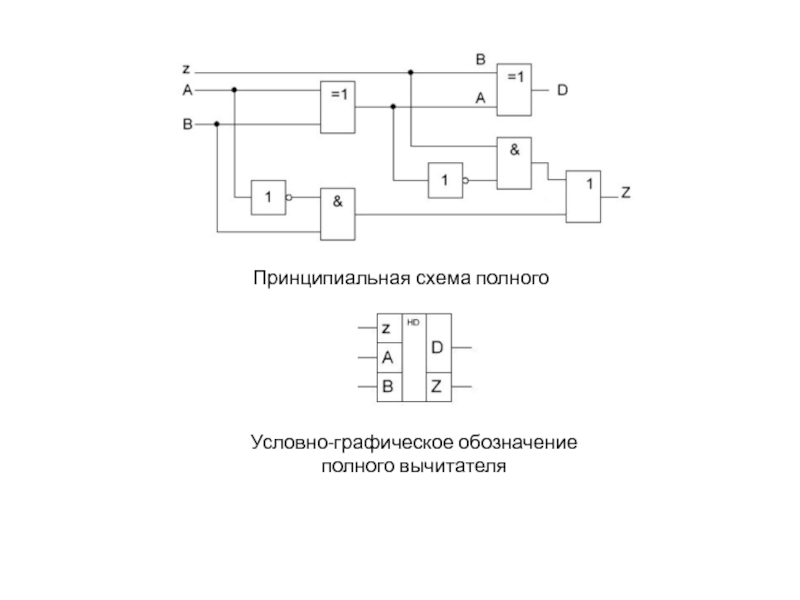

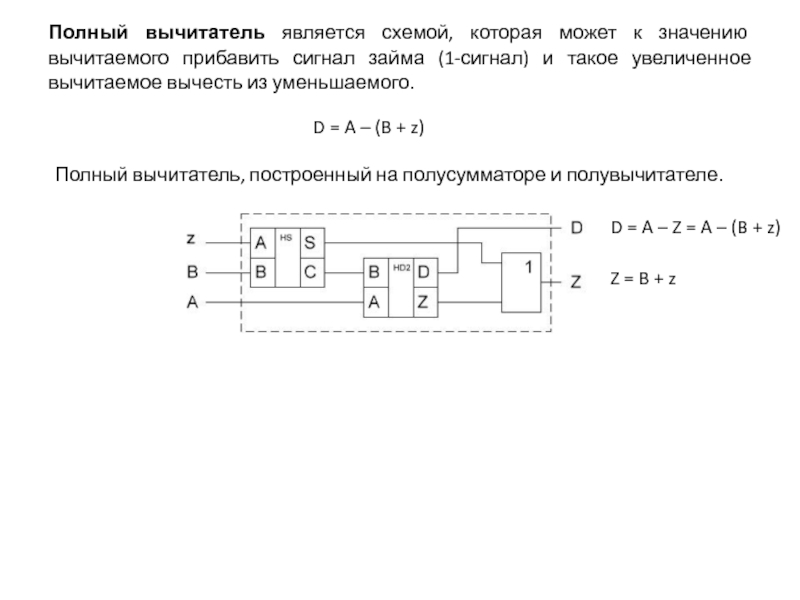

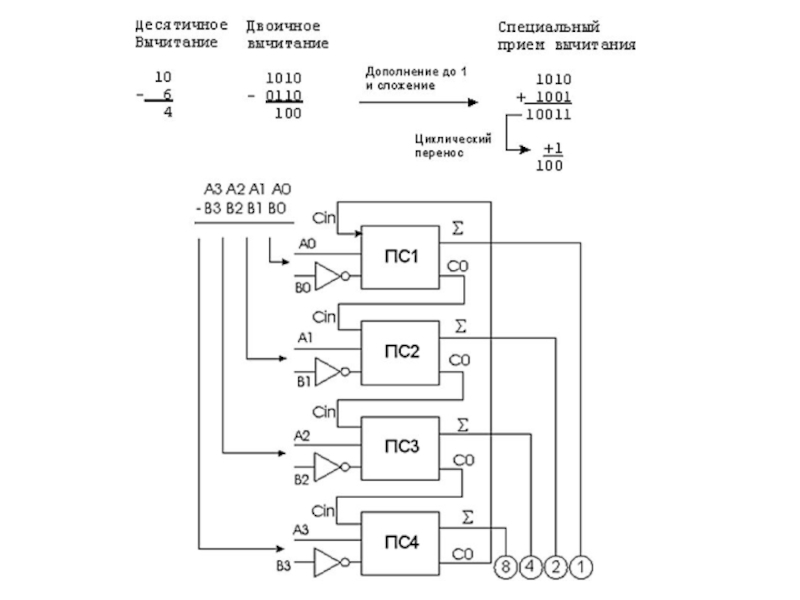

Операция вычитания заменяется сложением чисел представленных в обратном или дополнительном коде.

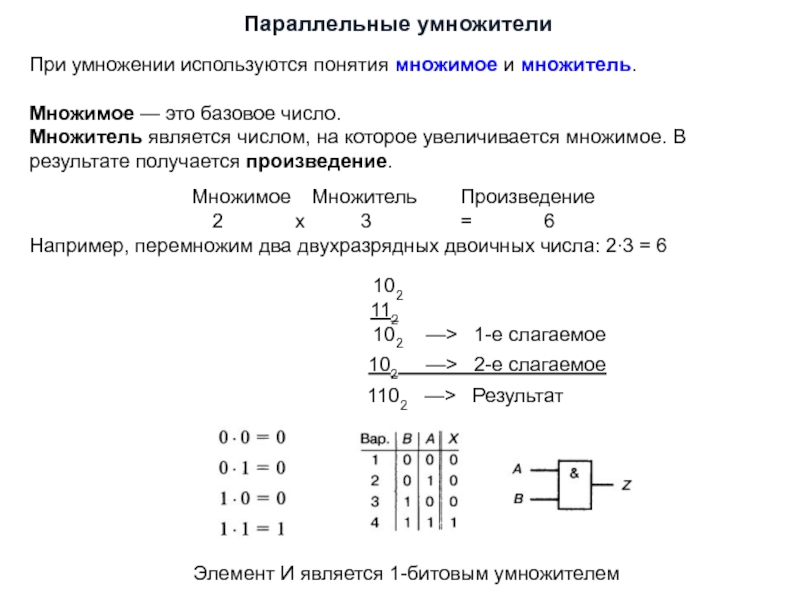

Операции умножения и деления сводятся к реализации операций многократных сложений и сдвигов.