Слайд 1Кафедра ИВТ

ВЫЧИСЛИТЕЛЬНАЯ ТЕХНИКА И ИНФОРМАЦИОННЫЕ ТЕХНОЛОГИИ

АСВТ

Рекомендуемая литература:

1. Угрюмов Е. Цифровая

схемотехника. – С-Петербург, изд-во «БХВ-Петербург», 2002.

2. Уэйкерли Дж.Ф. Проектирование

цифровых устройств, т.1, 2 / Пер. с англ. – М.: ПОСТМАРКЕТ, 2002.

3. Солонина А., Улахович Д., Яковлев Л. Алгоритмы и процессоры цифровой обработки сигналов. - С-Петербург, изд-во «БХВ-Петербург», 2001.

5. Вычислительные системы, сети и телекоммуникации: Учебник. – 2-е изд., перераб. И доп. / А.П. Пятибратов, Л.П. Гудыно, А.А. Кириченко; Под ред. А.П. Пятибратова – М.: Финансы и статистика, 2004.

6. Основы современных компьютерных технологий: Учебник / Под ред. проф. А.Д. Хомоненко. – СПб.: КОРОНА принт, 2005.

7. Безуглов Д.А., Калиенко И.В. Цифровые устройства и микропроцессоры. Учебное пособие для студентов высших учебных заведений. Ростов на Дону. ФЕНИКС- 2006, 480 с.

Слайд 21. ЛОГИЧЕСКИЕ ОСНОВЫ ЦИФРОВЫХ УСТРОЙСТВ

1.1. Понятие функции алгебры логики

Функция, однозначно

определяющая соответствие каждой из всех возможных совокупностей значений аргументов нулю

или единице, называется функцией алгебры логики (ФАЛ).

Логические переменные – как функция, так и аргументы, могут принимать только два значения. Обычно их обозначают символами 0 и 1.

Для технической реализации ФАЛ используют электрические схемы, называемые логическими элементами. Логический элемент (ЛЭ) выполняет логические операции над одной или более логическими переменными. При этом переменная-функция соответствует выходу ЛЭ, а переменные-аргументы – разрядам двоичных наборов, поступающим на соответствующие входы ЛЭ.

Закон функционирования ЛЭ представляют в виде таблицы истинности В строках первого раздела этой таблицы по порядку записываются десятичные номера входных двоичных наборов. В строках второго раздела записываются собственно входные наборы, представляющие собой n-разрядное двоичное отображение соответствующего десятичного номера. В строках третьего раздела записываются соответствующие входным наборам значения функции.

Слайд 3В общем случае ФАЛ строятся на основе элементарных ФАЛ. Элементарной

называется ФАЛ одного или двух аргументов, в логическом выражении которой

содержится не более одной логической операции.

К элементарным ФАЛ одного аргумента относятся:

1. Константа нуля. Реализуется генератором нуля, который на схемах обозначается соединением соответствующего входа ЛЭ с «землей» (общим проводом источника питания).

2. Константа единицы. Реализуется генератором единицы, который на схемах обозначается соединением соответствующего входа ЛЭ с полюсом источника питания.

3. Повторение. Реализуется логическим элементом повторителем. Записывается ФАЛ как у = х.

4. Инверсия или логическое отрицание. Реализуется логическим элементом НЕ (инвертором). . Записывается ФАЛ как у = x .

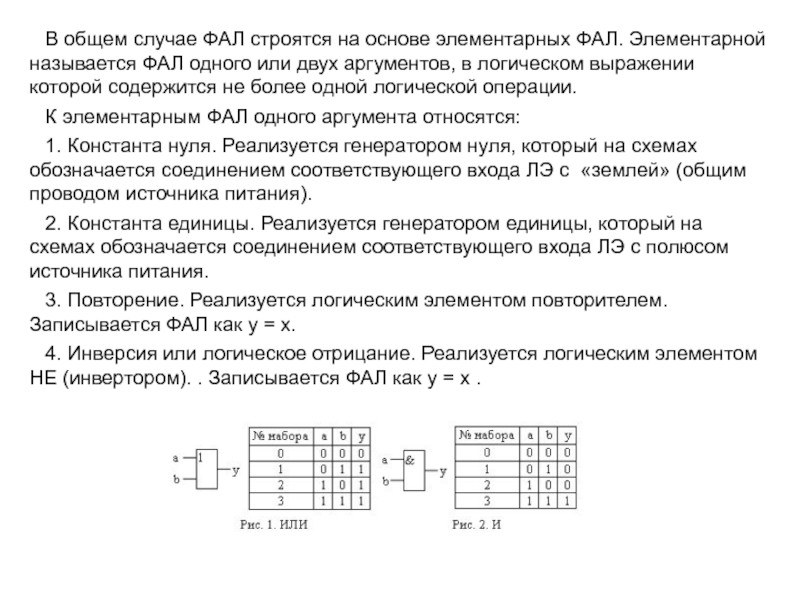

Слайд 4Основными из элементарных ФАЛ двух аргументов являются:

1. Дизъюнкция (логическое сложение).

Реализуется логическим элементом ИЛИ. Записывается ФАЛ как у = aVb.

2.

Конъюнкция (логическое умножение). Реализуется логическим элементом И. Записывается ФАЛ как у = a^b.

3. Стрелка Пирса. Реализуется логическим элементом ИЛИ-НЕ. . Записывается ФАЛ как и может быть представлена в сложной форме:

4. Штрих Шеффера. Реализуется логическим элементом И-НЕ. . Записывается ФАЛ как y = a | b и может быть представлена в сложной форме:

5. Исключающее ИЛИ (сложение по модулю два). Реализуется сумматором по модулю два. Записывается ФАЛ как у = и может быть представлена в сложной форме: у = b а

6. Эквивалентность. Реализуется одноименным ЛЭ. Записывается ФАЛ как

y = a∾b и может быть представлена в сложной форме:

у = = а b

Все рассмотренные функции могут быть расширены на произвольное число аргументов.

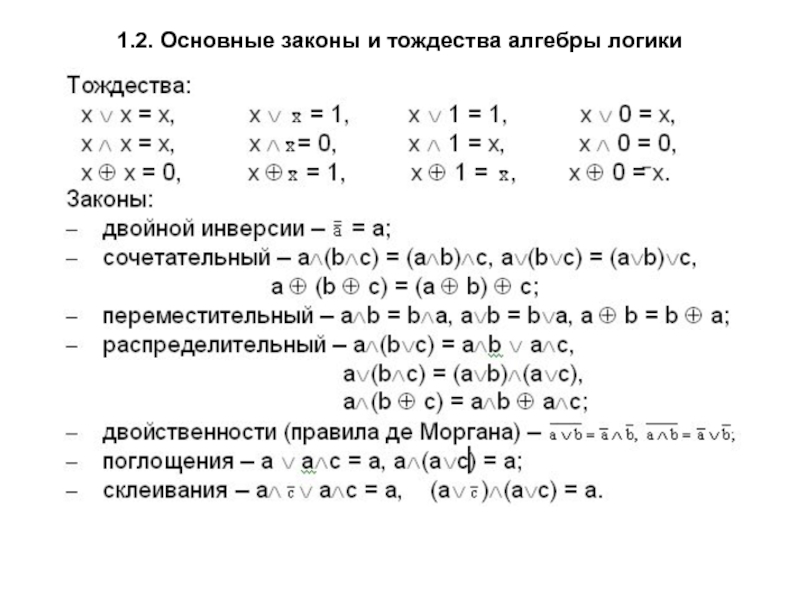

Слайд 51.2. Основные законы и тождества алгебры логики

Слайд 6Все указанные законы и тождества справедливы для любого числа аргументов,

причем аргументом может быть как простая переменная, так и функция.

Законы

и тождества алгебры логики используются для преобразования ФАЛ в процессе синтеза цифровых устройств. В частности, целью преобразования может быть упрощение ФАЛ:

Кроме того, в тождествах отражены правила замены логических элементов одного типа логическими элементами другого типа.

2. КОМБИНАЦИОННЫЕ ЦИФРОВЫЕ УСТРОЙСТВА

2.1. Понятие и последовательность синтеза

Любое цифровое устройство можно рассматривать как преобразователь входных n-разрядных двоичных наборов в выходные m-разрядные двоичные наборы. Поскольку n определяется числом информационных входов цифрового устройства, длина (число разрядов) входных двоичных наборов постоянна и не зависит от их значения. Тогда общее число входных двоичных наборов не превышает 2n и, следовательно, диапазон десятичных чисел, которые могут быть обработаны таким цифровым устройством составляет от 0 до Мmax = 2n – 1.

Слайд 7Отсюда легко решается обратная задача: число разрядов, необходимое для представления

в цифровом устройстве абсолютных значений десятичных чисел от Мmin до

Мmax определяется из соотношения: n = log2(Мmax + 1), где x – наименьшее целое, не меньшее х.

Физически значения разрядов (логических переменных) двоичных наборов отображаются электрическими сигналами в одной из двух форм – потенциальной или импульсной.

В потенциальной форме (рис. 10,а) единичному значению двоичного разряда соответствует высокий уровень напряжения U1, а нулевому – низкий уровень U0, близкий к «земле». В импульсной форме (рис. 10,б) единичному значению двоичного разряда соответствует относительно короткий импульс, а нулевому – отсутствие импульса.

Слайд 8Как видно, в любой форме сигналы могут принимать только два

значения и потому называются двоичными сигналами. В этой терминологии и

определим комбинационное цифровое устройство (КЦУ): комбинационным называется цифровое устройство, у которого выходные двоичные сигналы в любой момент времени зависят только от тех двоичных сигналов, которые поступают на вход устройства в тот же момент времени. Таким образом, сигналы на выходе КЦУ изменяются практически сразу после изменения входных сигналов.

В реальных цифровых устройствах каждые входной и соответствующий ему выходной двоичные наборы отображаются двоичными сигналами лишь в течение определенного интервала времени, называемого тактом (рис. 10,в). При этом говорят, что устройство тактируется, то есть входные и выходные сигналы могут изменяться лишь с началом (окончанием) каждого последующего такта.

КЦУ называется полностью определённым, если каждому из всех его возможных входных двоичных наборов поставлен в соответствие строго определенный двоичный набор на выходе. Если хотя бы для одного входного набора значение одного или более разрядов соответствующего выходного набора безразлично, КЦУ называется не полностью или частично определённым. На практике частично определенные КЦУ соответствуют ситуациям, когда некоторые двоичные наборы либо никогда не появляются на входе, либо никогда не оказываются востребованными на выходе.

Слайд 9Синтез любого КЦУ проводится в следующей последовательности:

1. Задается закон функционирования.

2.

Для каждого из m выходов выводится минимальная ФАЛ, то есть

ФАЛ с минимальным числом членов и минимальным числом аргументов в каждом члене.

3. При необходимости каждая минимальная ФАЛ записывается в заданном минимальном базисе.

4. В соответствии с системой минимальных ФАЛ строится структурная схема устройства.

2.2. Способы задания КЦУ

1.Табличный. Правила работы задаются таблицей истинности. При этом в случае частично определенного КЦУ строки раздела «Выходной набор» таблицы, соответствующие безразличным входным наборам, заполняются символом тильда (рис. 11). Однако при большом значении n таблица истинности становится громоздкой и теряет наглядность.

Слайд 102.Скобочная запись таблицы истинности.

В случае полностью определенного КЦУ для каждого

разряда выходного набора в круглых (квадратных) скобках через запятую перечисляются

десятичные номера входных наборов, на которых значение этого разряда обращается в 0 (1).

Например, запись уi(n = 4) = [1, 8, 15] означает, что i-й разряд выходных наборов имеет значение 1 на первом, восьмом и пятнадцатом n-разрядных входных наборах. Следовательно, на остальных ( 16– 3 = 13) не указанных нборах, этот разряд имеет значение 0.

В случае частично определенного КЦУ используются оба вида скобок, что позволяет не указывать безразличные входные наборы.

Например, запись уi(n = 4) = [1, 8, 15, (0, 6)] = (0, 6, [1, 8, 15]) означает, что i-й разряд выходных наборов принимает значение 1 на первом, восьмом и пятнадцатом входных наборах, значение 0 – на нулевом и шестом, и его значение безразлично на остальных (24 – 5 = 11) не указанных входных наборах.

3.Аналитический. Правила работы КЦУ задаются системой ФАЛ, каждая из которых соответствует определенному выходу КЦУ и записывается на основании таблицы истинности или ее скобочного представления в любой из двух совершенных форм – дизъюнктивной (СДНФ) или конъюнктивной (СКНФ).

Слайд 11Правила записи ФАЛ в совершенной форме:

ФАЛ в СДНФ (СКНФ) представляется

дизъюнкцией (конъюнкцией) своих членов, каждый из которых соответствует единственному и

строго определенному входному набору, обращающего данную функцию в 1 (0) или соответствующего безразличному ее значению;

каждый член функции в СДНФ (СКНФ) образуется конъюнкцией (дизъюнкцией) всех аргументов, которые берутся с инверсией при нулевом (единичном) значении в данном входном наборе и без инверсии – при единичном (нулевом). Таким образом, каждый член функции в СДНФ (СКНФ) является функцией конституанты 1 (0).

2.3. Вывод минимальной ФАЛ

Существуют графические и алгебраические методы минимизации ФАЛ. Из графических наибольшее распространение получил метод карт Вейча-Карно, а из алгебраических – метод Квайна.

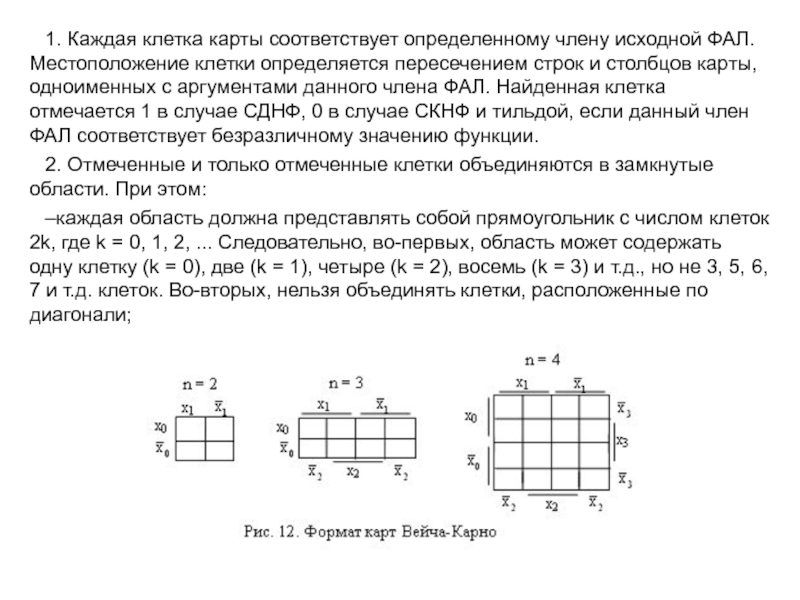

Карта Вейча-Карно представляет собой таблицу истинности специальной формы с числом клеток 2n (рис. 12), где n – длина входных наборов КЦУ.

Минимизация методом карт Вейча-Карно проводится в следующей последовательности:

Слайд 121. Каждая клетка карты соответствует определенному члену исходной ФАЛ. Местоположение

клетки определяется пересечением строк и столбцов карты, одноименных с аргументами

данного члена ФАЛ. Найденная клетка отмечается 1 в случае СДНФ, 0 в случае СКНФ и тильдой, если данный член ФАЛ соответствует безразличному значению функции.

2. Отмеченные и только отмеченные клетки объединяются в замкнутые области. При этом:

–каждая область должна представлять собой прямоугольник с числом клеток 2k, где k = 0, 1, 2, ... Следовательно, во-первых, область может содержать одну клетку (k = 0), две (k = 1), четыре (k = 2), восемь (k = 3) и т.д., но не 3, 5, 6, 7 и т.д. клеток. Во-вторых, нельзя объединять клетки, расположенные по диагонали;

Слайд 13–число клеток в области должно быть максимально возможным, поскольку только

тогда число аргументов в соответствующем члене выводимой функции будет минимальным;

–одни и те же клетки могут входить в разные области, т.е. области могут пересекаться;

–при условии участия всех отмеченных клеток в процедуре формирования областей следует стремиться к минимальному числу областей, поскольку только тогда число членов выводимой функции будет минимальным. С этой целью допускается сворачивание карты в цилиндр относительно горизонтальной и/или вертикальной осей с соединением противоположных граней.

Учет безразличных входных наборов (клеток, помеченных тильдой) повышает эффективность минимизации. Однако если эти клетки не способствуют расширению областей, их следует считать пустыми.

3. В соответствии с выделенными областями записывается минимальная ФАЛ в дизъюнктивной (если исходной была СДНФ) или конъюнктивной (если исходной была СКНФ) нормальной форме. При этом каждая область определяет отдельный член минимальной функции, который составляется лишь из тех аргументов, которые в данную область входят либо только с инверсией, либо только без инверсии.

Слайд 14Минимизация методом Квайна заключается в следующем.

1. Члены исходной ФАЛ, где

учтены и безразличные входные наборы, отличающиеся только в одной переменной,

группируются в пары.

Две ФАЛ отличаются в одной переменной, если эта переменная в одну из них входит с инверсией, а в другую без инверсии. Других различий нет.

При группировке руководствуются следующими правилами:

–пары могут пересекаться, т.е. один и тот же член функции может входить в различные пары;

–при условии участия в процедуре группирования всех членов ФАЛ, число пар должно быть минимальным.

2. К сформированным парам в случае СДНФ применяется операция склеивания, а в случае СКНФ – операция поглощения.

3. По результатам преобразования записывается новая ФАЛ, к которой применяются законы и тождества алгебры логики или повторно все пункты минимизации. При этом полезным бывает соотношение

Слайд 152.4. Базисы и минимальные базисы

Полным базисом называется система ФАЛ, позволяющая

представить любую функцию от произвольного числа аргументов. Полный базис допускает

использование логических элементов самых различных типов: И, ИЛИ, И-НЕ, ИЛИ-НЕ, НЕ и т.д.

Минимальным базисом называется минимальный набор ФАЛ, позволяющий представить любую функцию от произвольного числа аргументов. Минимальный базис допускает использование логических элементов только одного строго определенного типа. Из минимальных базисов наибольшее практическое применение получили базисы И-НЕ и ИЛИ-НЕ.

ФАЛ в базисе ИЛИ-НЕ может содержать только операции стрелка Пирса, а в базисе И-НЕ – только операции штрих Шеффера. Вместе с тем допустимо использование операции инверсии, а, следовательно, в технической реализации – логического элемента НЕ.

Для представления минимальной ФАЛ в любом из минимальных базисов используются законы двойной инверсии и двойственности.

Например, ФАЛ у = х2х3 х1х0 запишется в базисе И-НЕ следующим

образом: =

Слайд 162.5. Построение структурной схемы

Структурная схема ЦУ представляет собой совокупность условных

графических изображений логических элементов, типовых цифровых устройств и связей между

ними.

Элементной базой при технической реализации цифровых устройств являются интегральные схемы различной степени интеграции.

На структурных схемах компоненты микросхем нумеруются слева направо и сверху вниз, то есть построчно. При этом используются две латинские буквы DD, за которыми следуют номер микросхемы в устройстве и через точку номер компоненты в микросхеме. Если микросхема содержит один компонент (логический элемент или типовое устройство), то используется одна буква D и номер компоненты в нумерации отсутствует.

Последовательность построения структурной схемы устройства, реализующего данную ФАЛ или систему ФАЛ, определяется приоритетностью логических операций: старшей является инверсия, затем следует конъюнкция и, наконец, операции типа дизъюнкции – дизъюнкция, исключающее ИЛИ и эквивалентность.

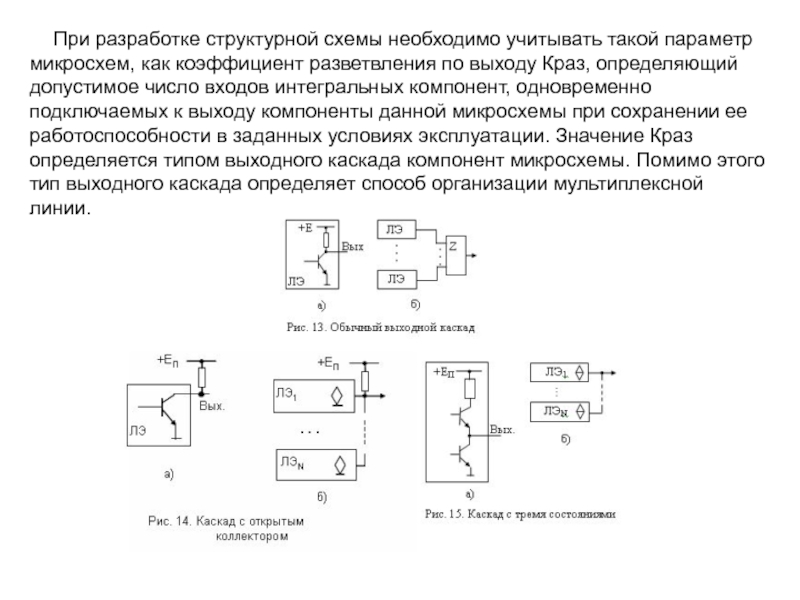

Слайд 17При разработке структурной схемы необходимо учитывать такой параметр микросхем, как

коэффициент разветвления по выходу Краз, определяющий допустимое число входов интегральных

компонент, одновременно подключаемых к выходу компоненты данной микросхемы при сохранении ее работоспособности в заданных условиях эксплуатации. Значение Краз определяется типом выходного каскада компонент микросхемы. Помимо этого тип выходного каскада определяет способ организации мультиплексной линии.

Слайд 18Мультиплексирование – поочередное подключение к линии передачи на время Т

выхода каждого из N логических элементов или цифровых устройств.

Выходные каскады

выполняются в одном из трех основных вариантов.

1. Обычный каскад (рис. 13, а). Краз.= 10.

Выход имеет два устойчивых состояния – 0 (транзистор открыт) и 1 (транзистор закрыт).

При организации мультиплексной линии (рис. 13,б) требуется дополнительный ЛЭ Z, тип которого (И либо ИЛИ) зависит от значения выходного сигнала логических элементов в состоянии закрытого ключа.

2. Каскад с открытым коллектором (рис. 14,а). Краз.= 16.

Для обеспечения устойчивого состояния 1 выход через внешний резистор подключается к источнику питания.

Повышенное значение Краз объясняется возможностью регулирования выходного тока путем изменения сопротивления резистора.

Исполнение выходных каскадов с открытым коллектором отмечается на корпусе микросхемы символом в виде подчеркнутого ромба (рис. 14,б).

Мультиплексная линия образуется соединением выходов всех N логических элементов на одном общем внешнем резисторе (рис. 14,б).

Слайд 19Такое включение эквивалентно использованию дополнительного логического элемента ИЛИ, поэтому его

называют "монтажным (проводным) ИЛИ".

3. Каскад с тремя состояниями (рис. 15,а).

Краз.= 10.

Здесь возможны три ситуации:

– напряжение логического нуля на выходе соответствует открытому нижнему транзистору;

– напряжение логической единицы на выходе соответствует закрытому нижнему и открытому верхнему транзистору;

– при обоих закрытых транзисторах выход отключен от цепей питания. Это и есть третье (безразличное) состояние.

Исполнение выходных каскадов с тремя состояниями отмечается на корпусе микросхемы символом в виде ромба с поперечной линией (рис. 15,б).

Мультиплексная линия образуется «монтажным ИЛИ» без дополнительного резистора (рис. 15,б).

Слайд 202.6. Типовые КЦУ

На входы типовых КЦУ могут подаваться два вида

сигналов – информационные сигналы и сигналы управления. Информационные сигналы отображают

обрабатываемую информацию, а сигналы управления выполняют одну или несколько из следующих функций:

переключение входных информационных сигналов на определенные выходы устройства;

задание порядка формирования выходных сигналов;

синхронизация работы устройства. Синхросигнал задает временной интервал между любыми двумя соседними моментами срабатывания устройства и отображается тактовыми импульсами (тактами);

стробирование устройства. Сигнал стробирования задает временной интервал, в течение которого выходы устройства разблокированы и на них передается результат обработки информационных сигналов.

Разрешающее значение управляющего сигнала называется активным. На условном графическом обозначении типовых КЦУ всегда указывается именно активный управляющий сигнал: нулевой знаком инверсии , единичный – его отсутствием . Аналогично для некоторых КЦУ указываются и активные значения выходных сигналов

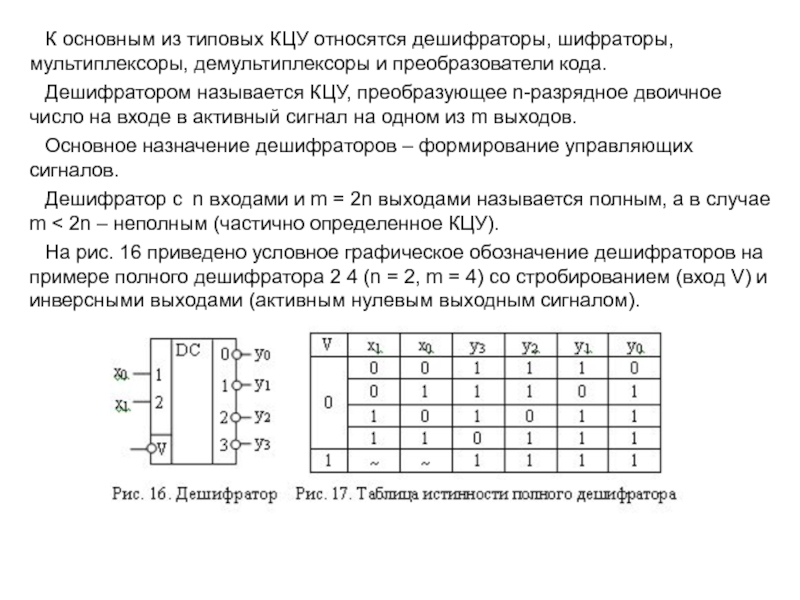

Слайд 21К основным из типовых КЦУ относятся дешифраторы, шифраторы, мультиплексоры, демультиплексоры

и преобразователи кода.

Дешифратором называется КЦУ, преобразующее n-разрядное двоичное число на

входе в активный сигнал на одном из m выходов.

Основное назначение дешифраторов – формирование управляющих сигналов.

Дешифратор с n входами и m = 2n выходами называется полным, а в случае m < 2n – неполным (частично определенное КЦУ).

На рис. 16 приведено условное графическое обозначение дешифраторов на примере полного дешифратора 2 4 (n = 2, m = 4) со стробированием (вход V) и инверсными выходами (активным нулевым выходным сигналом).

Слайд 22Информационные входы обозначаются весовыми коэффициентами двоичных разрядов, что устанавливает однозначное

соответствие между номером входа дешифратора и номером разряда двоичного набора.

Для выходов используется сквозная нумерация.

Таблица истинности полных дешифраторов, ограниченная дешифратором рис. 16, показана на рис. 17. Из таблицы видно, что номер выхода, на котором появляется активный сигнал, является десятичным эквивалентом текущего двоичного набора на информационных входах. В маркировке микросхем дешифраторов используются буквы ИД.

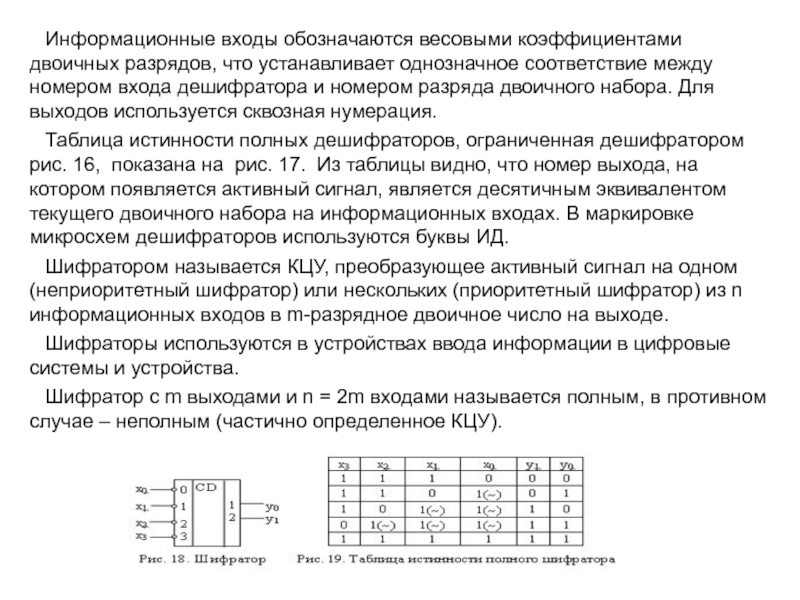

Шифратором называется КЦУ, преобразующее активный сигнал на одном (неприоритетный шифратор) или нескольких (приоритетный шифратор) из n информационных входов в m-разрядное двоичное число на выходе.

Шифраторы используются в устройствах ввода информации в цифровые системы и устройства.

Шифратор с m выходами и n = 2m входами называется полным, в противном случае – неполным (частично определенное КЦУ).

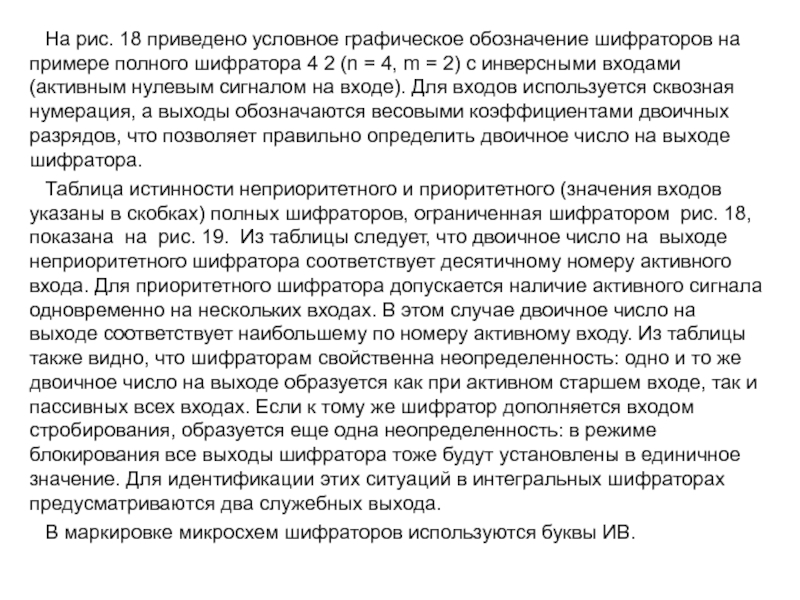

Слайд 23На рис. 18 приведено условное графическое обозначение шифраторов на примере

полного шифратора 4 2 (n = 4, m = 2)

с инверсными входами (активным нулевым сигналом на входе). Для входов используется сквозная нумерация, а выходы обозначаются весовыми коэффициентами двоичных разрядов, что позволяет правильно определить двоичное число на выходе шифратора.

Таблица истинности неприоритетного и приоритетного (значения входов указаны в скобках) полных шифраторов, ограниченная шифратором рис. 18, показана на рис. 19. Из таблицы следует, что двоичное число на выходе неприоритетного шифратора соответствует десятичному номеру активного входа. Для приоритетного шифратора допускается наличие активного сигнала одновременно на нескольких входах. В этом случае двоичное число на выходе соответствует наибольшему по номеру активному входу. Из таблицы также видно, что шифраторам свойственна неопределенность: одно и то же двоичное число на выходе образуется как при активном старшем входе, так и пассивных всех входах. Если к тому же шифратор дополняется входом стробирования, образуется еще одна неопределенность: в режиме блокирования все выходы шифратора тоже будут установлены в единичное значение. Для идентификации этих ситуаций в интегральных шифраторах предусматриваются два служебных выхода.

В маркировке микросхем шифраторов используются буквы ИВ.

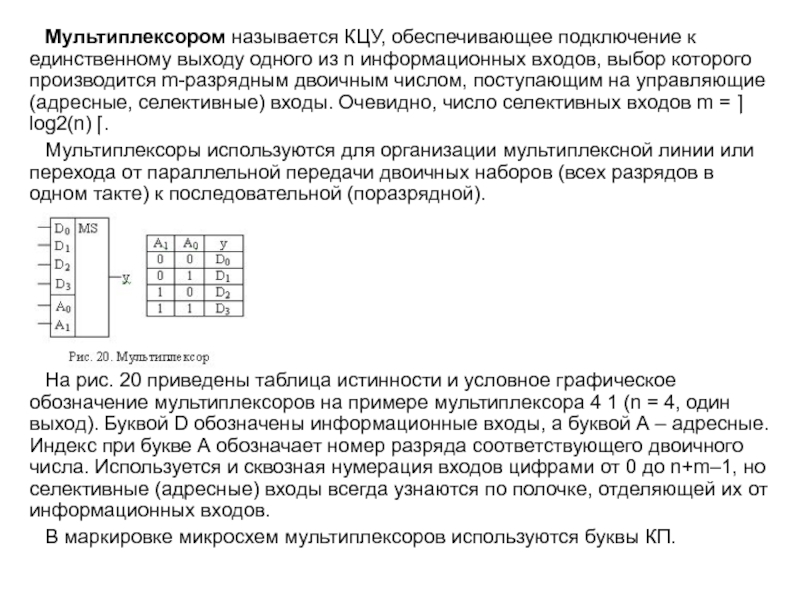

Слайд 24Мультиплексором называется КЦУ, обеспечивающее подключение к единственному выходу одного из

n информационных входов, выбор которого производится m-разрядным двоичным числом, поступающим

на управляющие (адресные, селективные) входы. Очевидно, число селективных входов m = log2(n) .

Мультиплексоры используются для организации мультиплексной линии или перехода от параллельной передачи двоичных наборов (всех разрядов в одном такте) к последовательной (поразрядной).

На рис. 20 приведены таблица истинности и условное графическое обозначение мультиплексоров на примере мультиплексора 4 1 (n = 4, один выход). Буквой D обозначены информационные входы, а буквой А – адресные. Индекс при букве А обозначает номер разряда соответствующего двоичного числа. Используется и сквозная нумерация входов цифрами от 0 до n+m–1, но селективные (адресные) входы всегда узнаются по полочке, отделяющей их от информационных входов.

В маркировке микросхем мультиплексоров используются буквы КП.

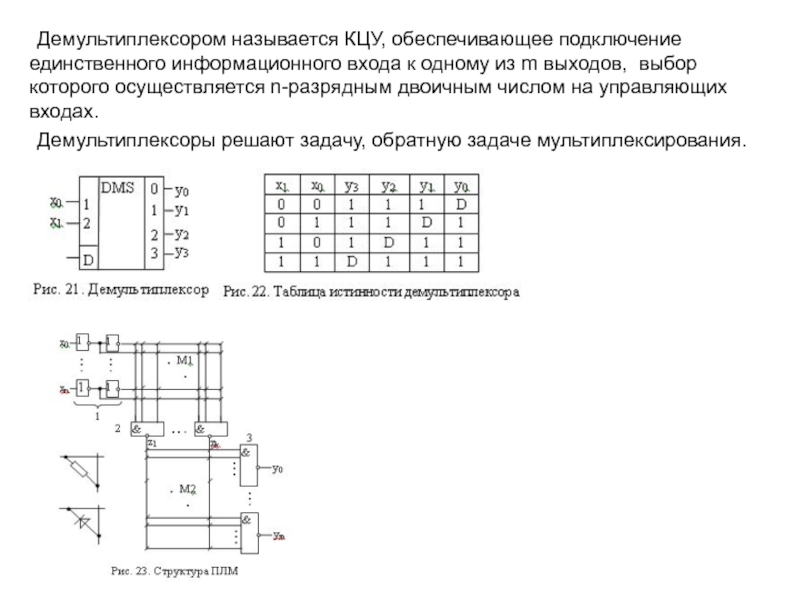

Слайд 25Демультиплексором называется КЦУ, обеспечивающее подключение единственного информационного входа к одному

из m выходов, выбор которого осуществляется n-разрядным двоичным числом на

управляющих входах.

Демультиплексоры решают задачу, обратную задаче мультиплексирования.

Слайд 26На рис. 21 приведено условное графическое обозначение демультиплексоров на примере

демультиплексора 1 4 (один информационный вход, m = 4). Управляющие

входы обозначаются весовыми коэффициентами двоичных разрядов, а для выходов используется сквозная нумерация.

Таблица истинности демультиплексоров, ограниченная демультиплексором рис. 21, показана на рис. 22. Из таблицы следует, что номер выхода, к которому подключается информационный вход D, является десятичным эквивалентом двоичного числа х1х0 на управляющих входах. Кроме того, нетрудно видеть, что в качестве демультиплексора вполне можно использовать дешифратор со стробированием, если считать стробирующий вход информационным, а информационные входы – управляющими. По этой причине в интегральном исполнении демультиплексоры не выпускаются, а дешифратор со стробированием называют дешифратором-демультиплексором, подчеркивая тем самым возможность выполнения им двух функций.

Преобразователями кода называются КЦУ, реализующие процедуру кодирования – изменение закона расположения нулей и единиц относительно исходных двоичных наборов.

В интегральном исполнении выпускаются только преобразователи двоичного кода в двоично-десятичный или семисегментный код, а также двоично-десятичного кода в двоичный. В маркировке таких микросхем используются буквы ПР, например, К155ПР6. Другие преобразователи кода либо синтезируются как КЦУ, либо реализуются на базе программируемой логической матрицы (ПЛМ).

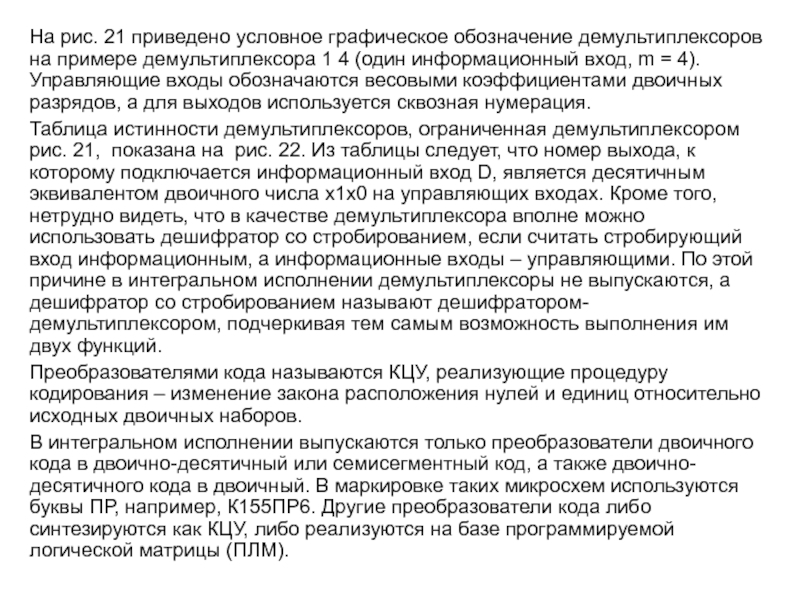

Слайд 27ПЛМ – это универсальная комбинационная схема, обеспечивающая преобразование входных n-разрядных

кодовых слов в m-разрядные кодовые слова на выходе. Структурно (рис.

23) ПЛМ состоит из трех уровней логических элементов и двух матриц соединительных линий М1 и М2.

В исходном состоянии во всех точках пересечения соединительных линий обеих матриц электрический контакт может быть либо обеспечен, либо отсутствовать. В первом случае место соединения выполняется в виде плавкой перемычки, а во втором – в виде р-n перехода. В соответствии с этим программирование ПЛМ заключается либо в разрушении определенных контактов путем пережигания плавкой перемычки, либо в их установлении путем пробоя р-n перехода.

Закон преобразования кодовых слов ПЛМ представленной структуры описывается системой ФАЛ, записанных в СДНФ: {yi = zj}, где zj – j-й член i-й функции. Соответственно с этим логические элементы первого уровня обеспечивают прямые и инверсные значения входных переменных, необходимые для формирования членов ФАЛ. Кроме того, второй ряд логических элементов этого уровня введен с целью обеспечения минимальной нагрузки для генератора исходного кода. Собственно члены ФАЛ zj формируются логическими элементами второго уровня совместно с матрицей М1. Элементы третьего уровня совместно с матрицей М2 обеспечивают необходимую структуру каждой из m ФАЛ.

Слайд 28

3. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ ЦИФРОВЫЕ УСТРОЙСТВА

3.1. Понятие и способ задания ПЦУ

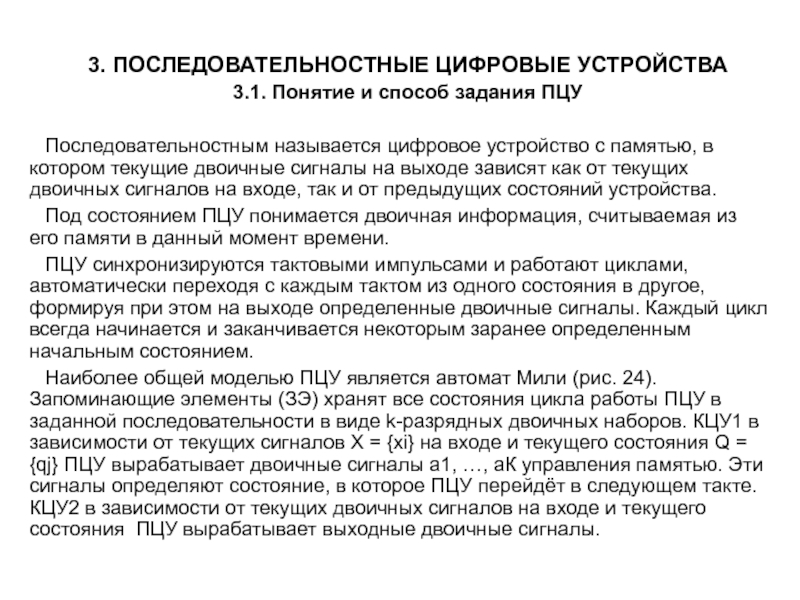

Последовательностным

называется цифровое устройство с памятью, в котором текущие двоичные сигналы

на выходе зависят как от текущих двоичных сигналов на входе, так и от предыдущих состояний устройства.

Под состоянием ПЦУ понимается двоичная информация, считываемая из его памяти в данный момент времени.

ПЦУ синхронизируются тактовыми импульсами и работают циклами, автоматически переходя с каждым тактом из одного состояния в другое, формируя при этом на выходе определенные двоичные сигналы. Каждый цикл всегда начинается и заканчивается некоторым заранее определенным начальным состоянием.

Наиболее общей моделью ПЦУ является автомат Мили (рис. 24). Запоминающие элементы (ЗЭ) хранят все состояния цикла работы ПЦУ в заданной последовательности в виде k-разрядных двоичных наборов. КЦУ1 в зависимости от текущих сигналов Х = {xi} на входе и текущего состояния Q = {qj} ПЦУ вырабатывает двоичные сигналы а1, …, аК управления памятью. Эти сигналы определяют состояние, в которое ПЦУ перейдёт в следующем такте. КЦУ2 в зависимости от текущих двоичных сигналов на входе и текущего состояния ПЦУ вырабатывает выходные двоичные сигналы.

Слайд 29Автомат Мили задаётся двумя системами логических функций: функций переходов Qt+1

= f(Xt, Qt) и функций выходов Yt = φ(Xt, Qt),

где индекс t соответствует текущему такту цикла, а (t+1) – последующему. Однако на практике часто оказывается достаточной более простая модель, в которой отсутствует связь КЦУ2 с входом ПЦУ. В этом случае функции выходов упрощаются: Yt = φ(Qt). Такая модель называется конечным автоматом Мура.

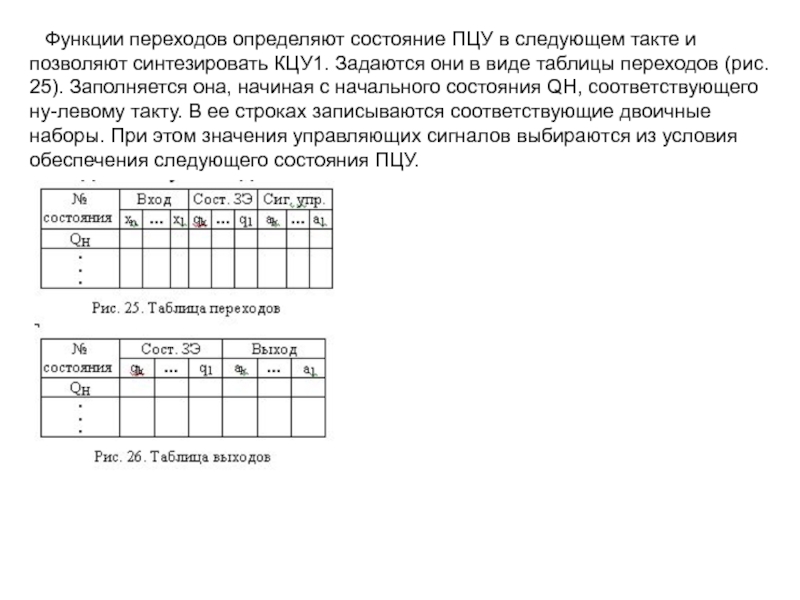

Слайд 30Функции переходов определяют состояние ПЦУ в следующем такте и позволяют

синтезировать КЦУ1. Задаются они в виде таблицы переходов (рис. 25).

Заполняется она, начиная с начального состояния QН, соответствующего ну-левому такту. В ее строках записываются соответствующие двоичные наборы. При этом значения управляющих сигналов выбираются из условия обеспечения следующего состояния ПЦУ.

Слайд 31Функции выходов определяют выходной двоичный набор в текущем такте и

позволяют синтезировать КЦУ2. Задаются они в виде таблицы выходов (рис.

26).

Обычно обе таблицы объединяются в одну, которая называется автоматной таблицей. Однако автоматная таблица не отражает динамику поведения ПЦУ. Поэтому для пояснения работы ПЦУ автоматную таблицу дополняют временными диаграммами.

3.2. Понятие и классификация триггеров

Основными компонентами ПЦУ являются запоминающие элементы, которые реализуются специальными устройствами – триггерами.

Триггер – это одноразрядный элемент памяти, предназначенный для хранения одного бита информации. Основной способ построения триггеров – использование обратных связей. Именно за счёт них обеспечивается возможность запоминания.

Любой триггер имеет два выхода – прямой и инверсный, но состояние триггера определяется сигналом на прямом выходе. Число входов в зависимости от типа триггера может составлять от двух до пяти.

По способу приема информации различают асинхронные и синхронные триггеры. Синхронные триггеры записывают бит информации только при наличии активного (разрешающего) сигнала на входе синхронизации. Пассивное значение синхросигнала определяет режим хранения триггера. Асинхронные триггеры не имеют входа синхронизации и записывают бит информации в момент его подачи на информационные входы.

Слайд 32Синхронные триггеры могут быть со статическим или динамическим управлением по

входу синхронизации. При статическом управлении активным является уровень логического 0

(инверсный синхровход) или логической 1 (прямой синхровход). На условном графическом обозначении триггера инверсный синхровход показывается кружочком , а прямой – без кружочка . При динамическом управлении активным является фронт или срез синхроимпульса. На условном графическом обозначении триггера фронт показывается прямой косой линией , а срез – обратной .

По функциональным возможностям различают триггеры с раздельной установкой состояний 0 и 1 (RS-триггер), с приёмом информации по одному входу D (D-триггер), универсальный с информационными входами J и K (JK-триггер) и со счётным входом Т (Т-триггер).

3.3. Типовые триггеры

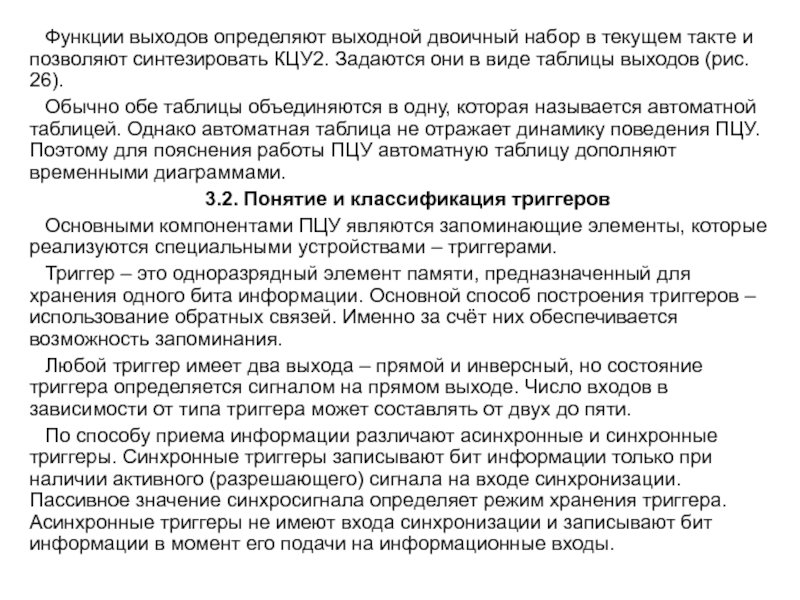

Асинхронные RS-триггеры имеют два информационных входа, один из которых обозначается буквой S (Set – установка), а другой – буквой R (Reset – сброс).

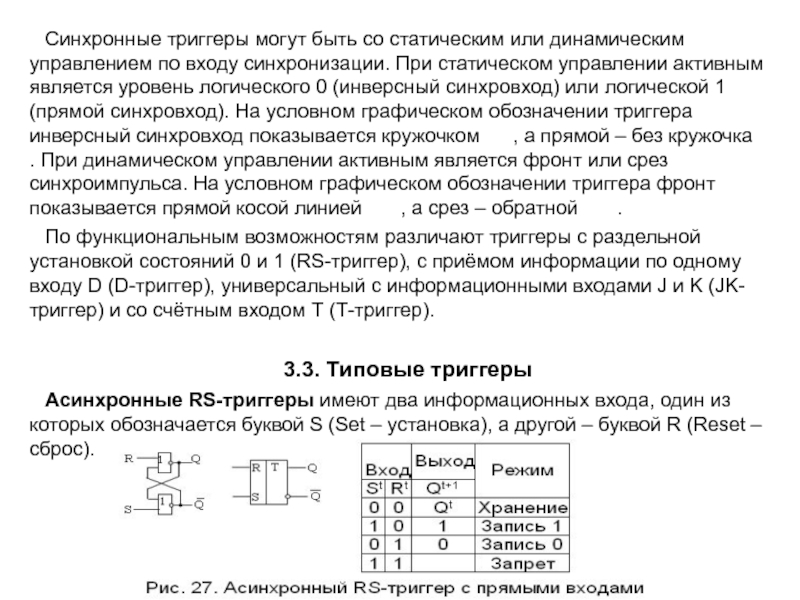

Слайд 33На рис. 27 приведены реализация триггера на ЛЭ ИЛИ-НЕ, его

условное графическое обозначение при исполнении в виде интегральной схемы и

таблица переходов. Как видно, активным значением информационного сигнала является 1. Поэтому RS-триггер, построенный на логических элементах ИЛИ-НЕ, называют RS-триггером с прямыми

входами. Однако асинхронный RS-триггер может быть построен и на логических элементах И-НЕ. Такая реализация триггера, ее условное графическое обозначение при исполнении в виде интегральной схемы и таблица переходов приведены на рис. 28. Здесь активным значением

информационного сигнала является 0. Поэтому RS- триггер, построенный на логических элементах И-НЕ, называют RS-триггером с инверсными входами.

Слайд 34Из таблиц переходов рис. 27 и 28 видно, что, во-первых,

активный сигнал на входе S приводит к установке триггера в

единичное состояние, а на входе R – в нулевое. По этой причине у триггеров любого другого типа асинхронный вход принудительной установки в 1 обозначается буквой S, а в 0 – буквой R. Эти входы являются входами первого приоритета, то есть при активном сигнале на одном из этих входов триггер не реагирует на сигналы по другим входам. Во-вторых, существует запрещенная комбинация входных сигналов. Запрет следует понимать только в информационном смысле. То есть он имеет смысл лишь при использовании триггера в качестве запоминающего элемента. Действительно, активные сигналы одновременно на S и R входах триггера устанавливают его выходы в одинаковое единичное состояние, что приводит к неопределенности относительно записываемого бита информации. Однако такая комбинация входных сигналов вполне естественна при использовании триггера в качестве управляющего элемента устройства.

В маркировке микросхем RS-триггеров используются буквы ТР.

Триггеры всех других типов выпускаются промышленностью как синхронные.

D-триггеры имеют один информационный вход D и вход синхронизации С. В интегральном исполнении D-триггеры выпускаются как со статическим, так и с динамическим управлением по входу С. В любом случае в маркировке микросхем D-триггеров используются буквы ТМ.

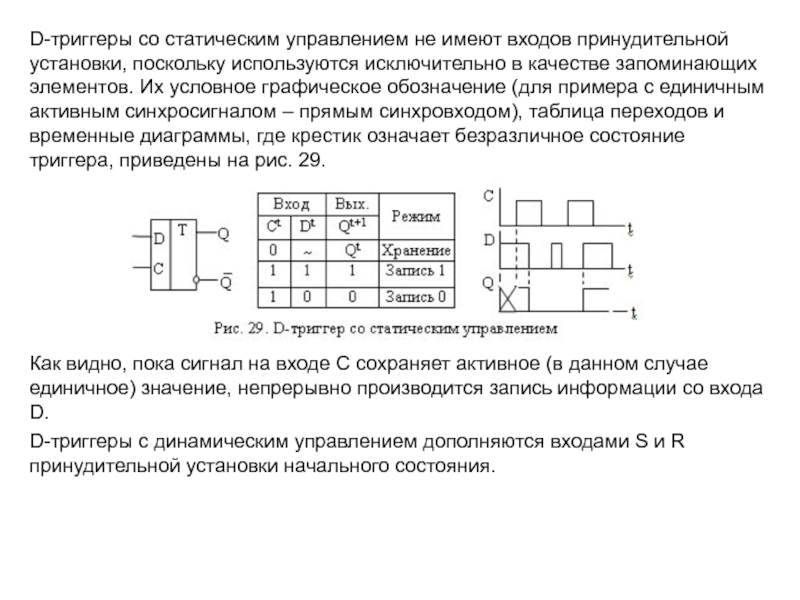

Слайд 35D-триггеры со статическим управлением не имеют входов принудительной установки, поскольку

используются исключительно в качестве запоминающих элементов. Их условное графическое обозначение

(для примера с единичным активным синхросигналом – прямым синхровходом), таблица переходов и временные диаграммы, где крестик означает безразличное состояние триггера, приведены на рис. 29.

Как видно, пока сигнал на входе С сохраняет активное (в данном случае единичное) значение, непрерывно производится запись информации со входа D.

D-триггеры с динамическим управлением дополняются входами S и R принудительной установки начального состояния.

Слайд 36 Их условное графическое обозначение (для примера с активным фронтом

синхросигнала), таблица переходов и временные диаграммы приведены на рис. 30.

Как видно, запись информации с входа D производится только по фронту синхросигнала (тактового импульса).

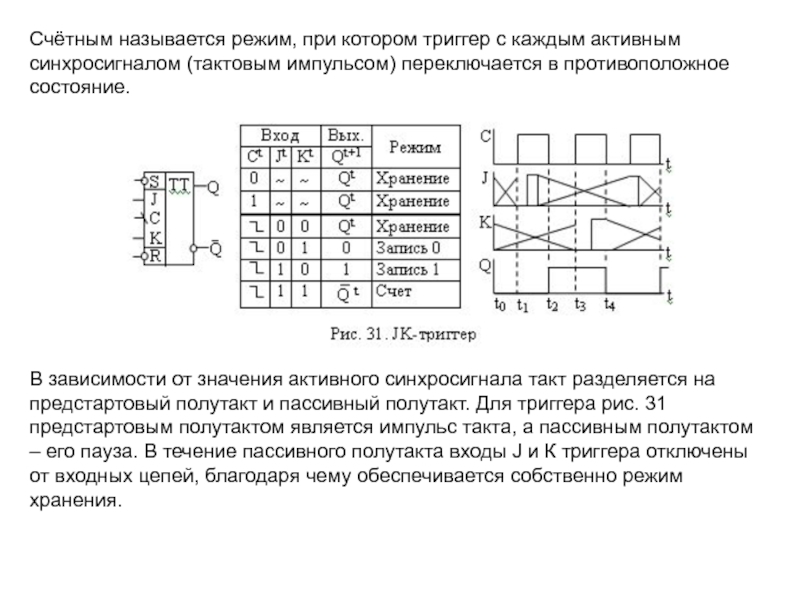

JК-триггеры имеют два информационных входа J и К, вход синхронизации С и входы R и S принудительной установки начального состояния. В интегральном исполнении выпускаются только с динамическим управлением по входу синхронизации. В маркировке микросхем JK-триггеров используются буквы ТВ.

Условное графическое обозначение (для примера с активным срезом синхросигнала), таблица переходов и временные диаграммы работы JК-триггера приведены на рис. 31.

Слайд 37Счётным называется режим, при котором триггер с каждым активным синхросигналом

(тактовым импульсом) переключается в противоположное состояние.

В зависимости от значения активного

синхросигнала такт разделяется на предстартовый полутакт и пассивный полутакт. Для триггера рис. 31 предстартовым полутактом является импульс такта, а пассивным полутактом – его пауза. В течение пассивного полутакта входы J и К триггера отключены от входных цепей, благодаря чему обеспечивается собственно режим хранения.

Слайд 38В течение предстартового полутакта к входным цепям подключается только тот

информационный вход, активный сигнал (для триггера рис. 31 – единица)

на котором может изменить текущее состояние триггера. Так, применительно к триггеру рис. 31, в интервале времени t1 – t2 будет подключен вход J, а в интервале времени t3 – t4 будет подключен вход К. Если в течение предстартового полутакта на подключенном информационном входе хоть на мгновение появляется активный сигнал, по активному синхросигналу триггер переключится в соответствующее состояние. В противном случае текущее состояние триггера не изменится.

Т-триггеры имеют единственный вход Т, на который поступают тактовые импульсы. По этой причине и поскольку Т-триггеры работают только в режиме счета, Т-вход называют счетным входом триггера.

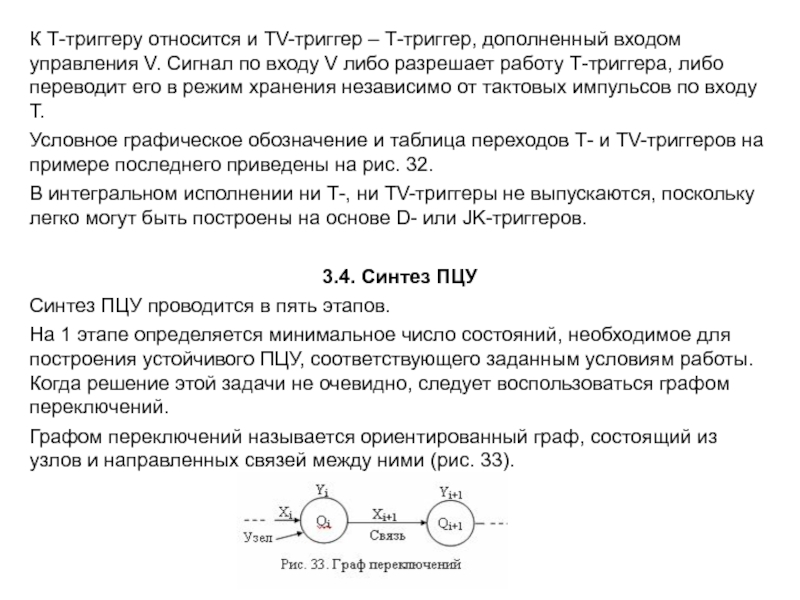

Слайд 39К Т-триггеру относится и TV-триггер – Т-триггер, дополненный входом управления

V. Сигнал по входу V либо разрешает работу Т-триггера, либо

переводит его в режим хранения независимо от тактовых импульсов по входу Т.

Условное графическое обозначение и таблица переходов Т- и TV-триггеров на примере последнего приведены на рис. 32.

В интегральном исполнении ни Т-, ни TV-триггеры не выпускаются, поскольку легко могут быть построены на основе D- или JK-триггеров.

3.4. Синтез ПЦУ

Синтез ПЦУ проводится в пять этапов.

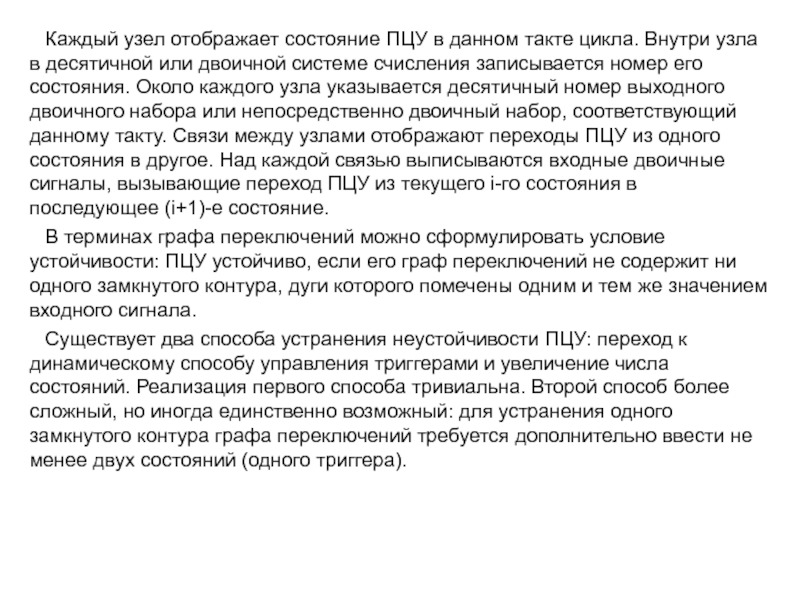

На 1 этапе определяется минимальное число состояний, необходимое для построения устойчивого ПЦУ, соответствующего заданным условиям работы. Когда решение этой задачи не очевидно, следует воспользоваться графом переключений.

Графом переключений называется ориентированный граф, состоящий из узлов и направленных связей между ними (рис. 33).

Слайд 40Каждый узел отображает состояние ПЦУ в данном такте цикла. Внутри

узла в десятичной или двоичной системе счисления записывается номер его

состояния. Около каждого узла указывается десятичный номер выходного двоичного набора или непосредственно двоичный набор, соответствующий данному такту. Связи между узлами отображают переходы ПЦУ из одного состояния в другое. Над каждой связью выписываются входные двоичные сигналы, вызывающие переход ПЦУ из текущего i-го состояния в последующее (i+1)-е состояние.

В терминах графа переключений можно сформулировать условие устойчивости: ПЦУ устойчиво, если его граф переключений не содержит ни одного замкнутого контура, дуги которого помечены одним и тем же значением входного сигнала.

Существует два способа устранения неустойчивости ПЦУ: переход к динамическому способу управления триггерами и увеличение числа состояний. Реализация первого способа тривиальна. Второй способ более сложный, но иногда единственно возможный: для устранения одного замкнутого контура графа переключений требуется дополнительно ввести не менее двух состояний (одного триггера).

Слайд 41На 2 этапе определяется количество триггеров и выбирается их тип.

Количество триггеров ПЦУ определяется выражением: NT = Log2NC ,

где NC – число состояний автомата, включая начальное.

Тип триггеров выбирается по принципу наибольшего совпадения их правил работы с правилами работы проектируемого устройства.

На 3 этапе определяются функции переходов и проводится синтез КЦУ1.

Функции переходов представляются таблицей переходов, где управляющие сигналы записываются на основе правил работы выбранных триггеров, состояния запоминающих элементов – в соответствии с принятым порядком их следования, а входные двоичные наборы – в соответствии с правилами работы проектируемого устройства. Полученная таблица рассматривается как таблица истинности КЦУ1, что позволяет воспользоваться стандартной методикой его синтеза.

На 4 этапе определяются функции выходов и проводится синтез КЦУ2.

Функции выходов представляются таблицей выходов, где управляющие сигналы записываются, как и в таблице переходов, а выходные двоичные наборы – в соответствии с правилами работы проектируемого устройства. Построение таблицы выходов основывается на графе переключений. Полученная таблица рассматривается как таблица истинности КЦУ2, что позволяет воспользоваться стандартной методикой его синтеза.

Слайд 42На 5 этапе строится структурная схема ПЦУ. При этом входы

синхронизации триггеров соединяются параллельно (объединяются) на общий вход синхронизации ПЦУ,

называемый тактовым входом устройства. В случае обнаружения в структурной схеме типовых структур производится коррекция схемы путем использования условных графических обозначений этих структур.

Наиболее часто используемые ПЦУ – счетчики и регистры, относятся к категории типовых устройств.

3.5. Двоичные счетчики

Двоичным счётчиком называется ПЦУ, которое подсчитывает число поступающих на его вход тактовых импульсов и выдает результат в виде двоичного числа.

Основным информационным параметром счётчиков является модуль счёта (коэффициент пересчёта). Модуль счёта КС определяет максимальное число тактовых импульсов, которое может быть сосчитано счётчиком. Таким образом, максимальный модуль счета n-разрядного двоичного счётчика равен 2n.

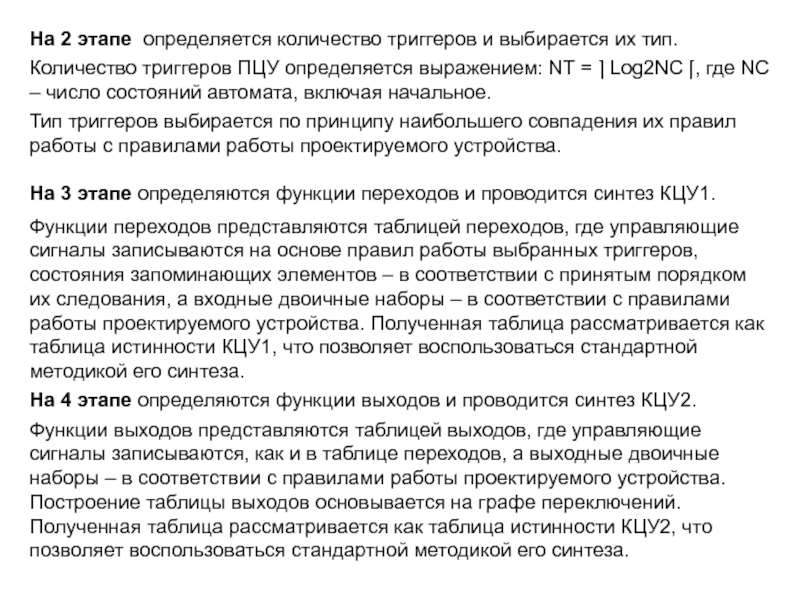

В процессе счёта тактовых импульсов t1, t2, t3, … счётчик последовательно проходит КС состояний, включая начальное состояние QН (рис. 34).

Слайд 43При этом на выходе счётчика формируется последовательность двоичных чисел YH,

Y1, Y2 …, в которой каждое последующее число отличается от

предыдущего на 1. КС-м тактовым импульсом счётчик возвращается в начальное состояние (говорят, переполняется), после чего цикл счёта повторяется.

Базовыми элементами любого счётчика являются Т- и ТV-триггеры, которые аппаратно могут быть реализованы на D- или JK-триггерах.

По направлению счёта различают суммирующие, вычитающие и реверсивные счётчики. Любой из них в зависимости от способа организации цепей синхронизации может быть асинхронным или синхронным.

Суммирующие счётчики с каждым тактом увеличивают свое состояние на 1. Стандартным начальным состоянием считается нулевое состояние счетчика.

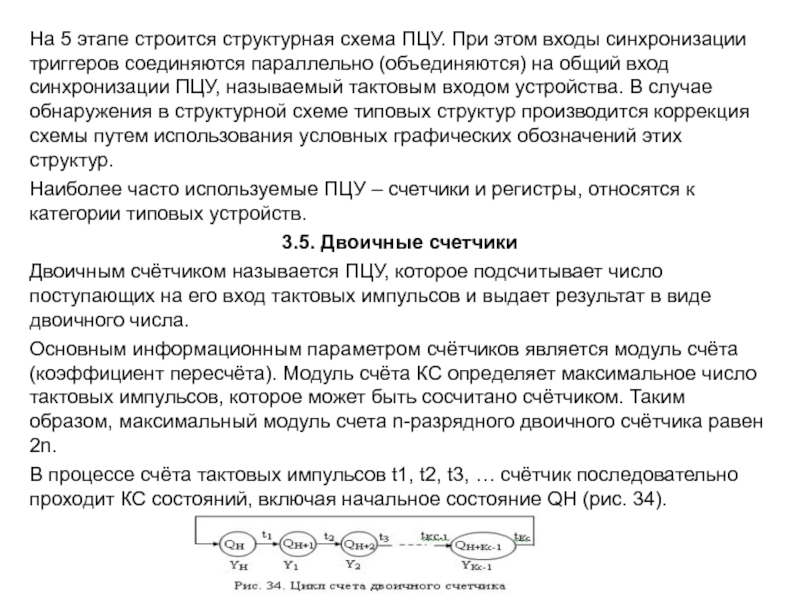

Асинхронный счетчик строится путем соединения выхода предыдущего триггера со счетным входом последующего (рис. 35). На рис. 35 приведены также временные диаграммы, иллюстрирующие динамику работы счетчика при стандартном начальном состоянии.

Слайд 44По фронту первого тактового импульса младший триггер переходит в единичное

состояние, формируя на инверсном выходе перепад напряжения из 1 в

0. Поскольку этот перепад пассивен для данного типа триггеров, второй триггер сохраняет предыдущее нулевое состояние. В результате на выходе счетчика образуется двоичное число 01 (110). Фронт второго тактового импульса возвращает младший триггер в нулевое состояние. При этом на его инверсном выходе формируется перепад напряжения из 0 в 1, который переключает второй триггер в единичное состояние. В результате на выходе счетчика образуется двоичное число 10 (210). Фронт третьего тактового импульса переводит счетчик в третье состояние – на выходе двоичное число 11 (310). Четвертым тактовым импульсом счетчик переполняется, то есть возвращается в нулевое (начальное) состояние, после чего процесс счета повторяется.

На основе проведенного анализа можно сформулировать схемотехнические принципы работы суммирующего счетчика:

для любого суммирующего счетчика переключение i-го триггера возможно, только если все предыдущие триггеры находятся в состоянии единицы;

в асинхронном счетчике каждый последующий триггер может переключиться только после переключения предыдущего.

Из последнего пункта следует, что каждое двоичное число на выходе асинхронного счетчика формируется во времени последовательно разряд за разрядом, начиная с младшего.

Слайд 45Этот процесс эквивалентен распространению переноса при арифметическом сложении двоичного числа

с единицей. Поэтому счетчики, у которых сигнал управления переключением триггеров

распространяется последовательно, называются счетчиками с последовательным переносом.

Очевидно, что наибольшее время, в течение которого на выходе асинхронного счетчика установится очередной результат равно

n , где – среднее время задержки переключения триггера по счетному входу, а n – число разрядов (триггеров) счетчика.

Наибольшее время между изменением сигнала на входе и завершением образования соответствующего сигнала на выходе называется быстродействием цифрового устройства. В частности, быстродействие счетчиков характеризуется наибольшей допустимой частотой следования тактовых импульсов, которая для асинхронного счетчика определяется отношением 1/(n ) Гц.

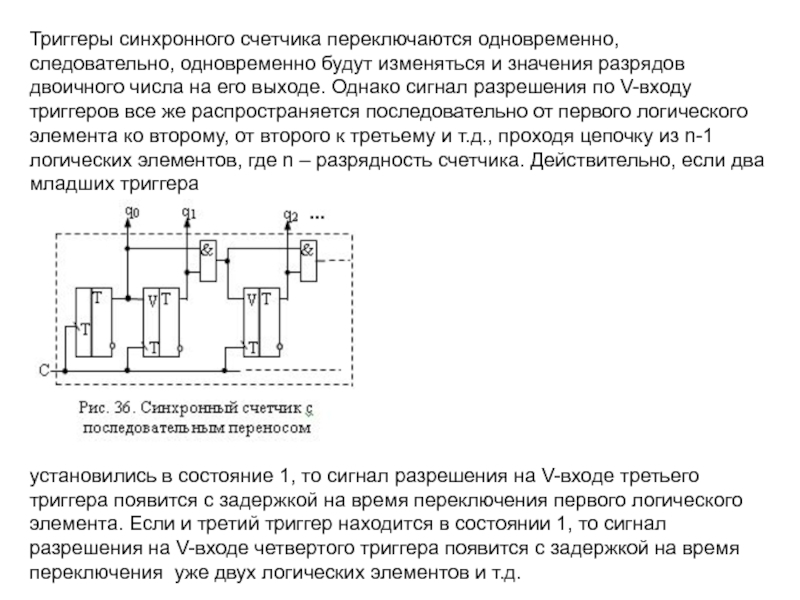

Синхронные счетчики отличаются от асинхронных параллельным соединением счетных входов всех триггеров (рис. 36). Логические элементы обеспечивают выполнение первого пункта схемотехнических принципов работы суммирующего счетчика.

Слайд 46Триггеры синхронного счетчика переключаются одновременно, следовательно, одновременно будут изменяться и

значения разрядов двоичного числа на его выходе. Однако сигнал разрешения

по V-входу триггеров все же распространяется последовательно от первого логического элемента ко второму, от второго к третьему и т.д., проходя цепочку из n-1 логических элементов, где n – разрядность счетчика. Действительно, если два младших триггера

установились в состояние 1, то сигнал разрешения на V-входе третьего триггера появится с задержкой на время переключения первого логического элемента. Если и третий триггер находится в состоянии 1, то сигнал разрешения на V-входе четвертого триггера появится с задержкой на время переключения уже двух логических элементов и т.д.

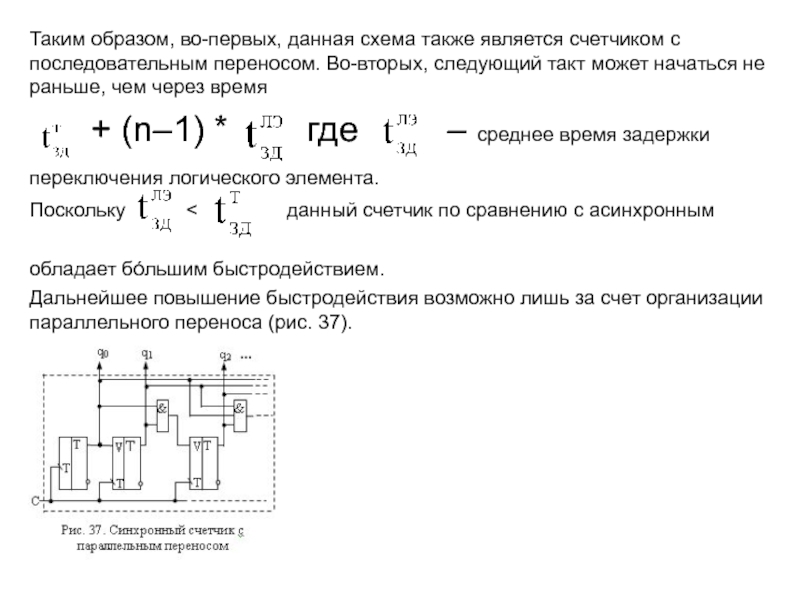

Слайд 47Таким образом, во-первых, данная схема также является счетчиком с последовательным

переносом. Во-вторых, следующий такт может начаться не раньше, чем через

время

+ (n–1) * где – среднее время задержки переключения логического элемента.

Поскольку < данный счетчик по сравнению с асинхронным

обладает бóльшим быстродействием.

Дальнейшее повышение быстродействия возможно лишь за счет организации параллельного переноса (рис. 37).

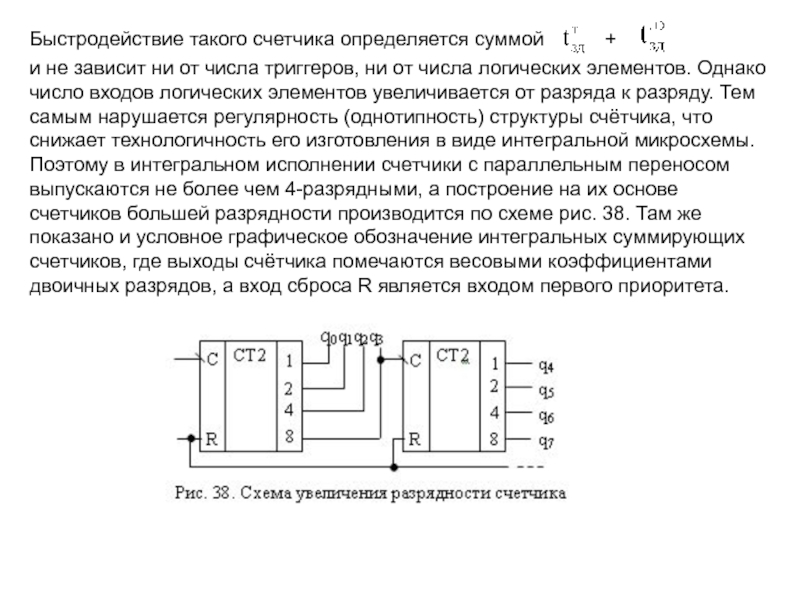

Слайд 48Быстродействие такого счетчика определяется суммой

+

и не зависит ни от числа триггеров, ни от

числа логических элементов. Однако число входов логических элементов увеличивается от разряда к разряду. Тем самым нарушается регулярность (однотипность) структуры счётчика, что снижает технологичность его изготовления в виде интегральной микросхемы. Поэтому в интегральном исполнении счетчики с параллельным переносом выпускаются не более чем 4-разрядными, а построение на их основе счетчиков большей разрядности производится по схеме рис. 38. Там же показано и условное графическое обозначение интегральных суммирующих счетчиков, где выходы счётчика помечаются весовыми коэффициентами двоичных разрядов, а вход сброса R является входом первого приоритета.

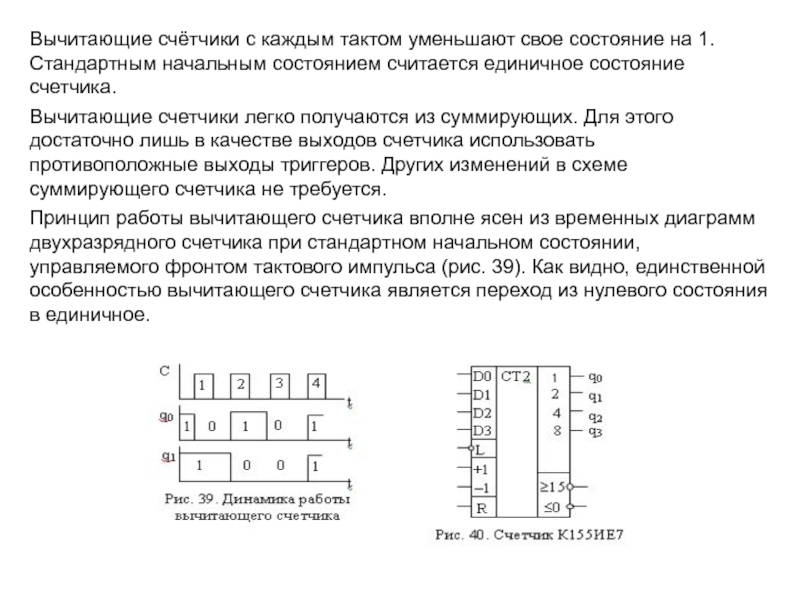

Слайд 49Вычитающие счётчики с каждым тактом уменьшают свое состояние на 1.

Стандартным начальным состоянием считается единичное состояние счетчика.

Вычитающие счетчики легко получаются

из суммирующих. Для этого достаточно лишь в качестве выходов счетчика использовать противоположные выходы триггеров. Других изменений в схеме суммирующего счетчика не требуется.

Принцип работы вычитающего счетчика вполне ясен из временных диаграмм двухразрядного счетчика при стандартном начальном состоянии, управляемого фронтом тактового импульса (рис. 39). Как видно, единственной особенностью вычитающего счетчика является переход из нулевого состояния в единичное.

Слайд 50Реверсивные счётчики обладают возможностями суммирующего и вычитающего счётчиков.

Условное графическое

обозначение интегральных реверсивных счетчиков показано на примере микросхемы К155ИЕ7 (рис.

40). Режим суммирования задаётся подачей тактовых импульсов на вход +1, а режим вычитания – на вход -1. Вход L предназначен для предварительной установки счетчика в заданное состояние. Активный сигнал на этом входе блокирует счетные входы 1 и двоичное число с входов D переписывается на выход. Таким образом, вход L является входом второго приоритета. На выходе переноса 15 активный сигнал появляется при единичном состоянии счётчика, а на выходе займа 0 – при нулевом. Эти выходы обычно используются для построения многоразрядного реверсивного счётчика. При этом выходы 15 и 0 предыдущей микросхемы (счетчика младших разрядов) соединяются, соответственно, с входами +1 и -1 последующей микросхемы (счётчика старших разрядов).

В интегральном исполнении выпускаются суммирующие счетчики – асинхронные и синхронные с параллельным переносом, а также реверсивные счетчики.-- В маркировке микросхем счетчиков используются буквы ИЕ.

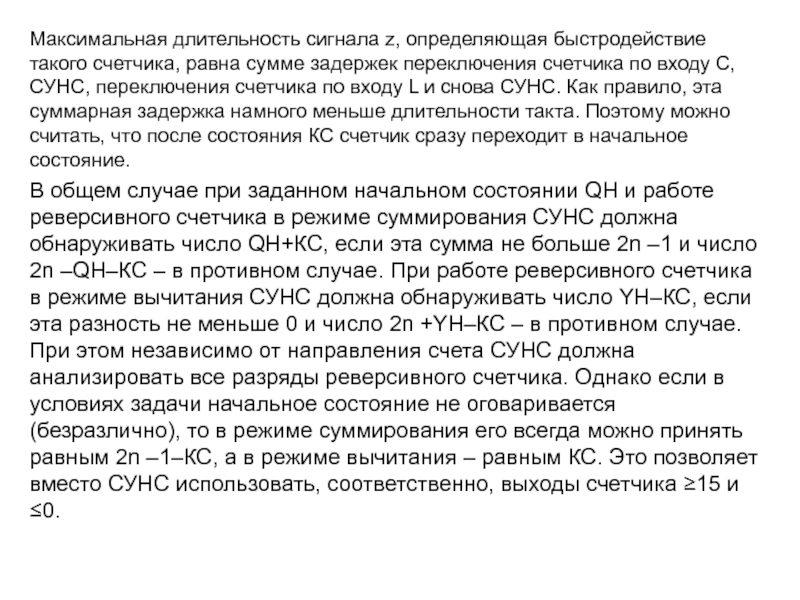

Слайд 513.6. Счетчики с произвольным модулем счета

Строятся на базе двоичных счётчиков

с модулем счета, не меньшим требуемого. Минимально необходимая разрядность базового

счетчика определяется по формуле n = Log2(КС) .

Принцип работы таких счетчиков заключается в принудительном прерывании последовательности состояний базового счетчика, исключая "лишние" старшие (суммирующий счетчик) или младшие (вычитающий счетчик) его состояния.

Счетчик по модулю КС при нестандартных начальных состояниях удобно строить на основе реверсивного счетчика. Одна из возможных таких реализаций показана на рис. 41. Как только счётчик переходит в состояние КС+1 (здесь 0), схема установки начального состояния (СУНС) вырабатывает сигнал z, принудительно устанавливающий счетчик в начальное состояние (здесь 3). После этого цикл счета повторяется.

Слайд 52Максимальная длительность сигнала z, определяющая быстродействие такого счетчика, равна сумме

задержек переключения счетчика по входу С, СУНС, переключения счетчика по

входу L и снова СУНС. Как правило, эта суммарная задержка намного меньше длительности такта. Поэтому можно считать, что после состояния КС счетчик сразу переходит в начальное состояние.

В общем случае при заданном начальном состоянии QH и работе реверсивного счетчика в режиме суммирования СУНС должна обнаруживать число QH+КС, если эта сумма не больше 2n –1 и число 2n –QH–КС – в противном случае. При работе реверсивного счетчика в режиме вычитания СУНС должна обнаруживать число YH–КС, если эта разность не меньше 0 и число 2n +YH–КС – в противном случае. При этом независимо от направления счета СУНС должна анализировать все разряды реверсивного счетчика. Однако если в условиях задачи начальное состояние не оговаривается (безразлично), то в режиме суммирования его всегда можно принять равным 2n –1–КС, а в режиме вычитания – равным КС. Это позволяет вместо СУНС использовать, соответственно, выходы счетчика 15 и 0.

Слайд 53В случае использования счетчиков, допускающих только стандартные начальные состояния, СУНС

по-прежнему необходима, но ее схема существенно упрощается. Действительно, в случае

суммирующего счетчика стандартным является нулевое начальное состояние. Следовательно, каждое последующее состояние всегда больше предыдущего, то есть в двоичном отображении отличается от предыдущего большим числом единичных позиций и/или смещением старшей единицы влево. Но тогда достаточно анализировать только те выходы суммирующего счетчика, которые соответствуют единичным разрядам числа КС. В результате в зависимости от значения активного сигнала по входу R счетчика СУНС представляет собой ЛЭ И либо И-НЕ. Аналогично, в случае вычитающего счетчика и стандартного начального состояния (2n –1) достаточно анализировать только те выходы счетчика, которые соответствуют нулевым позициям числа 2n –КС. В результате в зависимости от значения активного сигнала по входу S счетчика СУНС представляет собой ЛЭ ИЛИ либо ИЛИ-НЕ.

Слайд 543.7. Регистры

Регистром называется ПЦУ, предназначенное для хранения двоичных наборов и

выполнения над ними таких логических операций как преобразование последовательного способа

представления к параллельному и обратно, сдвиг влево или вправо на требуемое число разрядов и поразрядное инвертирование.

По назначению различают регистры хранения и сдвига.

Регистры хранения (буферные регистры) могут быть реализованы на триггерах, как со статическим, так и с динамическим управлением.

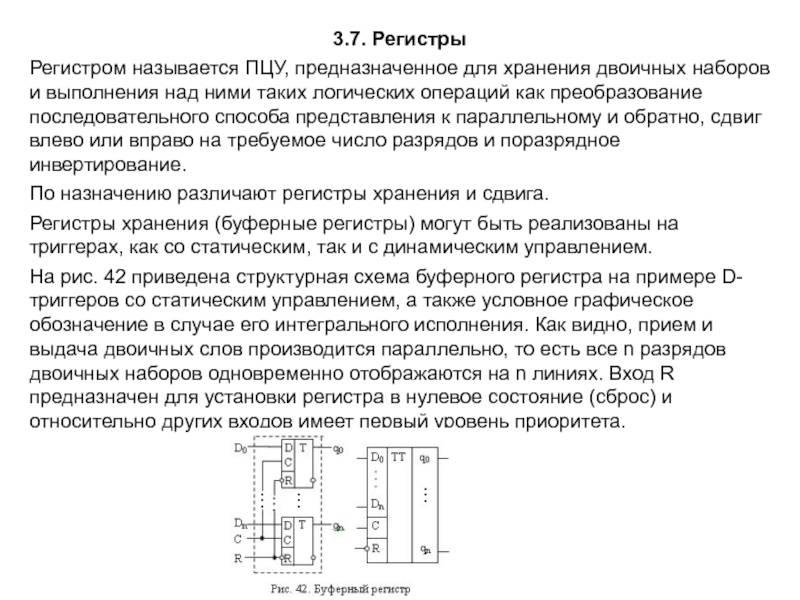

На рис. 42 приведена структурная схема буферного регистра на примере D-триггеров со статическим управлением, а также условное графическое обозначение в случае его интегрального исполнения. Как видно, прием и выдача двоичных слов производится параллельно, то есть все n разрядов двоичных наборов одновременно отображаются на n линиях. Вход R предназначен для установки регистра в нулевое состояние (сброс) и относительно других входов имеет первый уровень приоритета.

Слайд 55Буферные регистры выпускаются в интегральном исполнении. В маркировке микросхем используются

буквы ТМ.

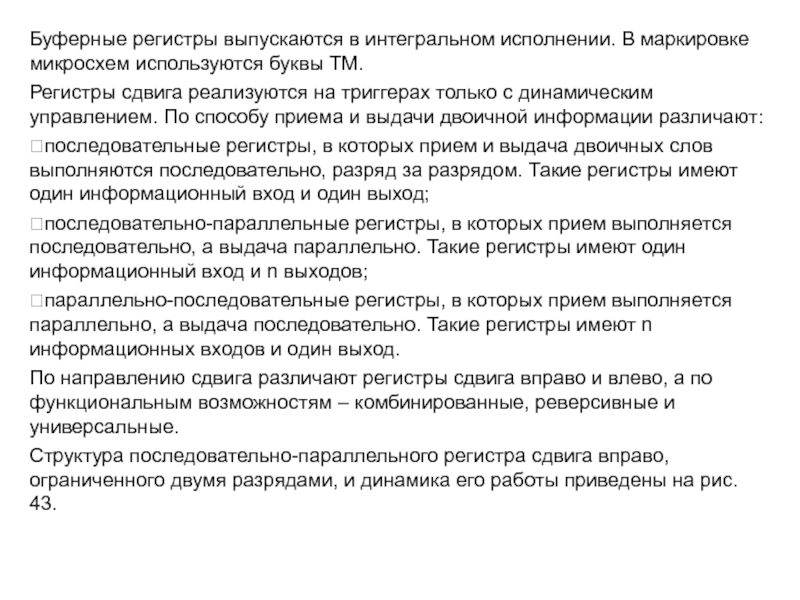

Регистры сдвига реализуются на триггерах только с динамическим управлением.

По способу приема и выдачи двоичной информации различают:

последовательные регистры, в которых прием и выдача двоичных слов выполняются последовательно, разряд за разрядом. Такие регистры имеют один информационный вход и один выход;

последовательно-параллельные регистры, в которых прием выполняется последовательно, а выдача параллельно. Такие регистры имеют один информационный вход и n выходов;

параллельно-последовательные регистры, в которых прием выполняется параллельно, а выдача последовательно. Такие регистры имеют n информационных входов и один выход.

По направлению сдвига различают регистры сдвига вправо и влево, а по функциональным возможностям – комбинированные, реверсивные и универсальные.

Структура последовательно-параллельного регистра сдвига вправо, ограниченного двумя разрядами, и динамика его работы приведены на рис. 43.

Слайд 56Заполняется такой регистр последовательно, начиная с триггера старшего разряда. Следовательно,

двоичный набор вводится, начиная с младшего разряда. При этом очередной

разряд набора выставляется на информационный вход регистра заблаговременно, устраняя тем самым возможность повторного ввода одного и того же разряда.

Общий принцип работы регистра сдвига вправо: в каждом такте каждый последующий триггер передает свое состояние предыдущему, а в освободившийся триггер старшего разряда записывается очередной разряд вводимого двоичного набора.

Последовательно-параллельный регистр сдвига влево отличается от предыдущего тем, что информационным входом является вход триггера младшего разряда. Следовательно, двоичное число вводится поразрядно, начиная со старшего разряда.

Слайд 57Общий принцип работы регистра сдвига вправо: в каждом такте каждый

предыдущий триггер передает свое состояние последующему, а в освободившийся триггер

младшего разряда записывается очередной разряд вводимого двоичного набора.

Для полного заполнения n-разрядного последовательного или последовательно-параллельного регистра требуется n тактов.

Условные графические обозначения интегральных последовательно-параллельных регистров сдвига приведены на рис. 44, где сплошная стрелка указывает направление сдвига, а пунктирной стрелкой обозначен порядок заполнения регистра.

Слайд 58Комбинированные регистры сочетают возможности параллельного регистра и регистра сдвига влево

или вправо.

Реверсивные регистры допускают сдвиг как влево, так и вправо.

Универсальные

регистры совмещают возможности параллельного и реверсивного регистров. Их условное графическое обозначение приведено на рис. 45, где DR – информационный вход в режиме сдвига вправо; DL – информационный вход в режиме сдвига влево; S1, S0 – входы выбора режима работы регистра; D0…D7 – информационные входы в режиме параллельного ввода двоичного слова (буферного регистра); R – вход сброса регистра в нулевое состояние; С – тактовый вход.

Слайд 59В интегральном исполнении выпускаются только комбинированные и универсальные регистры. В

маркировке микросхем регистров используются буквы ИР.

3.8. Основные типы сдвигов

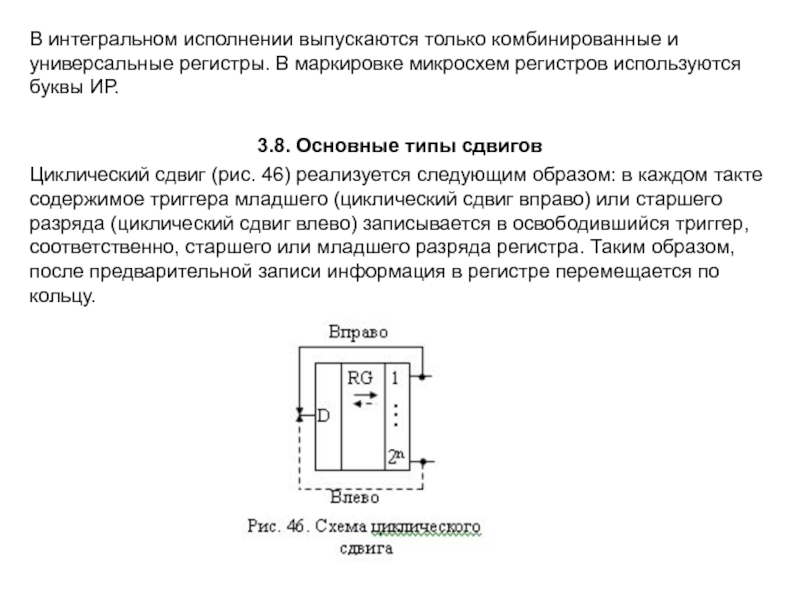

Циклический сдвиг

(рис. 46) реализуется следующим образом: в каждом такте содержимое триггера младшего (циклический сдвиг вправо) или старшего разряда (циклический сдвиг влево) записывается в освободившийся триггер, соответственно, старшего или младшего разряда регистра. Таким образом, после предварительной записи информация в регистре перемещается по кольцу.

Слайд 60Логический сдвиг является обычным сдвигом с той лишь особенностью, что

в освободившийся входной триггер всегда записывается логический ноль.

Свойства логического сдвига:

логический

сдвиг вправо на один разряд соответствует арифметической операции деления на 2 с округлением в меньшую сторону;

логический сдвиг влево на один разряд соответствует арифметической операции умножения на 2.

4. ПОЛУПРОВОДНИКОВЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

4.1. Классификация и основные характеристики ЗУ

Запоминающие устройства (ЗУ) разделяются на оперативные (ОЗУ) и постоянные (ПЗУ).

ОЗУ предназначены для сравнительно кратковременного хранения информации. При отключении напряжения питания информация в них разрушается. По способу хранения информации в запоминающем элементе различают:

-статические ОЗУ (RAM), в которых запоминающими элементами являются асинхронные RS-триггеры;

-динамические ОЗУ (RAMD), в которых хранение информации осуществляется за счёт заряда емкостей, сформированных в структуре полупроводника.

Слайд 61ПЗУ предназначены для длительного хранения информации, которая сохраняется и при

отсутствии напряжения питания. ПЗУ разделяются на три группы:

-масочные ПЗУ (ROM),

в которые информация записывается однократно в процессе изготовления;

-однократно-программируемые (PROM), в которые информация записывается также однократно, но пользователем;

-перепрограммируемые (ППЗУ), допускающие возможность стирания и повторной записи информации. ППЗУ, в которых стирание информации обеспечивается электрическим путём, обозначаются как EEPROM, а ультрафиолетовым облучением – как EPROM.

Все типы ЗУ изготовляются в виде интегральных микросхем. При этом в маркировке микросхем ОЗУ используются буквы РУ, микросхем ПЗУ типа ROM используются буквы РЕ, типа PROM – буквы РТ, типа EPROM – буквы РФ и типа EEPROM – буквы РР.

Выходные цепи ОЗУ организуются с тремя состояниями, а ПЗУ – как с тремя состояниями, так и с открытым коллектором.

Слайд 62К важнейшим характеристикам ЗУ относятся:

1. Общая ёмкость С = Nm,

определяемая числом хранимых слов N и их разрядностью m. Измеряется

в битах, байтах, килобитах и т.д.

Для хранения одноразрядного слова (одного бита) в ЗУ отводится запоминающий элемент, а m-разрядных слов – ячейки памяти, каждая из которых представляет собой совокупность m запоминающих элементов.

2. Быстродействие характеризуется временем обращения к ЗУ, которое определяется с момента начала записи или чтения информации до момента их завершения, включая и подготовку ЗУ к следующему обращению. Соответствие между сигналами управления и режимами работы ЗУ задается в виде таблицы.

Среди других временных параметров приводятся минимально допустимые длительность импульсов и пауз и величины временных сдвигов между сигналами на различных входах ЗУ. Эти параметры необходимы для обеспечения устойчивой работы микросхем ЗУ.

3. Напряжение питания, напряжения и токи сигналов в различных режимах работы ЗУ, потребляемая мощность.

Слайд 634.2. Организация накопителя ЗУ

Накопитель является основной частью ЗУ. Состоит он

из отдельных запоминающих элементов, число которых равно общему числу бит

хранимой информации. Каждый запоминающий элемент (ЗЭ) имеет определённый номер (адрес), который должен быть указан при каждом обращении к ЗУ. Таким образом, в полупроводниковых ЗУ используется адресный принцип хранения информации.

К накопителю запоминающий элемент подключается с помощью адресных и разрядных линий (проводников). Адресные линии используются для активизации одного запоминающего элемента или их совокупности с целью чтения либо записи. По разрядным линиям передается записываемая или считываемая информация.

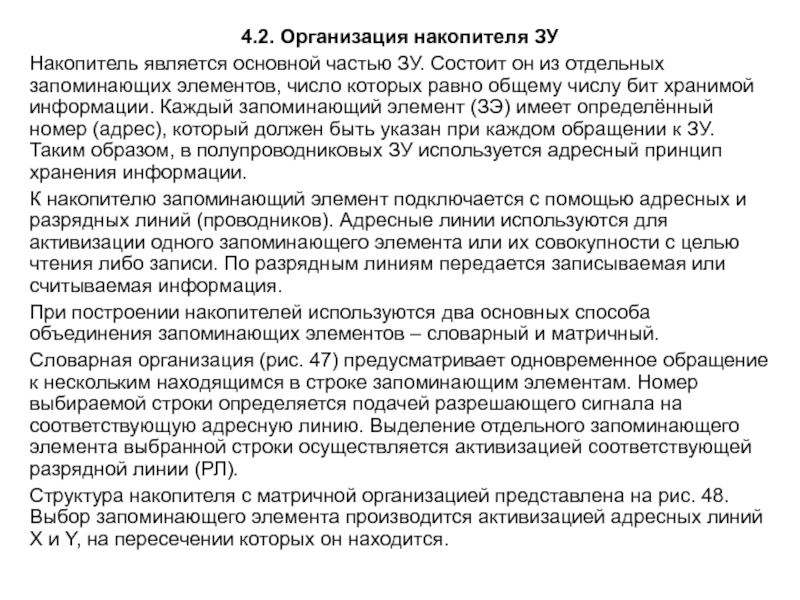

При построении накопителей используются два основных способа объединения запоминающих элементов – словарный и матричный.

Словарная организация (рис. 47) предусматривает одновременное обращение к нескольким находящимся в строке запоминающим элементам. Номер выбираемой строки определяется подачей разрешающего сигнала на соответствующую адресную линию. Выделение отдельного запоминающего элемента выбранной строки осуществляется активизацией соответствующей разрядной линии (РЛ).

Структура накопителя с матричной организацией представлена на рис. 48. Выбор запоминающего элемента производится активизацией адресных линий X и Y, на пересечении которых он находится.

Слайд 64

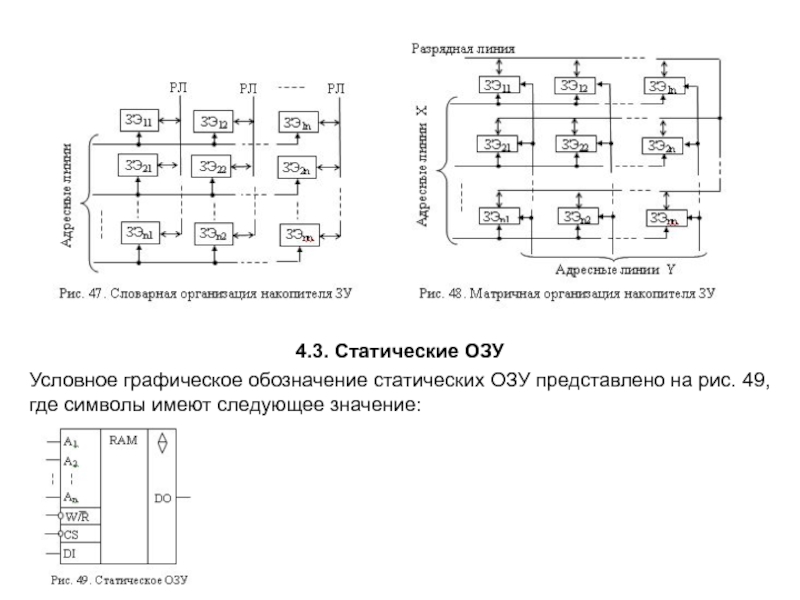

4.3. Статические ОЗУ

Условное графическое обозначение статических ОЗУ представлено на рис.

49, где символы имеют следующее значение:

Слайд 65А – адресные входы, используемые для выбора запоминающего элемента накопителя;

W/

– вход выбора режима (write/ read

– запись/чтение);

CS – вход выбора кристалла (аналогичен входу стробирования КЦУ);

DI – информационный вход (input);

DO – выход (output).

Накопитель статических ОЗУ имеет матричную структуру, поэтому одна половина адресной шины А определяет номер строки, а другая – номер столбца накопителя.

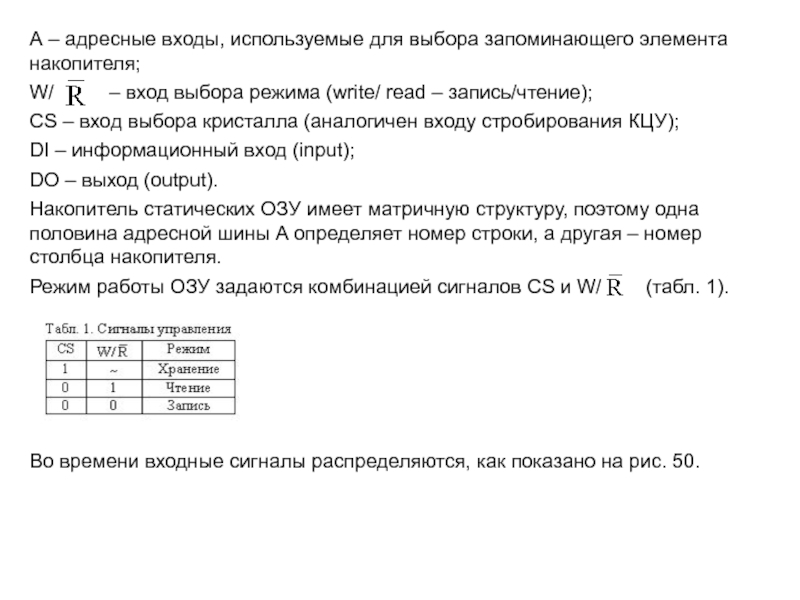

Режим работы ОЗУ задаются комбинацией сигналов CS и W/ (табл. 1).

Во времени входные сигналы распределяются, как показано на рис. 50.

Слайд 66

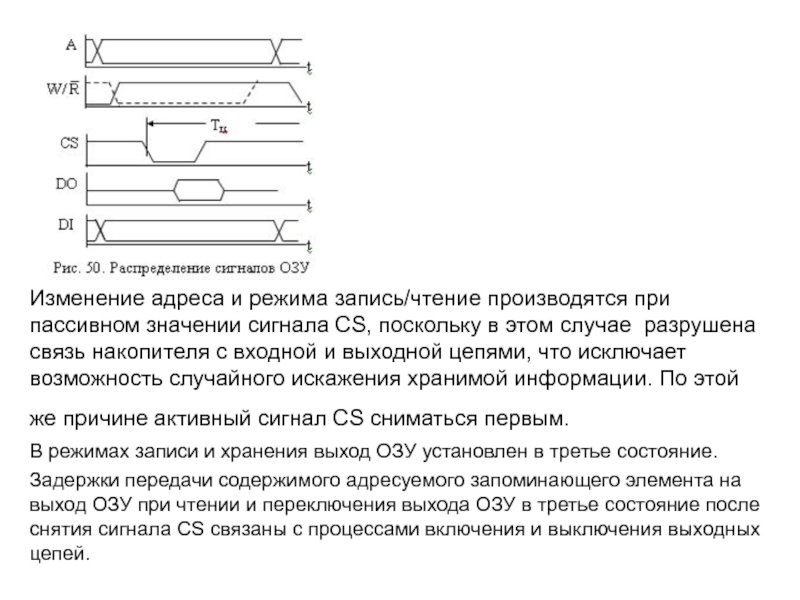

Изменение адреса и режима запись/чтение производятся при пассивном значении сигнала

CS, поскольку в этом случае разрушена связь накопителя с входной

и выходной цепями, что исключает возможность случайного искажения хранимой информации. По этой же причине активный сигнал CS сниматься первым.

В режимах записи и хранения выход ОЗУ установлен в третье состояние.

Задержки передачи cодержимого адресуемого запоминающего элемента на выход ОЗУ при чтении и переключения выхода ОЗУ в третье состояние после снятия сигнала CS связаны с процессами включения и выключения выходных цепей.

Слайд 67Цикл обращения Tµ определяется сигналом CS, а именно минимально допустимым

временем между моментами его подачи или снятия.

4.4. Динамические ОЗУ

Накопитель динамических

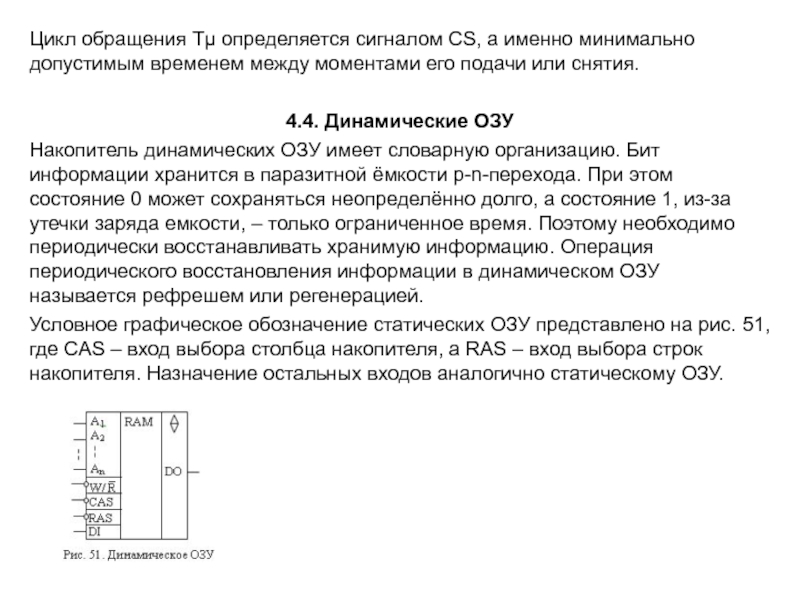

ОЗУ имеет словарную организацию. Бит информации хранится в паразитной ёмкости p-n-перехода. При этом состояние 0 может сохраняться неопределённо долго, а состояние 1, из-за утечки заряда емкости, – только ограниченное время. Поэтому необходимо периодически восстанавливать хранимую информацию. Операция периодического восстановления информации в динамическом ОЗУ называется рефрешем или регенерацией.

Условное графическое обозначение статических ОЗУ представлено на рис. 51, где CAS – вход выбора столбца накопителя, а RAS – вход выбора строк накопителя. Назначение остальных входов аналогично статическому ОЗУ.

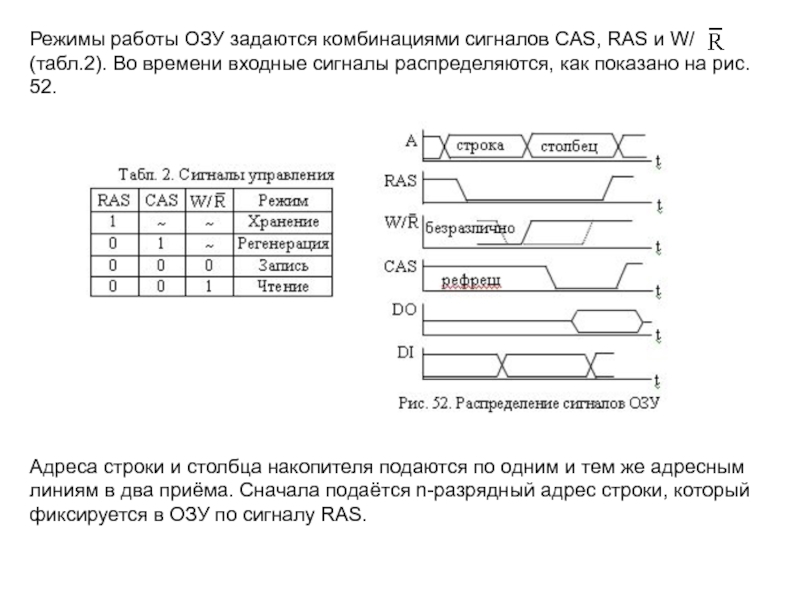

Слайд 68Режимы работы ОЗУ задаются комбинациями сигналов CAS, RAS и W/

(табл.2). Во времени входные сигналы распределяются, как показано на рис.

52.

Адреса строки и столбца накопителя подаются по одним и тем же адресным линиям в два приёма. Сначала подаётся n-разрядный адрес строки, который фиксируется в ОЗУ по сигналу RAS.

Слайд 69При пассивном сигнале CAS за относительно короткое время будет произведена

регенерация запоминающих элементов выбранной строки. Регенерация заключается в передаче информации

из запоминающих элементов адресованной строки в двунаправленные усилители регенерации, с выходов которых информация вновь записывается в те же запоминающие элементы. Таким образом, последовательно формируя адреса строк, за 2n тактов обеспечивается полная регенерация ОЗУ. По окончании регенерации подаётся n-разрядный адрес столбца, который также фиксируется в ОЗУ, но по сигналу CAS. При этом выбирается одна из разрядных линий, а значение сигнала W/R задает режим работы ОЗУ – запись или чтение.

Цикл обращения динамического ОЗУ определяется сигналом RAS.

4.5. ПЗУ

Накопитель ПЗУ представляет собой совокупность обычно 8-разрядных ячеек памяти и имеет словарно-матричную организацию.

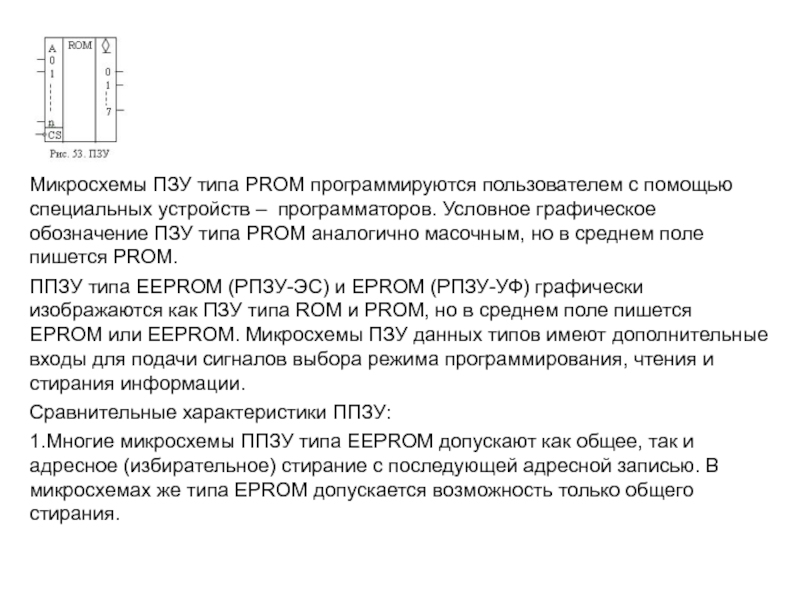

Масочные ПЗУ (типа ROM) программируются на заводе изготовителе с помощью индивидуальных для конкретных заказов фотошаблонов (масок). Такие ПЗУ широко используются в качестве носителей постоянных программ, подпрограмм, кодов физических констант, постоянных коэффициентов и т.п. Их условное графическое обозначение приведено на рис. 53.

Слайд 70

Микросхемы ПЗУ типа PROM программируются пользователем с помощью специальных устройств

– программаторов. Условное графическое обозначение ПЗУ типа PROM аналогично масочным,

но в среднем поле пишется PROM.

ППЗУ типа ЕEPROM (РПЗУ-ЭС) и EPROM (РПЗУ-УФ) графически изображаются как ПЗУ типа ROM и PROM, но в среднем поле пишется EPROM или EEPROM. Микросхемы ПЗУ данных типов имеют дополнительные входы для подачи сигналов выбора режима программирования, чтения и стирания информации.

Сравнительные характеристики ППЗУ:

1.Многие микросхемы ППЗУ типа ЕEPROM допускают как общее, так и адресное (избирательное) стирание с последующей адресной записью. В микросхемах же типа EPROM допускается возможность только общего стирания.

Слайд 712.По емкости ППЗУ типа EPROM превышают ППЗУ типа ЕEPROM.

3.ППЗУ типа

ЕEPROM, в отличие от EPROM, перепрограммируются без изъятия из устройства.

4.ППЗУ типа ЕEPROM допускают значительное число циклов перепрограммирования, достигающее 104. У ППЗУ типа EPROM число циклов перепрограммирования невелико – от 10 до 100.

5.ППЗУ типа EPROM требуют большого времени стирания (30 – 60 минут) и специально предназначенного для этой цели оборудования.

6.ППЗУ типа EPROM обладают сравнительно высоким быстродействием при невысокой стоимости.

4.6. Встроенная память/кэш

Обычно цифровые процессоры обработки сигналов работают настолько быстро, что медленная недорогая память не может поддерживать такой темп. В результате процессор замедляется – вводятся состояния ожидания, которые имеют программное управление, а иногда для этого требуются внешние аппаратные блоки. С целью решения этой проблемы во многие интегральные схемы цифровых процессоров встраивают скоростную внутреннюю память. При этом развитые архитектуры обладают выделенными внутренними памятью данных и программ, причем последняя может работать как обычная адресуемая память и как кэш (кэш-память).

Слайд 72Кэш используется в качестве буфера между собственно процессором и памятью

системы. Она имеет обычно небольшую емкость при высоком быстродействии и

используется для промежуточного запоминания информации, считываемой из памяти, прежде всего кодов команд. При чтении сначала выполняется обращение к кэш; если же необходимых данных там не оказалось, производится обращение к основной памяти, и полученные данные помещаются также в кэш. Выгода от использования кэш получается из-за того, что большинство прикладных программ носит циклический характер, и после первого обращения к основной программе в кэш (при достаточном объеме) попадают все циклически повторяющиеся команды программы, для выполнения которых нет необходимости обращаться к основной памяти. Чаще всего кэш работает по ассоциативному принципу, при котором в его ячейке хранится не только слово данных, но и адрес размещения этого слова в основной памяти, по которому и происходит поиск информации.

5. Типы адресаций операндов

Адресацией называется обращение к операнду (число, участвующее в операции), указание на который содержится в команде. Операнды, в зависимости от места своего хранения, могут указываться разными способами, которым соответствуют разные типы адресации, или, коротко, разные адресации.

Слайд 73При описании различных адресаций операндов используют понятия адресного кода и

исполнительного адреса. Адресный код АК – это информация об адресе

операнда, содержащаяся в команде. Исполнительный адрес АИ – это номер физической ячейки памяти, к которой производится обращение.

Первая группа адресаций устанавливает АИ по значению АК. Сюда входят непосредственная, прямая, регистровая, косвенная, автоинкрементная и автодекрементная адресации.

При непосредственной адресации операнд указывается в команде константой. Эта адресация используется только для указания исходных данных.

При прямой адресации АИ совпадает с АК.

При регистровой адресации в команде указывается имя регистра процессора, в котором хранится операнд.

Косвенная адресация используется в целях сокращения длины команды. В этом случае АК указывает имя регистра процессора, в котором находится АИ. Такой регистр называют регистром адреса..

При автоинкрементной (автодекрементной) адресации в команде указывается имя регистра процессора, содержимое которого автоматически увеличивается (уменьшается) на 1, причем изменение адреса может производиться как до (преинкремент/предекремент),

Слайд 74так и после (постинкремент/постдекремент) выполнения основной команды. Следовательно, преинкремент/предекремент означает

вычисление нового АИ перед выполнением команды, а постинкремент/постдекремент – что

АИ в данной команде не изменяется.

Вторая группа адресаций устанавливает АИ по АК и содержимому регистров процессора. Сюда входят индексная и базовая адресации. Оба типа адресаций позволяют при меньшей длине адресного кода команды обеспечить доступ к любой ячейке памяти.

Индексация (указание) означает автоматическое изменение АИ без изменения содержимого регистра адреса, называемого индексом, причем АИ вычисляется как алгебраическая сумма содержимого индекса и смещения. Таким образом, содержимое индекса задает начало некоторой области ячеек памяти, а смещение – конкретную ячейку памяти в этой области. В команде АК указывает имя индекса и сравнительно короткое смещение или имя регистра процессора, в котором оно содержится. Индексация используется при работе с массивами данных.

Слайд 75Базирование является развитием индексации. Здесь АИ также определяется алгебраической суммой

содержимого регистра адреса, называемого базой, и смещения, но с изменением

содержимого базы. При этом используются постинкремент/постдекремент и преинкремент/пре-декремент на величину смещения.