Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Последовательностные логические устройства

Содержание

- 1. Последовательностные логические устройства

- 2. Все ранее рассмотренные схемы являются схемами мгновенного

- 3. План лекции:1.Простейшие триггеры.2.D-триггеры.3.Регистры.

- 4. Простейшие триггеры Элементарной запоминающей ячейкой является триггер.

- 5. Слайд 5

- 6. Слайд 6

- 7. При подаче активного уровня на вход R

- 8. состояние выходных сигналов подобных схем зависит не

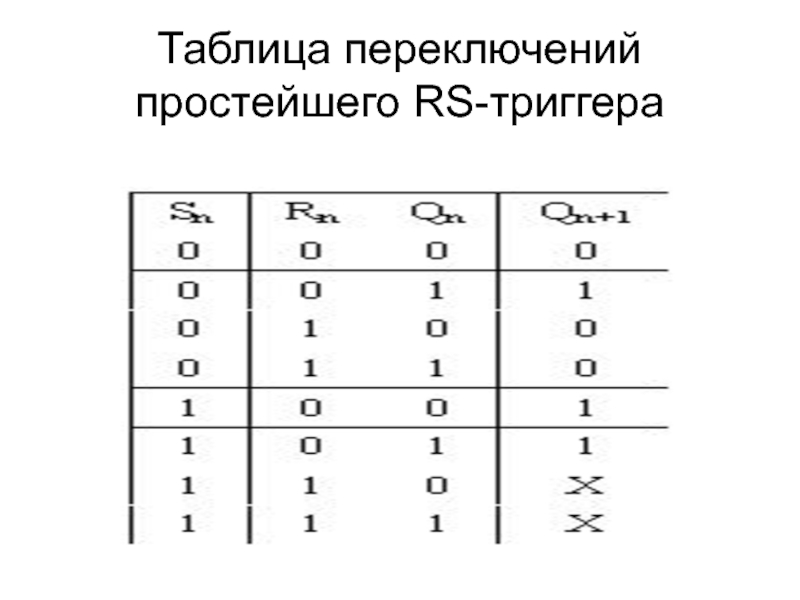

- 9. Таблица переключений простейшего RS-триггера

- 10. синхронный RS-триггер

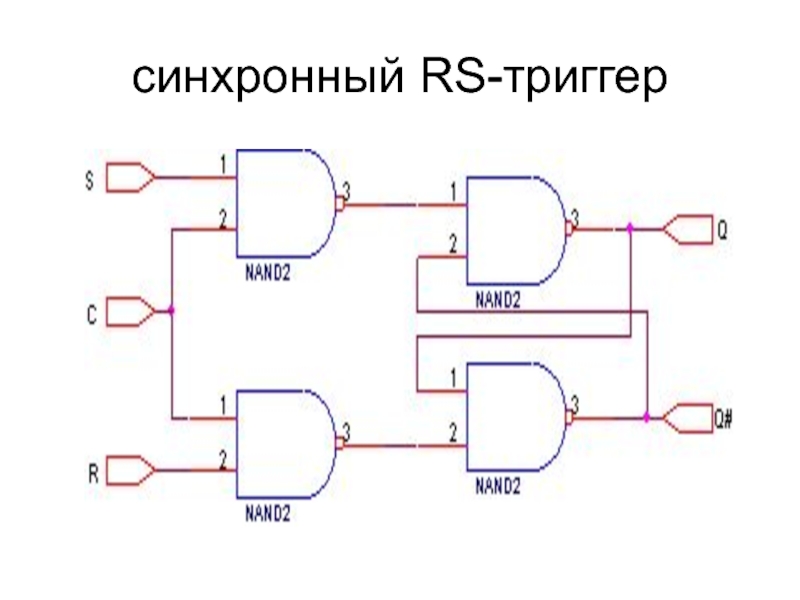

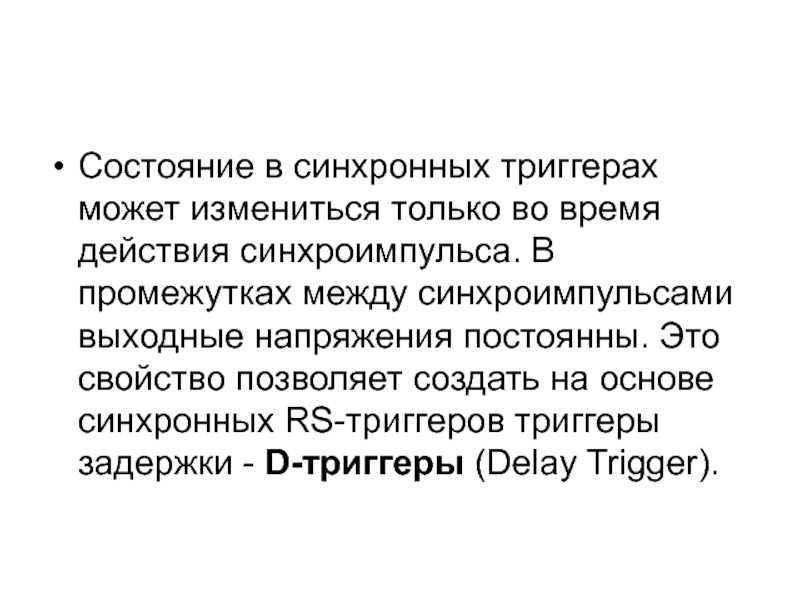

- 11. Состояние в синхронных триггерах может измениться только

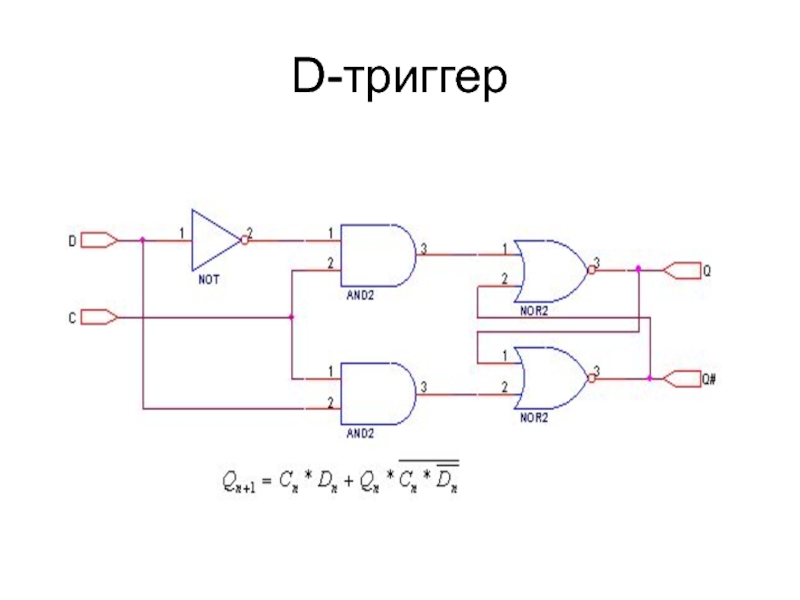

- 12. D-триггер

- 13. ). D-триггер фиксирует информацию, приходящую на один

- 14. Слайд 14

- 15. . Регистры Объединив несколько D-триггеров с единым

- 16. Слайд 16

- 17. Слайд 17

- 18. Слайд 18

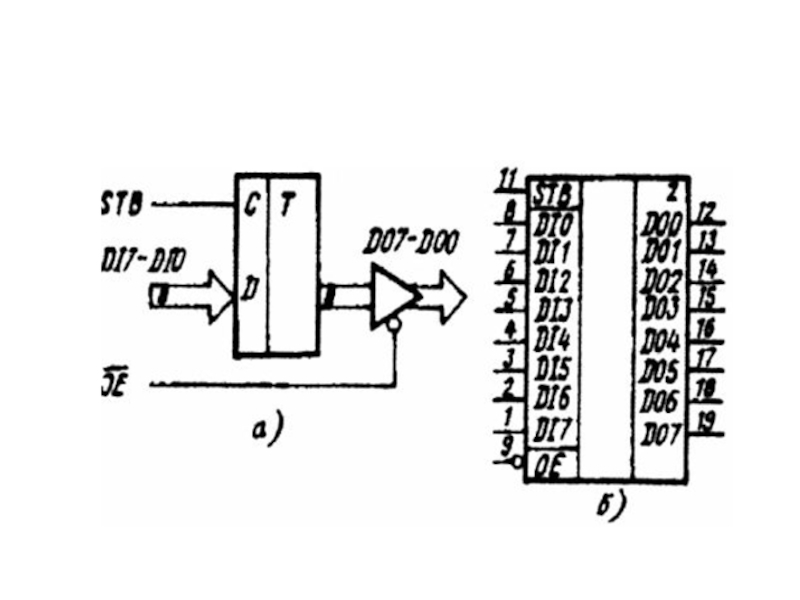

- 19. ). Запись данных в регистр разрешена при

- 20. Скачать презентанцию

Все ранее рассмотренные схемы являются схемами мгновенного действия. Информация на их выходах меняется мгновенно с изменением информации на входах. Поэтому, они называются комбинационными. Однако, зачастую бывает необходим элемент, способный запоминать информацию

Слайды и текст этой презентации

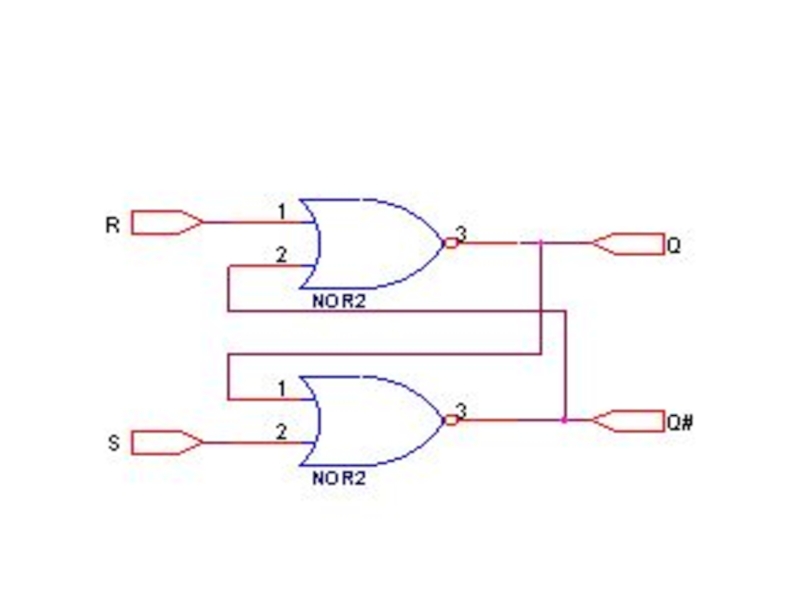

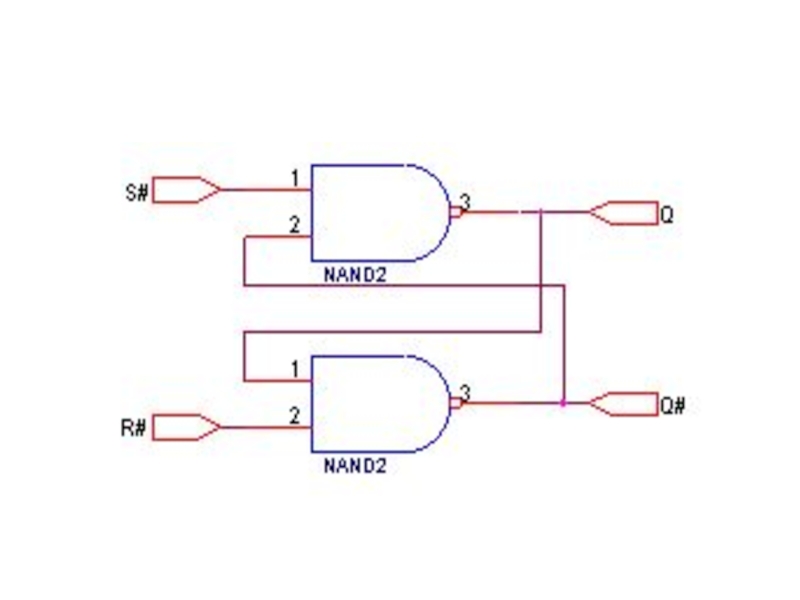

Слайд 4Простейшие триггеры

Элементарной запоминающей ячейкой является триггер. Простейший, т.н.

“R-S”

триггер может быть построен с помощью двух логических элементов путем

введения обратных связей.Слайд 7

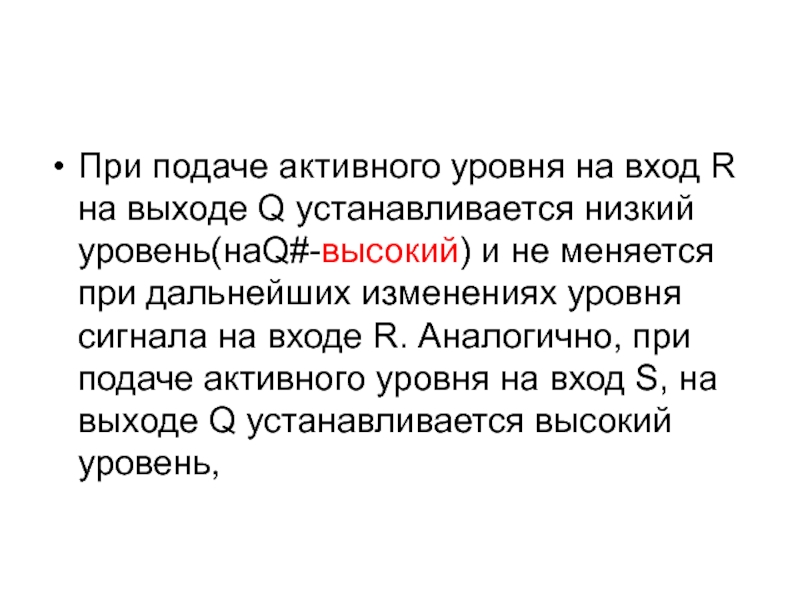

При подаче активного уровня на вход R на выходе Q

устанавливается низкий уровень(наQ#-высокий) и не меняется при дальнейших изменениях уровня

сигнала на входе R. Аналогично, при подаче активного уровня на вход S, на выходе Q устанавливается высокий уровень,Слайд 8

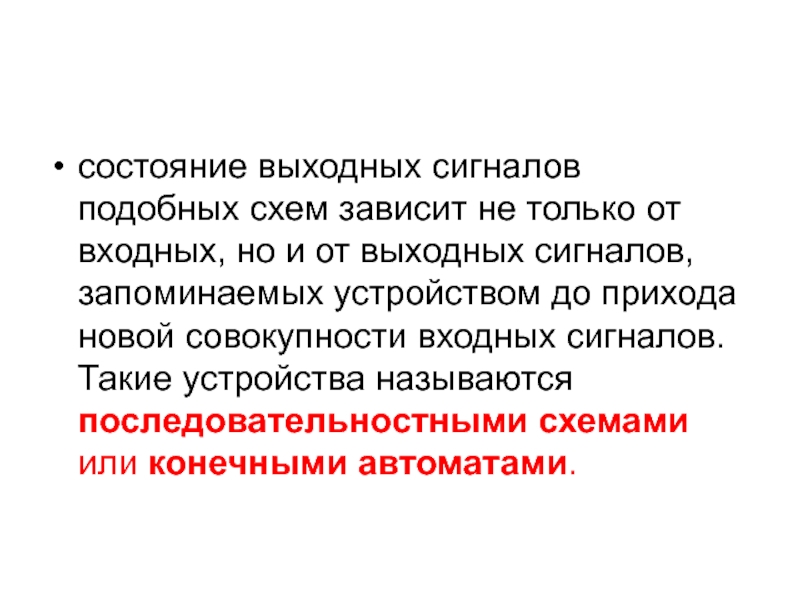

состояние выходных сигналов подобных схем зависит не только от входных,

но и от выходных сигналов, запоминаемых устройством до прихода новой

совокупности входных сигналов. Такие устройства называются последовательностными схемами или конечными автоматами.Слайд 11

Состояние в синхронных триггерах может измениться только во время действия

синхроимпульса. В промежутках между синхроимпульсами выходные напряжения постоянны. Это свойство

позволяет создать на основе синхронных RS-триггеров триггеры задержки - D-триггеры (Delay Trigger).Слайд 13

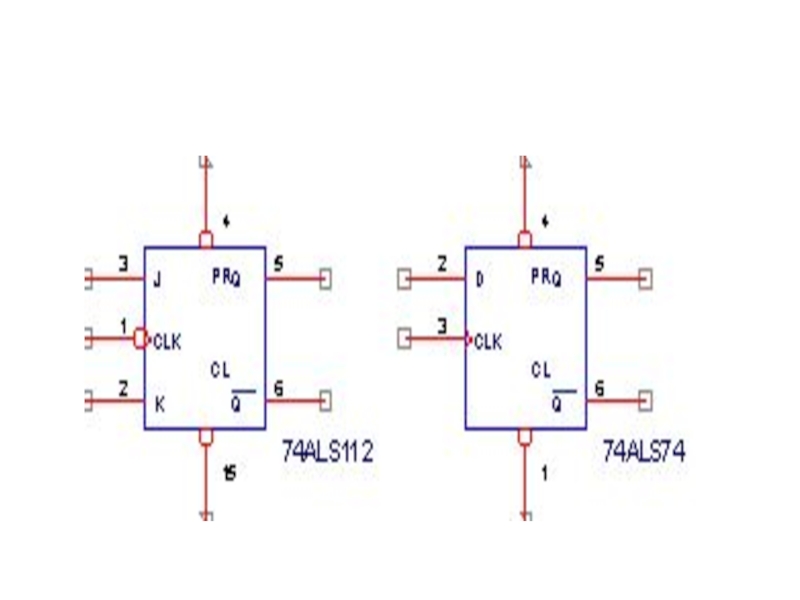

). D-триггер фиксирует информацию, приходящую на один вход данных. У

D-триггера значение выходного сигнала в (n+1) такте равно значению входного

сигнала в n такте. Т.о., D-триггер запоминает состояние входного сигнала на период одного такта квантования.Слайд 15. Регистры

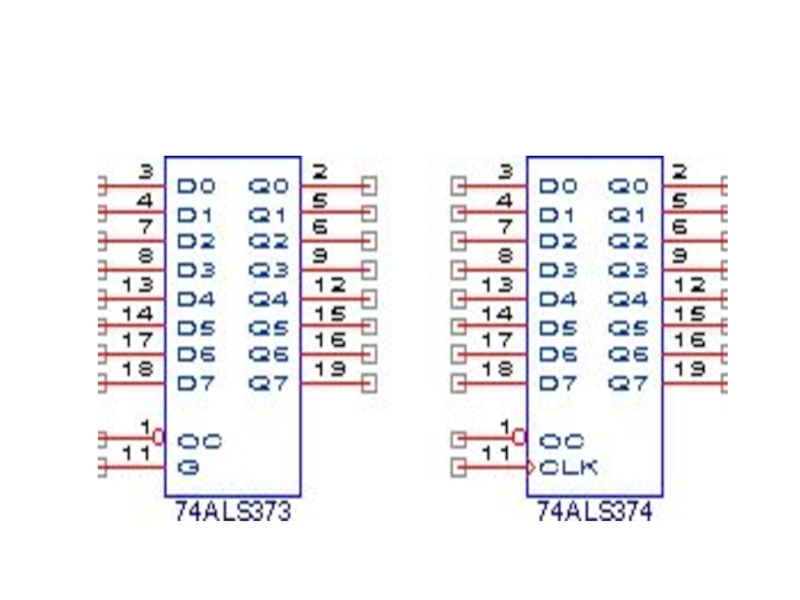

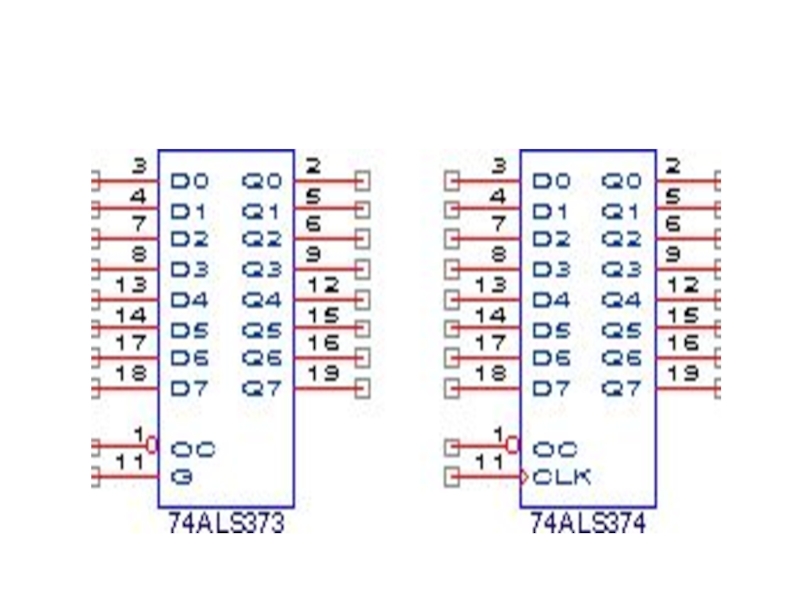

Объединив несколько D-триггеров с единым входом синхронизации можно

получить регистр, способный фиксировать многоразрядную информацию. В соответствии со структурой

внутренних триггеров существуют регистры-защелки и регистры с синхронным стробированием.. Регистры-защелки пропускают входную информацию на выход при одном уровне сигнала синхронизации и фиксируют ее при переходе сигнала синхронизации в другое состояние.

Регистры с синхронным стробированием фиксируют информацию по фронту сигнала синхронизации.