Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Суперскалярный процессор

Содержание

- 1. Суперскалярный процессор

- 2. Типы суперскалярных процессоровСтатический.Выполняет инструкции по порядку (in-order)Динамический.Выполняет

- 3. Статический суперскалярный процессорСхож с классическим конвейерным скалярным

- 4. Стадия планирования и группировки инструкций.Проверяет группу из

- 5. Достоинства и недостаткиДостоинства:Относительная аппаратная простота.Высокая пиковая производительность.Возможно

- 6. Модели статический суперскалярных процессоров.SunUltra Sparc III / IVIBMPOWER 6

- 7. Динамический суперскалярный процессор.Для планирования использует алгоритм Тамасуло.Усовершенствована

- 8. Что быстрее динамического суперскалярного процессора? Динамический суперскалярный

- 9. Спекулятивный суперскалярный процессор. (ССП)Спекуляция - выполнение некоторой

- 10. Этапы исполнения инструкцииАлгоритм ТамасулоВыборка инструкцииПланирование инструкцииОжидание готовности

- 11. Стадии записи результата и завершенияНа стадии записи

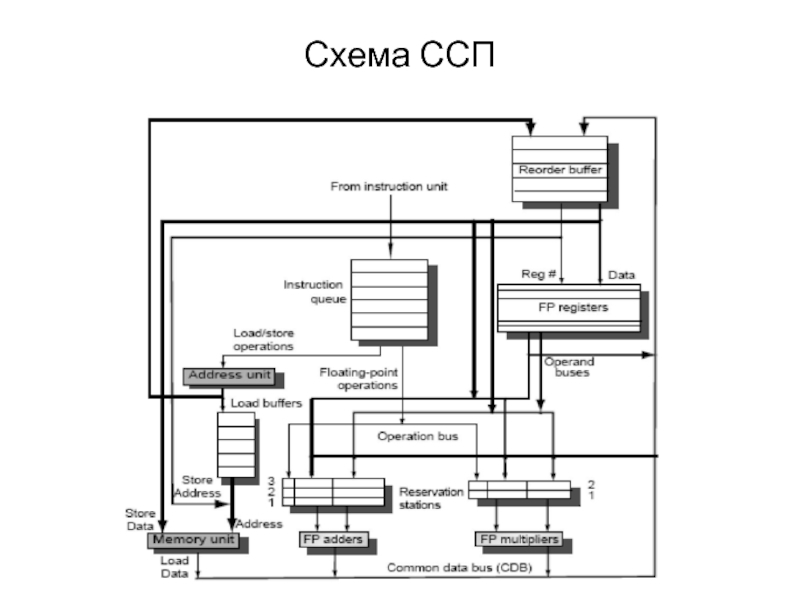

- 12. Изменения в аппаратной схемеДобавлен: буфер упорядочивания (reorder

- 13. Схема ССП

- 14. Описание работы схемы. Этап планирования.Планирование инструкций

- 15. Описание работы схемы. Этап исполнения и

- 16. Описание работы схемы. Этап завершения. Инструкция

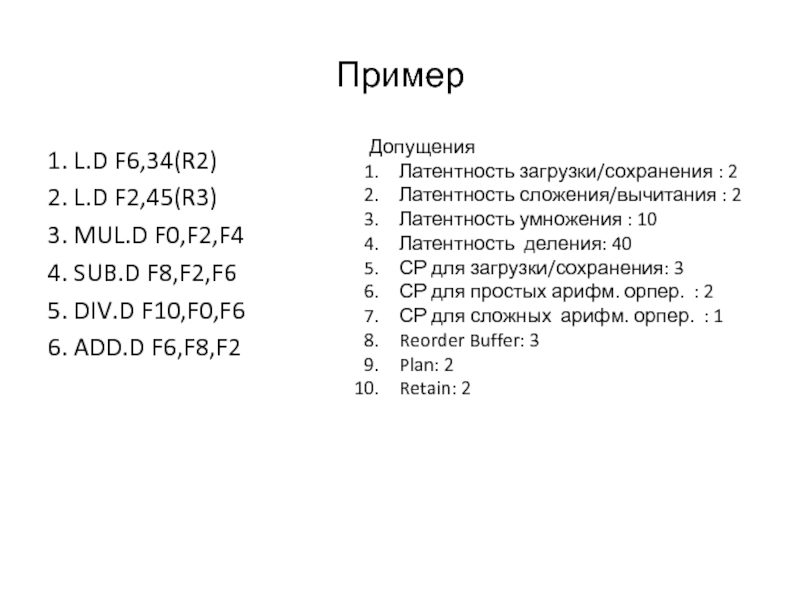

- 17. Пример1. L.D F6,34(R2)2. L.D F2,45(R3)3. MUL.D F0,F2,F44.

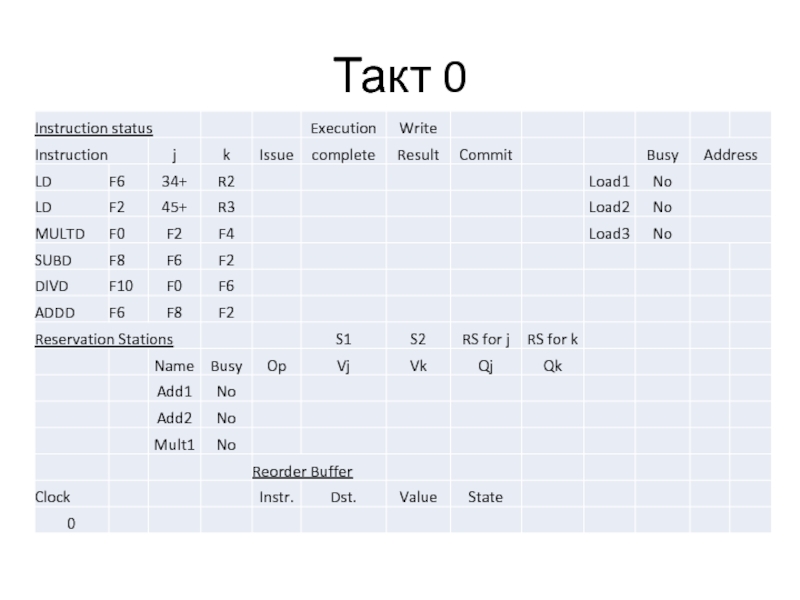

- 18. Такт 0

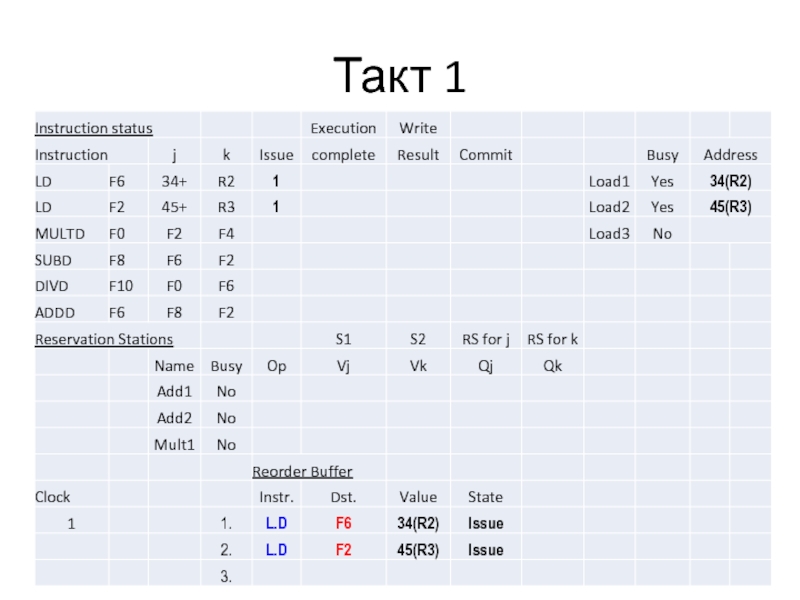

- 19. Такт 1

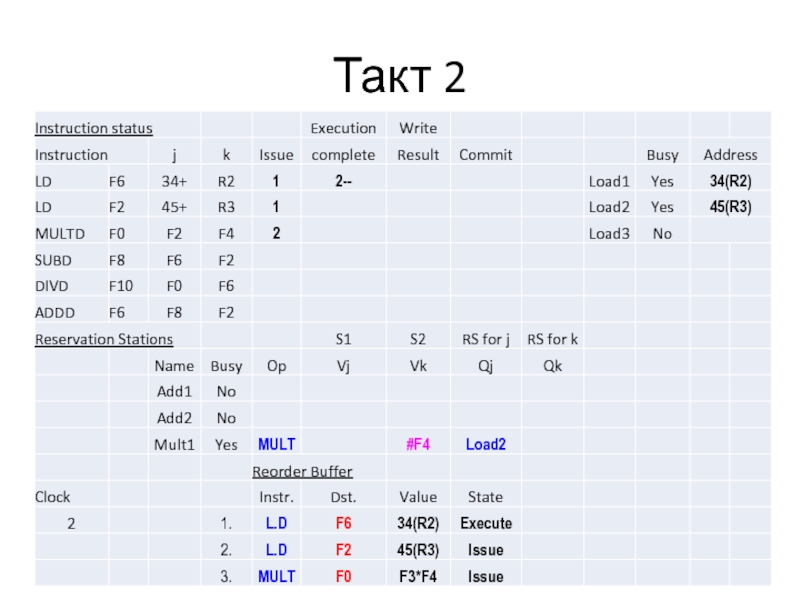

- 20. Такт 2

- 21. Такт 3

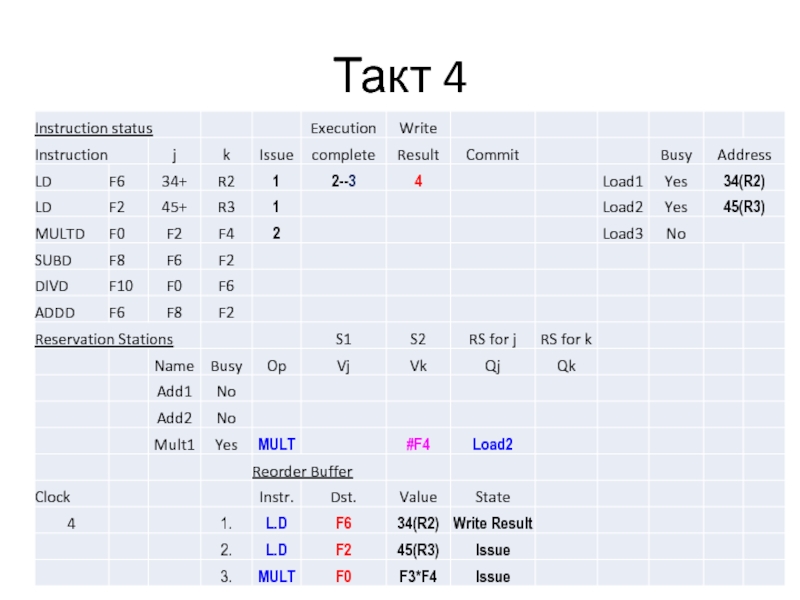

- 22. Такт 4

- 23. Такт 5

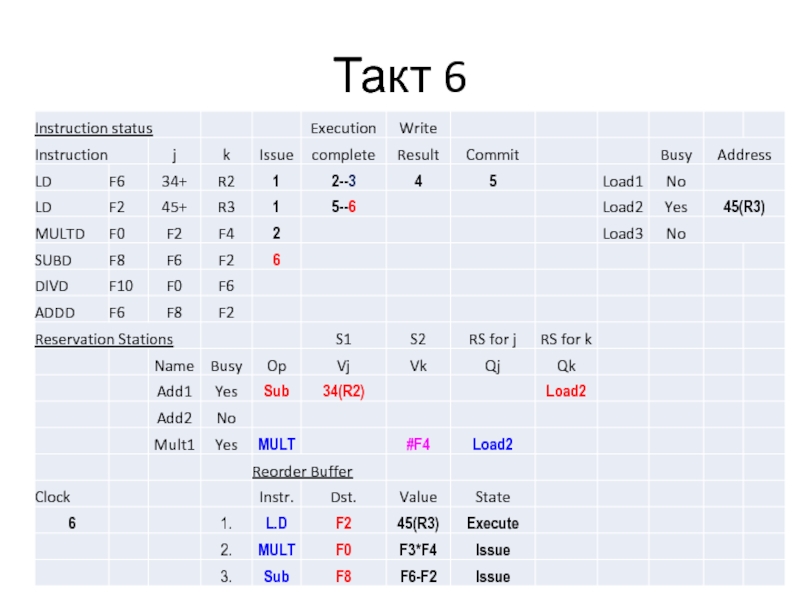

- 24. Такт 6

- 25. Такт 7

- 26. Такт 8

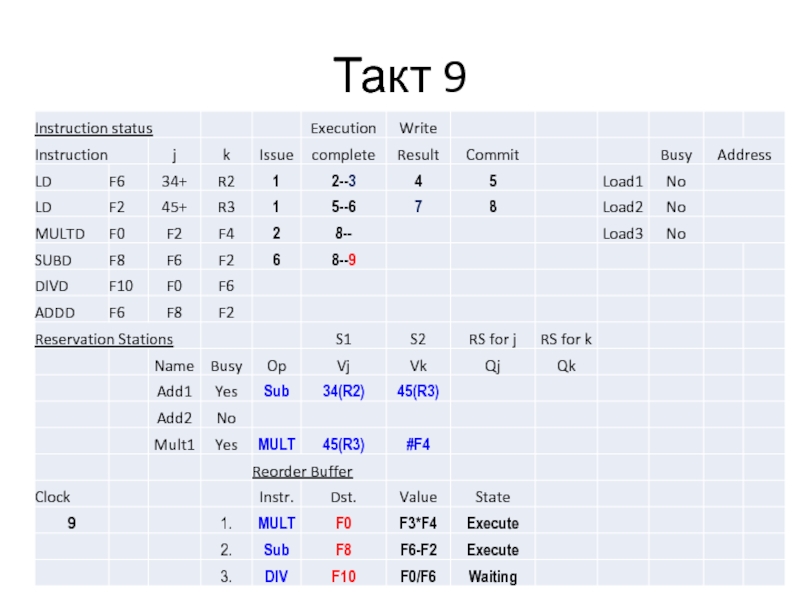

- 27. Такт 9

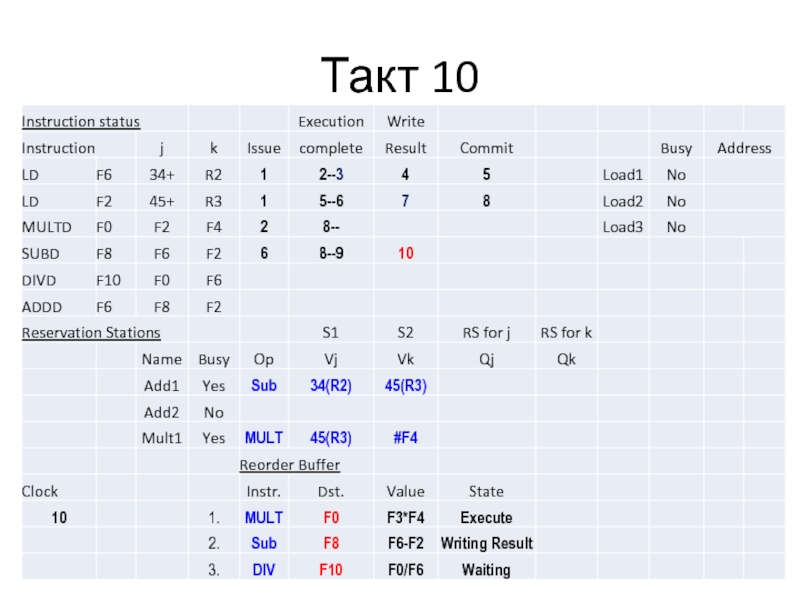

- 28. Такт 10

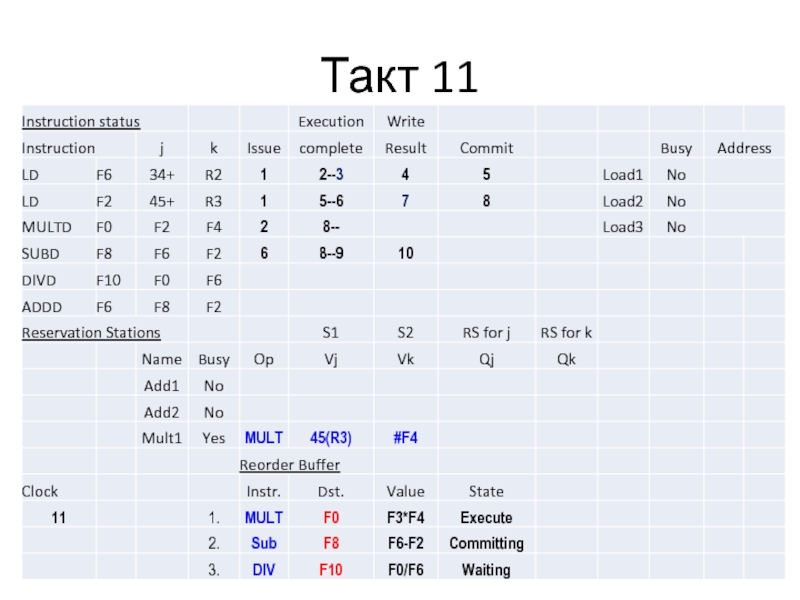

- 29. Такт 11

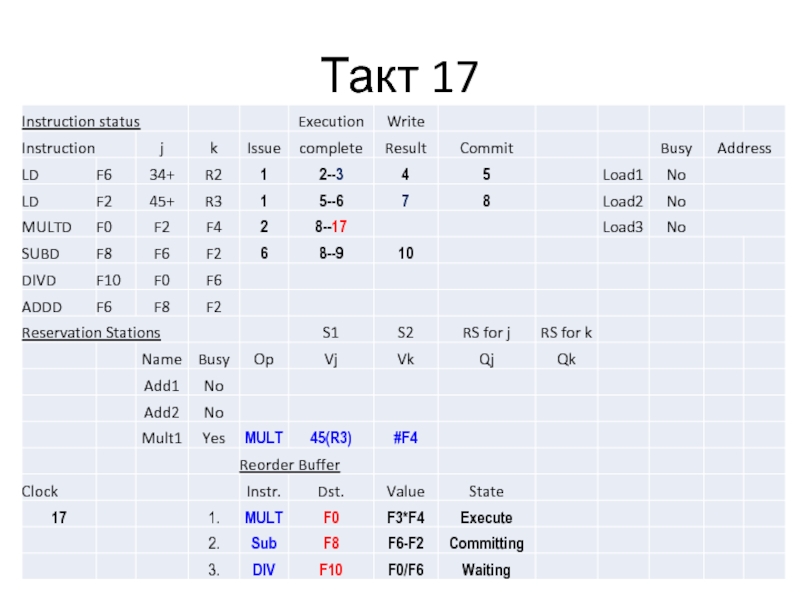

- 30. Такт 17

- 31. Такт 18

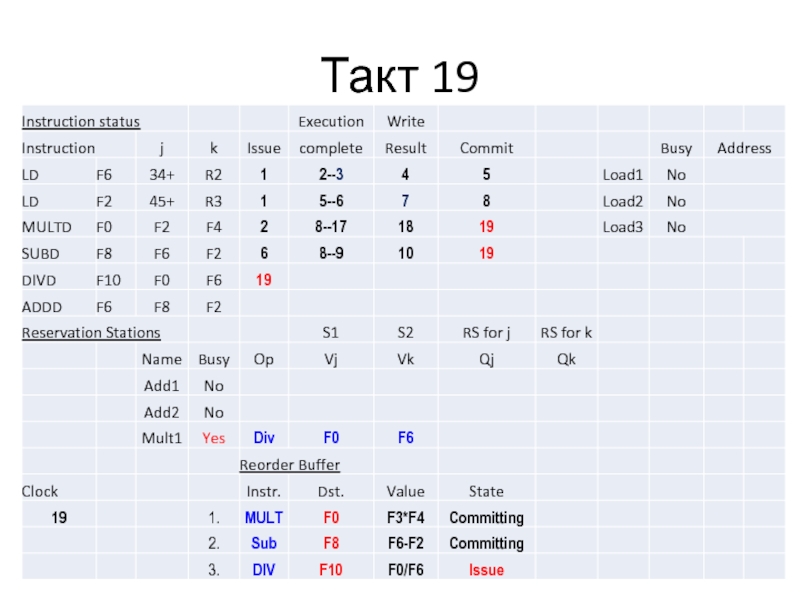

- 32. Такт 19

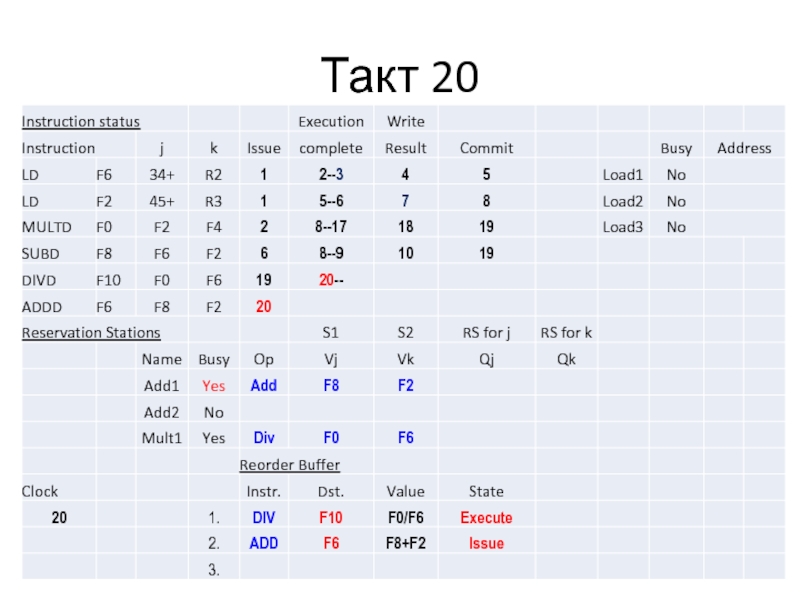

- 33. Такт 20

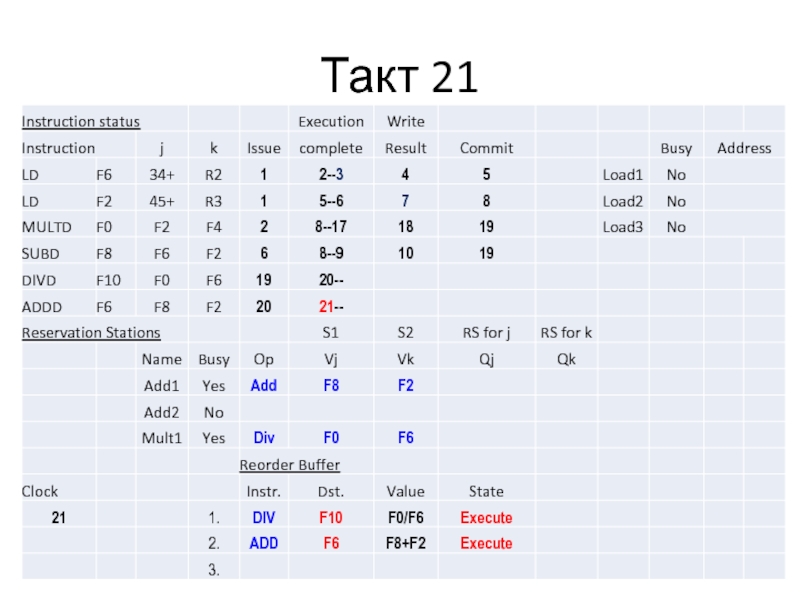

- 34. Такт 21

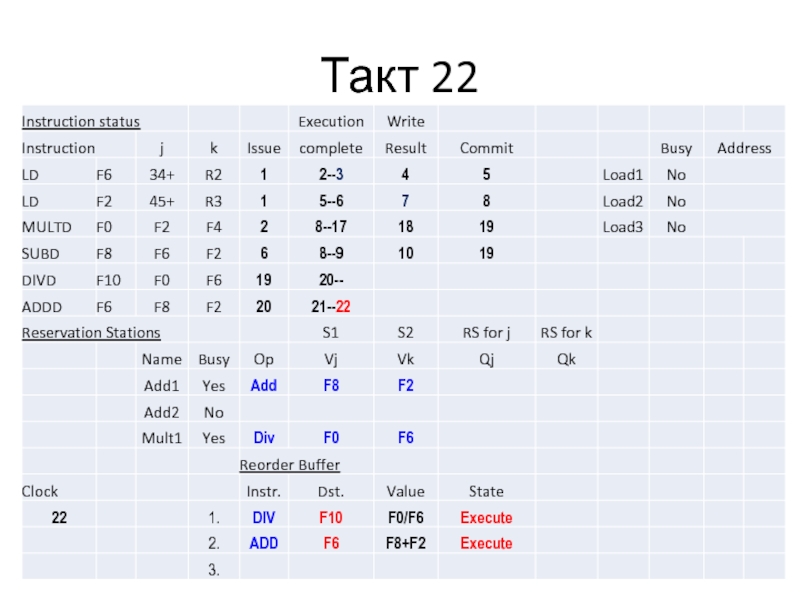

- 35. Такт 22

- 36. Такт 23

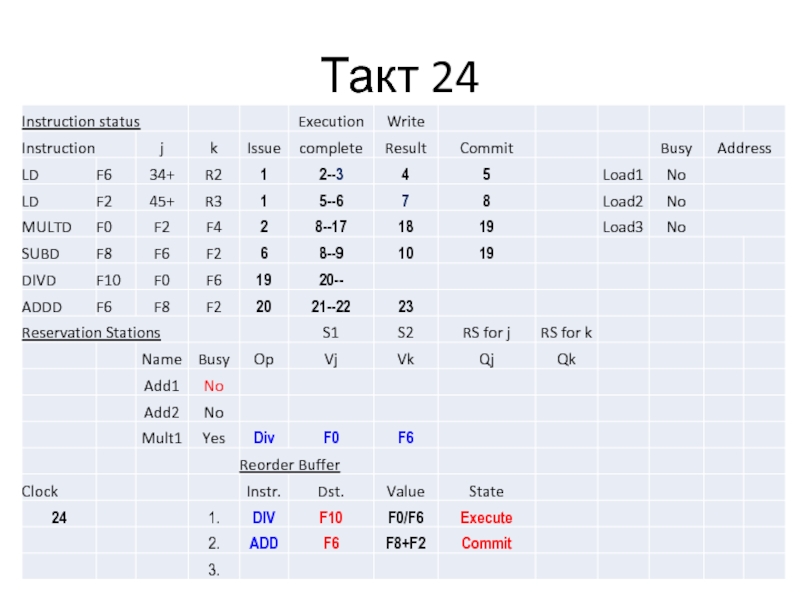

- 37. Такт 24

- 38. Такт 59

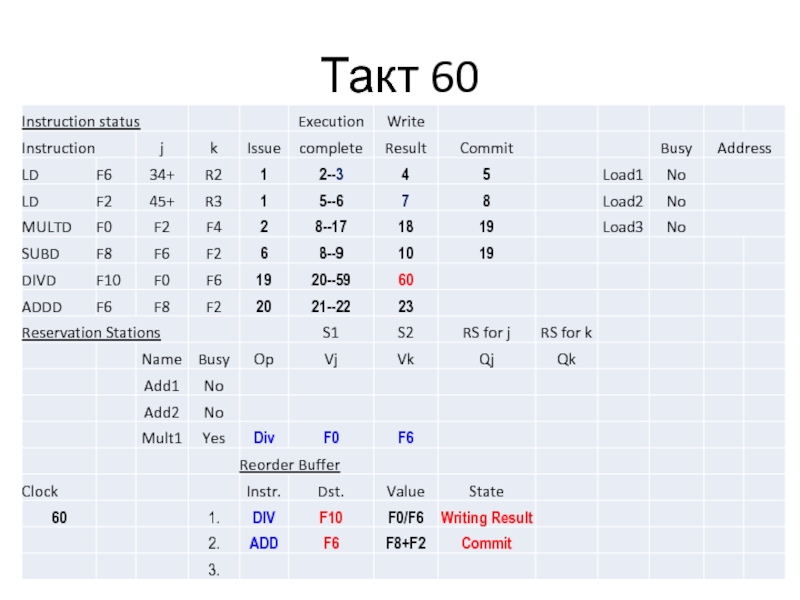

- 39. Такт 60

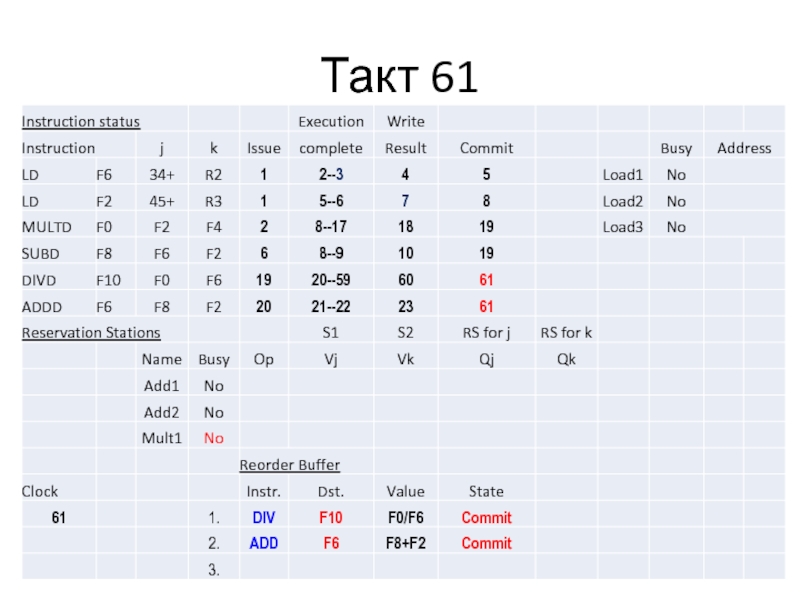

- 40. Такт 61

- 41. Что произойдет если будет сгенерировано исключение?Если в

- 42. Что обеспечивает выполнение критериев корректного исполнения программы?Сохранения

- 43. Ограничения спекуляции.Если инструкция в спекулятивном режиме вызвало

- 44. Ограничения планирования инструкций условного перехода.За один такт

- 45. Альтернативный подход к ССП Переименование регистров.Вычисленные значения

- 46. Особенности переименования регистров.Для своего функционирования требует два

- 47. Скачать презентанцию

Типы суперскалярных процессоровСтатический.Выполняет инструкции по порядку (in-order)Динамический.Выполняет инструкции вне порядка (out of order), кроме инструкций условного перехода.Спекулятивный.Выполняет все инструкции вне порядка (out of order). Спекулирует над инструкциями условного перехода и инструкциями

Слайды и текст этой презентации

Слайд 1Суперскалярный процессор

Это процессор который способен заканчивать или отставлять 2 и

более команды за такт.

но завершает всегда по одной.Слайд 2Типы суперскалярных процессоров

Статический.

Выполняет инструкции по порядку (in-order)

Динамический.

Выполняет инструкции вне порядка

(out of order), кроме инструкций условного перехода.

Спекулятивный.

Выполняет все инструкции вне

порядка (out of order). Спекулирует над инструкциями условного перехода и инструкциями загрузки/сохранения.

Слайд 3Статический суперскалярный процессор

Схож с классическим конвейерным скалярным процессором.

Все инструкции выполнятся

в рамках одного конвейера.

Появилась дополнительная стадия планирования и группировки

инструкций.Целочисленные и вещественные части конвейера выравниваются по длине с использованием пустых стадий.

Слайд 4Стадия планирования и группировки инструкций.

Проверяет группу из n инструкций на

наличие конфликтов внутри группы и с инструкциями, которые уже находятся

на исполнении.Если внутри группы инструкций обнаружен конфликт, то на исполнение отправляются инструкции, которые предшествуют первой конфликтной инструкции в программном порядке, а остальные инструкции ждут разрешения конфликта.

Также стадия отвечает за распределение инструкций между устройствами.

Слайд 5Достоинства и недостатки

Достоинства:

Относительная аппаратная простота.

Высокая пиковая производительность.

Возможно достижения высокой рабочей

частоты.

Недостатки:

Требуется перекомпиляция кода, для достижение высокого реального быстродействия.

Слайд 7Динамический суперскалярный процессор.

Для планирования использует алгоритм Тамасуло.

Усовершенствована стадия планирования, которая

может планировать более 2 инструкций за такт.

Инструкции после инструкции условного

перехода планируются, но не исполняются, до исполнения инструкции условного переходаСлайд 8Что быстрее динамического суперскалярного процессора?

Динамический суперскалярный процессор использует параллелизм

инструкций только в одном базовом блоке.

Следующим шагом является процессор, который

использует параллелизм нескольких базовых блоков.Слайд 9Спекулятивный суперскалярный процессор. (ССП)

Спекуляция - выполнение некоторой операции, необходимость выполнения

которой носит вероятностный характер.

ССП способен выполнять инструкции, которые следуют за

невыполненной инструкцией условного перехода, основываясь на данных предсказателя ветвления, и в случае неверного предсказания выполнять откат.Слайд 10Этапы исполнения инструкции

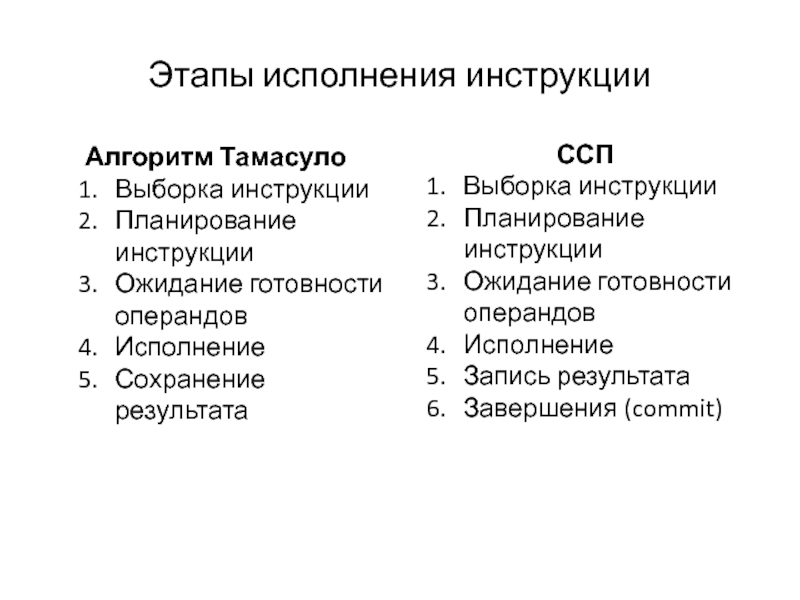

Алгоритм Тамасуло

Выборка инструкции

Планирование инструкции

Ожидание готовности операндов

Исполнение

Сохранение результата

ССП

Выборка

инструкции

Планирование инструкции

Ожидание готовности операндов

Исполнение

Запись результата

Завершения (commit)

Слайд 11Стадии записи результата и завершения

На стадии записи результата результат работы

инструкции помещается в промежуточное хранилище, а не в основной регистровый

файл.На стадии завершения производиться проверка корректности исполнения инструкции, генерируются исключения, происходит запись результатов из временного хранилища в основной регистровый файл.

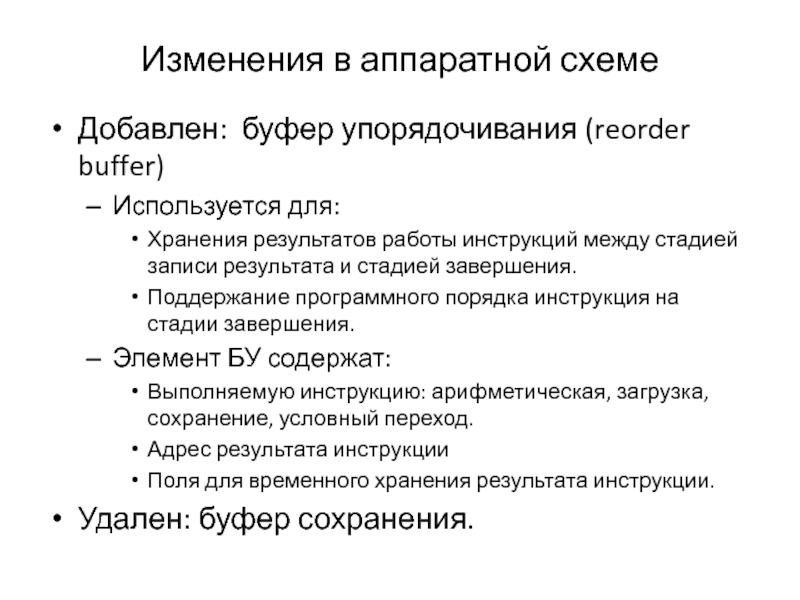

Слайд 12Изменения в аппаратной схеме

Добавлен: буфер упорядочивания (reorder buffer)

Используется для:

Хранения результатов

работы инструкций между стадией записи результата и стадией завершения.

Поддержание программного

порядка инструкция на стадии завершения.Элемент БУ содержат:

Выполняемую инструкцию: арифметическая, загрузка, сохранение, условный переход.

Адрес результата инструкции

Поля для временного хранения результата инструкции.

Удален: буфер сохранения.

Слайд 14Описание работы схемы.

Этап планирования.

Планирование инструкций осуществляется с вершины очереди

планирования.

Для выполнения планирования должна быть доступна СР на требуемом ФУ

и ячейка на БУ, если хотя бы один из ресурсов не доступен, то инструкция ожидает в очереди.Выборка операндов состоит из трех стадий:

Проверяются есть ли данные в регистровом файле, если есть переписываются в СР, если нет, то

Проверяются есть ли данные в БУ, если есть переписываются в СР, если нет, то

В СР записывается номер ячейки БУ которая содержит инструкцию, которая вычислит этот операнд.

В файл переименования для результирующего регистра инструкции помещается номер ячейки БУ, которая ее содержит.

Слайд 15Описание работы схемы.

Этап исполнения и записи результат.

Инструкции запускаются

на исполнении по мере готовности их операндов и доступности ФУ.

По

общей шине передается результат инструкции и номер ячейки БУ, которая ее содержит.Запись результата производится одновременно во все ожидающие СР и БУ.

Инструкция загрузки выполняется в две стадии:

Вычисление адреса.

Чтение из памяти. Запускается если нет конфликтов с предыдущими инструкциями загрузки и сохранения.

Инструкция сохранения на этапе исполнения вычисляет адрес операнда и ожидает готовности результат, запись в память произойдет на стадии завершения.

Слайд 16Описание работы схемы.

Этап завершения.

Инструкция после вычисления результата ожидает

в БУ своего завершения.

Завершаются инструкции, которые находятся на вершину БУ.

БУ поддерживает поведение очереди FIFO.На этапе завершения:

Для арифметических инструкции и инструкции загрузки проверяется наличия исключений и если исключений нет, то результат записывается регистровый файл.

Для инструкции сохранения проверяется наличия исключений и если исключений нет, то результат записывается в память.

Для инструкции условного перехода проверяется правильно она была предсказана или нет, если да, то инструкция удаляется из БУ, если нет, происходит сброс процессора: очищаются все стадии, на планирование отправляется первая инструкция из правельной ветви.

Слайд 17Пример

1. L.D F6,34(R2)

2. L.D F2,45(R3)

3. MUL.D F0,F2,F4

4. SUB.D F8,F2,F6

5. DIV.D

F10,F0,F6

6. ADD.D F6,F8,F2

Допущения

Латентность загрузки/сохранения : 2

Латентность сложения/вычитания : 2

Латентность

умножения : 10Латентность деления: 40

СР для загрузки/сохранения: 3

СР для простых арифм. орпер. : 2

СР для сложных арифм. орпер. : 1

Reorder Buffer: 3

Plan: 2

Retain: 2

Слайд 41Что произойдет если будет сгенерировано исключение?

Если в процессе завершения инструкции

выяснится, что она сгенерировала исключение, то произойдет сброс конвейера, как

при ошибке предсказания перехода.Слайд 42Что обеспечивает выполнение критериев корректного исполнения программы?

Сохранения потока данных происходит

за счет использование СР и БУ, для восстановления явных связей

между инструкциями по данным.Сохранение поведения исключений происходит:

За счет использования отложенной генерации исключений. Исключение генерируется не на стадии исполнения, когда обнаруживается, а на стадии завершения.

За счет отставки инструкции в программном порядке.

Слайд 43Ограничения спекуляции.

Если инструкция в спекулятивном режиме вызвало кэш промах стоит

его обрабатывать или нет?

Обрабатываются обычно только самые легкие события, такие

как промах в кэш первого уровня, остальные события откладываются до выхода инструкции из спекулятивного режима.Ошибочная спекуляция приводит к выполнению бессмысленной работы и трате энергии.

Количество инструкций условного перехода над которыми производится спекуляция может быть ограничена.

Слайд 44Ограничения планирования инструкций условного перехода.

За один такт может быть запланирована

только одна инструкция условного перехода, которая предсказана как выполненная.

Это объясняется

тем, что только на следующем такте будут доступны инструкции из выбранной ветви.Если инструкция предсказана как пропущенная, то одновременно с ней может быть запланированы последующие инструкции, и предсказана следующая инструкция условного перехода.

Указанное ограничение является серьезным фактором который ограничивает рост производительности ССП при увеличение кол-ва одновременно завершаемых инструкций.

Слайд 45Альтернативный подход к ССП

Переименование регистров.

Вычисленные значения инструкций до стадии завершения

хранятся в основном регистровом файле во вне архитектурных регистрах, вместо

БУ.На стадии завершение нужный теневой регистр переименовывается в архитектурный.

Такой подход позволяет упростить структуру процессора, так как все данные хранятся в одном месте.

Слайд 46Особенности переименования регистров.

Для своего функционирования требует два файл переименования для

связи архитектурных регистров с физическими.

Первый файл содержит информацию о текущих

архитектурных регистрах. Их отображении на физические регистры и ячейки БУ.Второй файл содержит информацию действительных архитектурных регистрах. Их отображении на физические регистры.