Универсальные шины адреса и данных для доступа к памяти программ,

данных и устройствам ввода-вывода.(Модифицированная) Гарвардская архитектура.

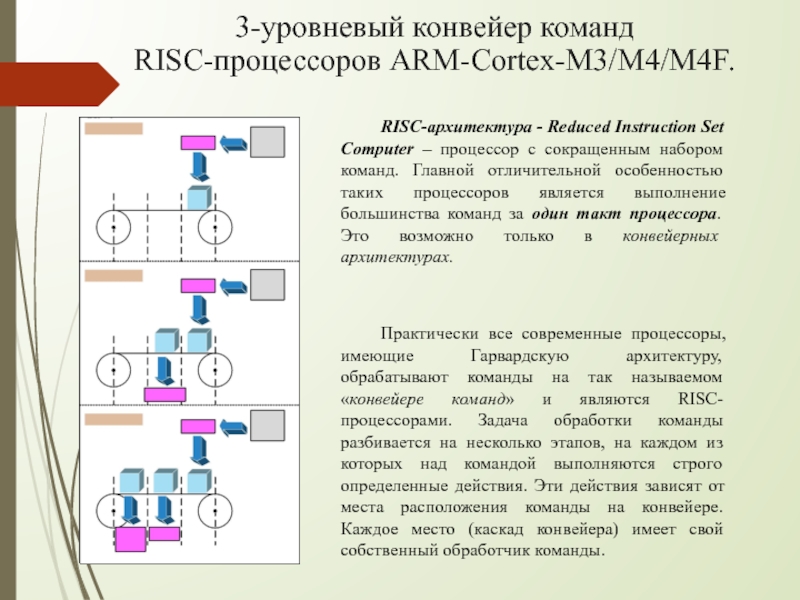

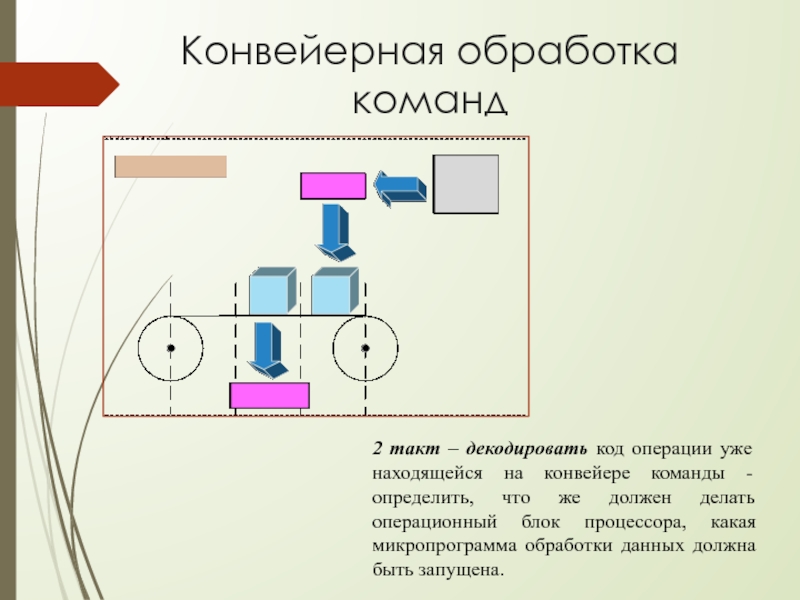

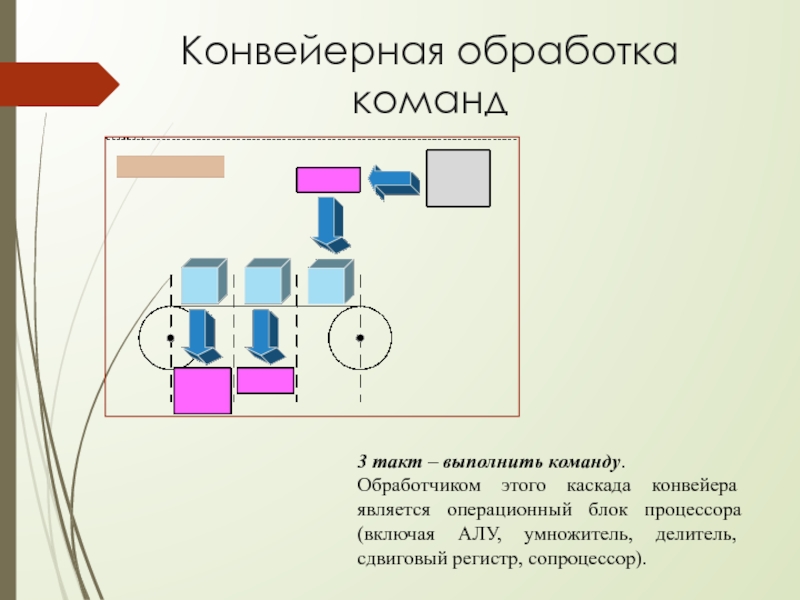

Изолированные шины для записи и чтения операндов в память данных, считывания из и записи в память программ. Резкое повышение производительности за счет использования многоуровневого конвейера команд и совмещения операций доступа к данным. Аппаратная поддержка умножения с накоплением для задач цифровой фильтрации и управления.

Мультипроцессорные архитектуры современных процессоров и микроконтроллеров с общей памятью и периферийными устройствами.

Основные типы процессорных архитектур