Слайд 1Глава 3. Базовые элементы цифровых интегральных схем.

Цифровые интегральные схемы

В современной

радиоэлектронике наряду с аналоговыми широко применяются цифровые сигналы.

ИС предназначенные

для обработки, преобразования и хранения информации представленной в цифровом виде называются - цифровыми ИМС (ЦИС).

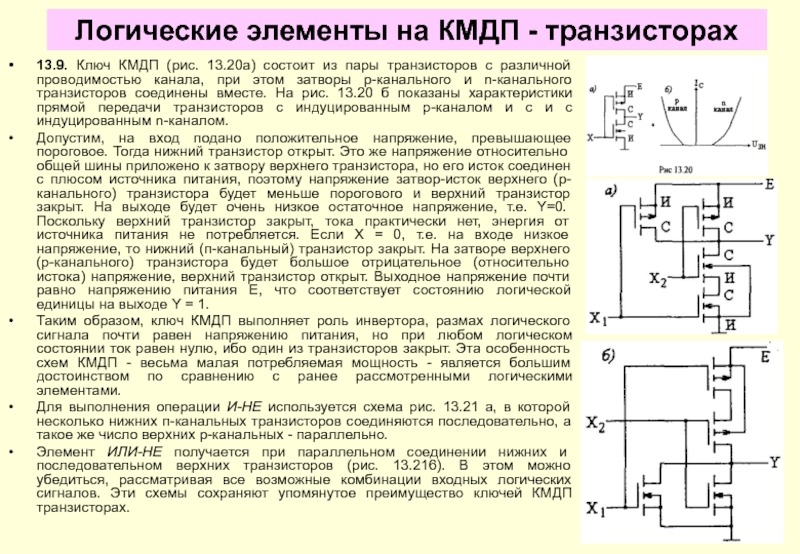

При цифровом представлении непрерывный сигнал заменяется своими отсчётами, которым в соответствии с их величиной ставится соответствующее число. В современной технике цифровые сигналы представляются в двоичной системе счисления. В ней числа принимают два значения 0 и 1.

В электронике двум значениям ставят в соответствии два резко отличающихся по своим характеристикам сигнала. Обычно применяют следующие способы кодирования: потенциальное и импульсное и импульсно-потенциальное.

При потенциальном кодирование переменным цифрового сигнала 0 и 1 ставят в соответствие два напряжения отличных по величине. При этом различают положительную и отрицательную логику кодирования. При импульсное кодирование «0 и «1», за 1 принимают наличие перепада потенциала во время импульса одной полярности, а за 0 – другой полярности.

В радиосвязи для кодирования двоичных сигналов применяют гармонические сигнала с разными амплитудами, частотами или начальными фазами.

Основные преимущества ЦИС.

- Они более помехоустойчивы чем аналоговые, т.к. небольшие помехи и разброс

параметров элементов при их изготовлении не вызывают ложных срабатываний.

По функциональному назначению ЦИС подразделяют на:

Комбинационные устройства. (Логические элементы).

Устройства последовательного типа. Содержат элементы памяти – триггеры).

Слайд 2Основные понятия теории логических схем

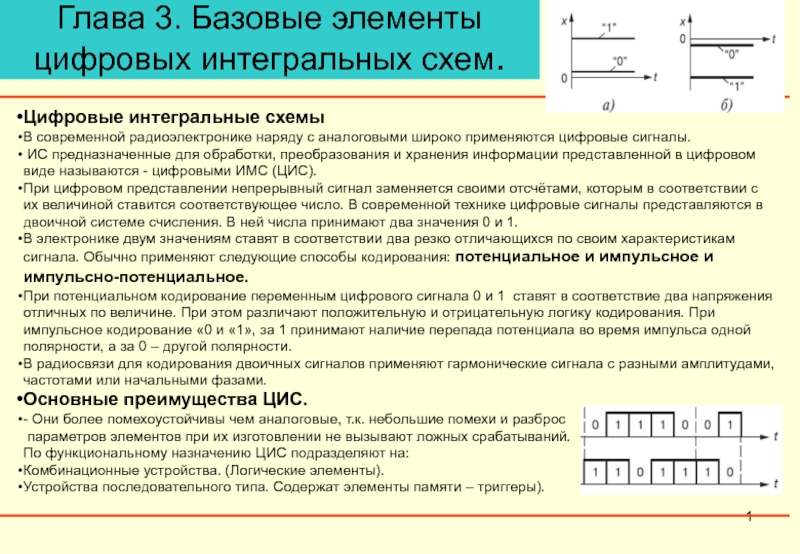

Теоретической основой построения логических схем и

устройств является алгебра логика или алгебра Буля. Она оперирует с

двумя логическими высказываниями (переменными), относительно которых можно сказать, что они: «истинно» или «ложно». Им соответствуют переменные двоичной системы счисления 0 и 1. Для логических переменных, принимающих два значения, существуют пять простых (основных) операции.

Сложное высказывание называется – логической функцией y = f (x1,x2,…xn), причём x1,.. xn и Y могут принимать лишь значения «0» и «1».

Логическая функция технически реализуется логическим

элементом (рис. ) слева, у которого показаны входы, а

справа выход.

Логическую функцию можно задать четырьмя

основными способами:

1. словесно – в виде правила;

2. таблично – в виде таблицы истинности. В ней указываются все наборы аргументов и значения функции, которую она принимает на этих наборах. Для функции n-переменных число наборов М=2n ; y=f (x1;x2).

3. Аналитически - в виде структурной или логической формулы.

4. Схемно - условным обозначение логического элемента.

Слайд 3

Основные операции алгебры логики

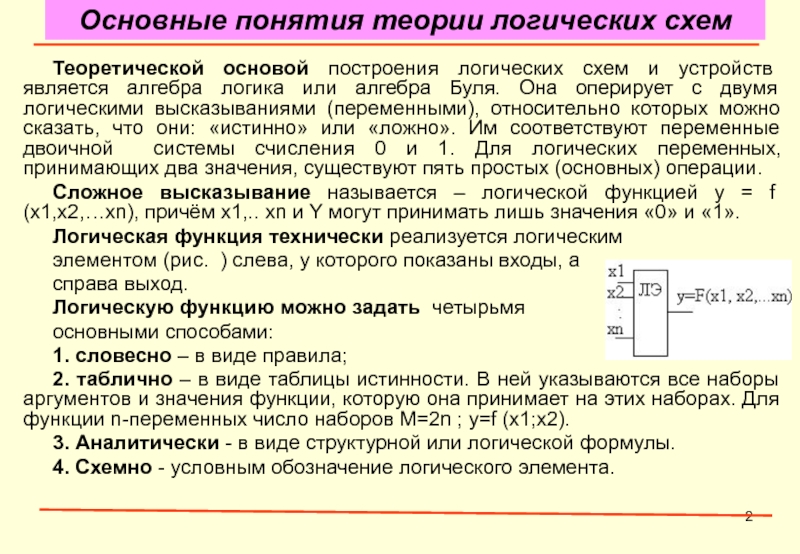

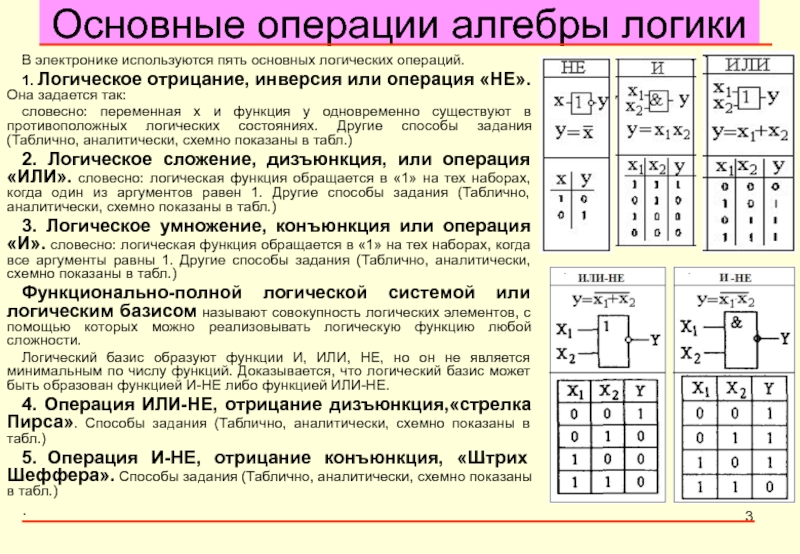

В электронике используются пять основных логических операций.

1.

Логическое отрицание, инверсия или операция «НЕ». Она задается так:

словесно: переменная

х и функция у одновременно существуют в противоположных логических состояниях. Другие способы задания (Таблично, аналитически, схемно показаны в табл.)

2. Логическое сложение, дизъюнкция, или операция «ИЛИ». словесно: логическая функция обращается в «1» на тех наборах, когда один из аргументов равен 1. Другие способы задания (Таблично, аналитически, схемно показаны в табл.)

3. Логическое умножение, конъюнкция или операция «И». словесно: логическая функция обращается в «1» на тех наборах, когда все аргументы равны 1. Другие способы задания (Таблично, аналитически, схемно показаны в табл.)

Функционально-полной логической системой или логическим базисом называют совокупность логических элементов, с помощью которых можно реализовывать логическую функцию любой сложности.

Логический базис образуют функции И, ИЛИ, НЕ, но он не является минимальным по числу функций. Доказывается, что логический базис может быть образован функцией И-НЕ либо функцией ИЛИ-НЕ.

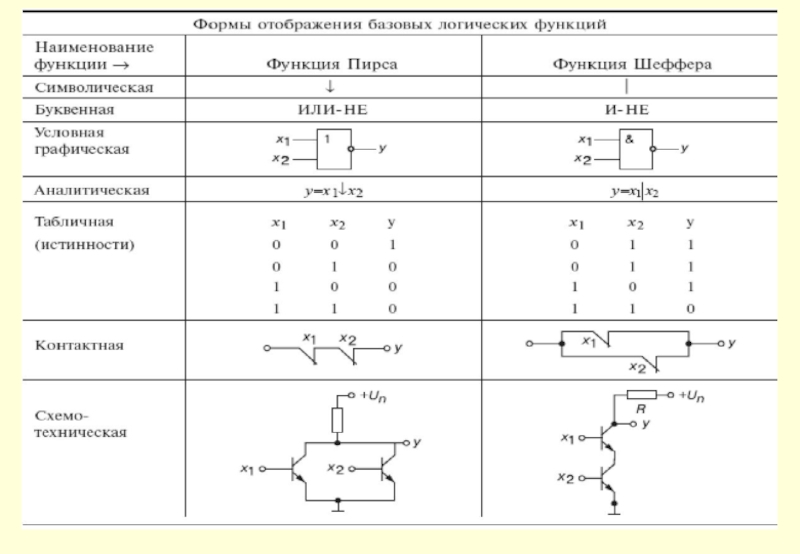

4. Операция ИЛИ-НЕ, отрицание дизъюнкция,«стрелка Пирса». Способы задания (Таблично, аналитически, схемно показаны в табл.)

5. Операция И-НЕ, отрицание конъюнкция, «Штрих Шеффера». Способы задания (Таблично, аналитически, схемно показаны в табл.)

.

Слайд 6Классификация логических

интегральных схем.

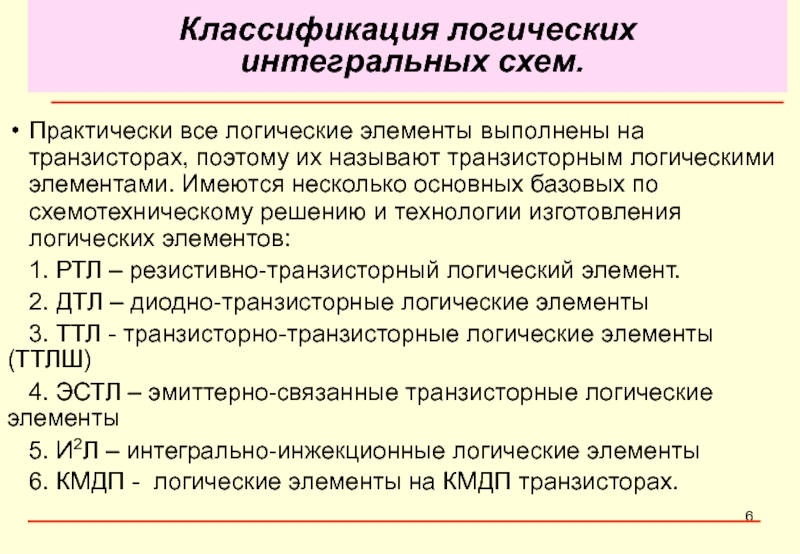

Практически все логические элементы выполнены на транзисторах,

поэтому их называют транзисторным логическими элементами. Имеются несколько основных базовых

по схемотехническому решению и технологии изготовления логических элементов:

1. РТЛ – резистивно-транзисторный логический элемент.

2. ДТЛ – диодно-транзисторные логические элементы

3. ТТЛ - транзисторно-транзисторные логические элементы (ТТЛШ)

4. ЭСТЛ – эмиттерно-связанные транзисторные логические элементы

5. И2Л – интегрально-инжекционные логические элементы

6. КМДП - логические элементы на КМДП транзисторах.

Слайд 7Основные параметры логических схем

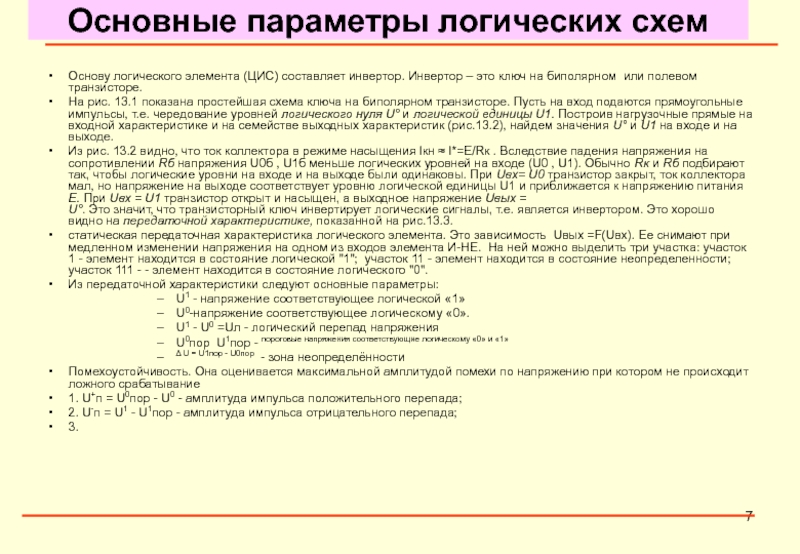

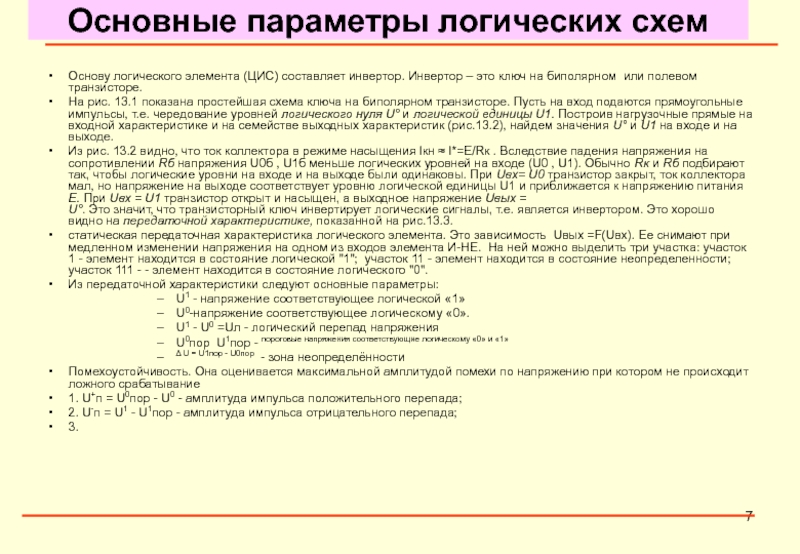

Основу логического элемента (ЦИС) составляет инвертор. Инвертор

– это ключ на биполярном или полевом транзисторе.

На рис.

13.1 показана простейшая схема ключа на биполярном транзисторе. Пусть на вход подаются прямоугольные импульсы, т.е. чередование уровней логического нуля U° и логической единицы U1. Построив нагрузочные прямые на входной характеристике и на семействе выходных характеристик (рис.13.2), найдем значения U° и U1 на входе и на выходе.

Из рис. 13.2 видно, что ток коллектора в режиме насыщения Iкн ≈ I*=Е/Rк . Вследствие падения напряжения на сопротивлении Rб напряжения U0б , U1б меньше логических уровней на входе (U0 , U1). Обычно Rк и Rб подбирают так, чтобы логические уровни на входе и на выходе были одинаковы. При Uвх= U0 транзистор закрыт, ток коллектора мал, но напряжение на выходе соответствует уровню логической единицы U1 и приближается к напряжению питания Е. При Uвх = U1 транзистор открыт и насыщен, а выходное напряжение Uвых =

U°. Это значит, что транзисторный ключ инвертирует логические сигналы, т.е. является инвертором. Это хорошо видно на передаточной характеристике, показанной на рис.13.3.

статическая передаточная характеристика логического элемента. Это зависимость Uвых =F(Uвх). Ее снимают при медленном изменении напряжения на одном из входов элемента И-НЕ. На ней можно выделить три участка: участок 1 - элемент находится в состояние логической "1"; участок 11 - элемент находится в состояние неопределенности; участок 111 - - элемент находится в состояние логического "0".

Из передаточной характеристики следуют основные параметры:

U1 - напряжение соответствующее логической «1»

U0-напряжение соответствующее логическому «0».

U1 - U0 =Uл - логический перепад напряжения

U0пор U1пор - пороговые напряжения соответствующие логическому «0» и «1»

U = U1пор - U0пор - зона неопределённости

Помехоустойчивость. Она оценивается максимальной амплитудой помехи по напряжению при котором не происходит ложного срабатывание

1. U+п = U0пор - U0 - амплитуда импульса положительного перепада;

2. U-п = U1 - U1пор - амплитуда импульса отрицательного перепада;

3.

Слайд 8Основные параметры логических схем

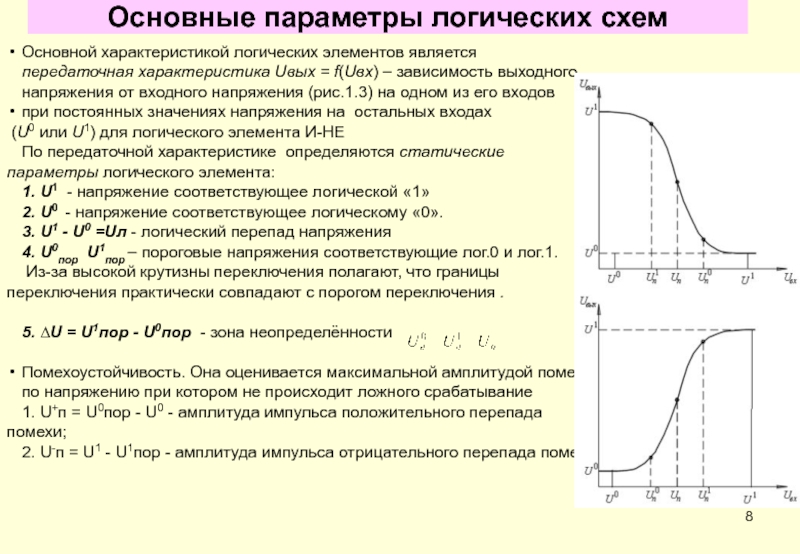

Основной характеристикой логических элементов является передаточная характеристика

Uвых = f(Uвх) – зависимость выходного напряжения от входного напряжения (рис.1.3) на одном из

его входов

при постоянных значениях напряжения на остальных входах

(U0 или U1) для логического элемента И-НЕ

По передаточной характеристике определяются статические параметры логического элемента:

1. U1 - напряжение соответствующее логической «1»

2. U0 - напряжение соответствующее логическому «0».

3. U1 - U0 =Uл - логический перепад напряжения

4. U0пор U1пор – пороговые напряжения соответствующие лог.0 и лог.1.

Из-за высокой крутизны переключения полагают, что границы переключения практически совпадают с порогом переключения .

5. ∆U = U1пор - U0пор - зона неопределённости

Помехоустойчивость. Она оценивается максимальной амплитудой помехи по напряжению при котором не происходит ложного срабатывание

1. U+п = U0пор - U0 - амплитуда импульса положительного перепада помехи;

2. U-п = U1 - U1пор - амплитуда импульса отрицательного перепада помехи

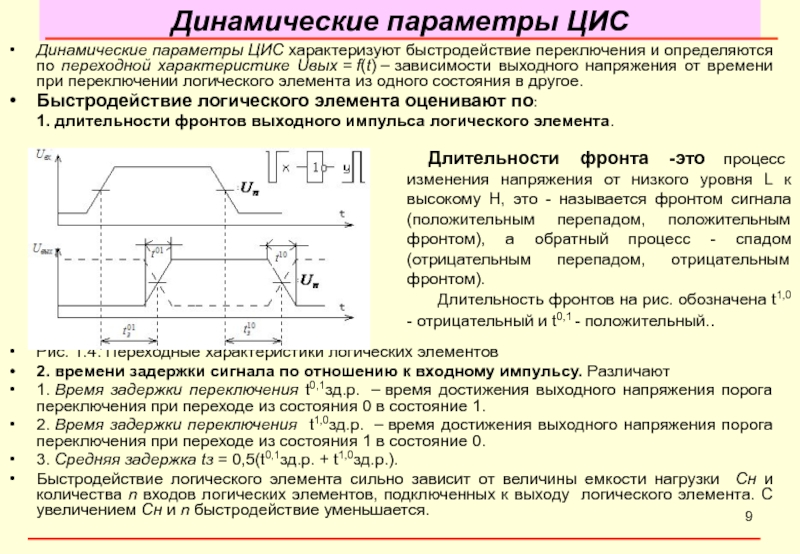

Слайд 9Динамические параметры ЦИС

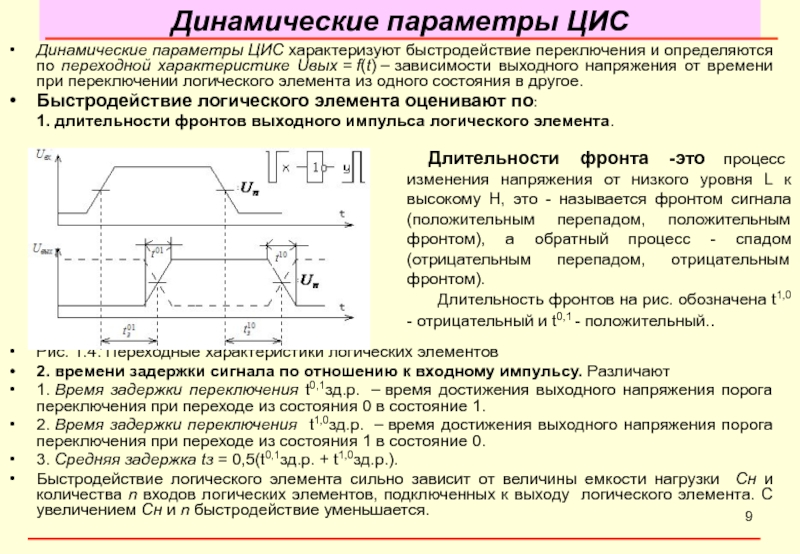

Динамические параметры ЦИС характеризуют быстродействие переключения и определяются

по переходной характеристике Uвых = f(t) – зависимости выходного напряжения от времени при переключении

логического элемента из одного состояния в другое.

Быстродействие логического элемента оценивают по:

1. длительности фронтов выходного импульса логического элемента.

Рис. 1.4. Переходные характеристики логических элементов

2. времени задержки сигнала по отношению к входному импульсу. Различают

1. Время задержки переключения t0,1зд.р. – время достижения выходного напряжения порога переключения при переходе из состояния 0 в состояние 1.

2. Время задержки переключения t1,0зд.р. – время достижения выходного напряжения порога переключения при переходе из состояния 1 в состояние 0.

3. Средняя задержка tз = 0,5(t0,1зд.р. + t1,0зд.р.).

Быстродействие логического элемента сильно зависит от величины емкости нагрузки Сн и количества n входов логических элементов, подключенных к выходу логического элемента. С увеличением Сн и n быстродействие уменьшается.

Длительности фронта -это процесс изменения напряжения от низкого уровня L к высокому H, это - называется фронтом сигнала (положительным перепадом, положительным фронтом), а обратный процесс - спадом (отрицательным перепадом, отрицательным фронтом).

Длительность фронтов на рис. обозначена t1,0 - отрицательный и t0,1 - положительный..

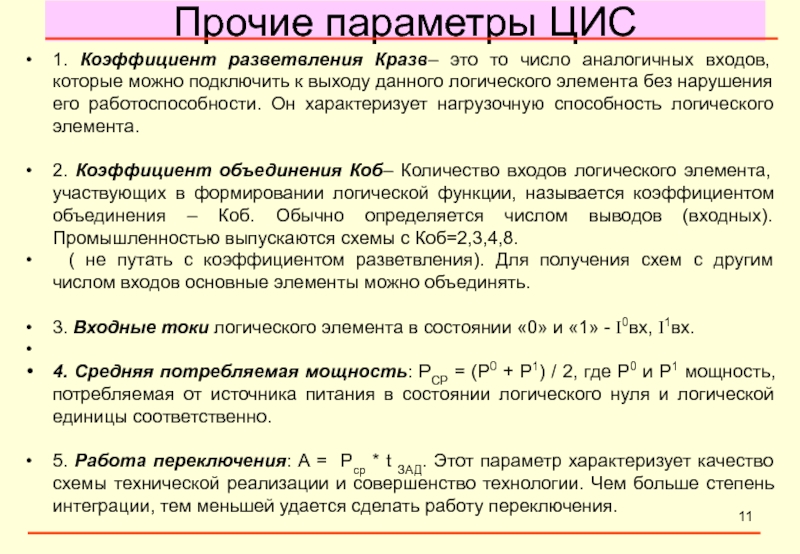

Слайд 11

Прочие параметры ЦИС

1. Коэффициент разветвления Кразв– это то число аналогичных

входов, которые можно подключить к выходу данного логического элемента без

нарушения его работоспособности. Он характеризует нагрузочную способность логического элемента.

2. Коэффициент объединения Коб– Количество входов логического элемента, участвующих в формировании логической функции, называется коэффициентом объединения – Коб. Обычно определяется числом выводов (входных). Промышленностью выпускаются схемы с Коб=2,3,4,8.

( не путать с коэффициентом разветвления). Для получения схем с другим числом входов основные элементы можно объединять.

3. Входные токи логического элемента в состоянии «0» и «1» - I0вх, I1вх.

4. Средняя потребляемая мощность: PСР = (P0 + P1) / 2, где Р0 и Р1 мощность, потребляемая от источника питания в состоянии логического нуля и логической единицы соответственно.

5. Работа переключения: А = Pср * t ЗАД. Этот параметр характеризует качество схемы технической реализации и совершенство технологии. Чем больше степень интеграции, тем меньшей удается сделать работу переключения.

Слайд 12Если на обоих входах Х1, Х2 присутствуют сигналы логических единиц,

транзистор VT1 открывается током базы, протекающим по цепи: плюс источника питания,

резистор R1, диоды VD3,VD4, переход база-эмиттер транзистора VT1, минус источника. На выходе элемента будет напряжение 0,1-0,2 В, что соответствует логическому нулю.

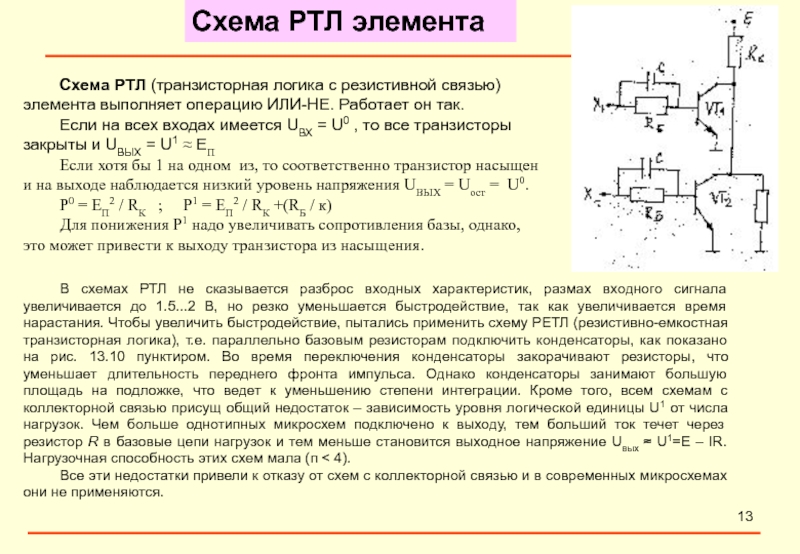

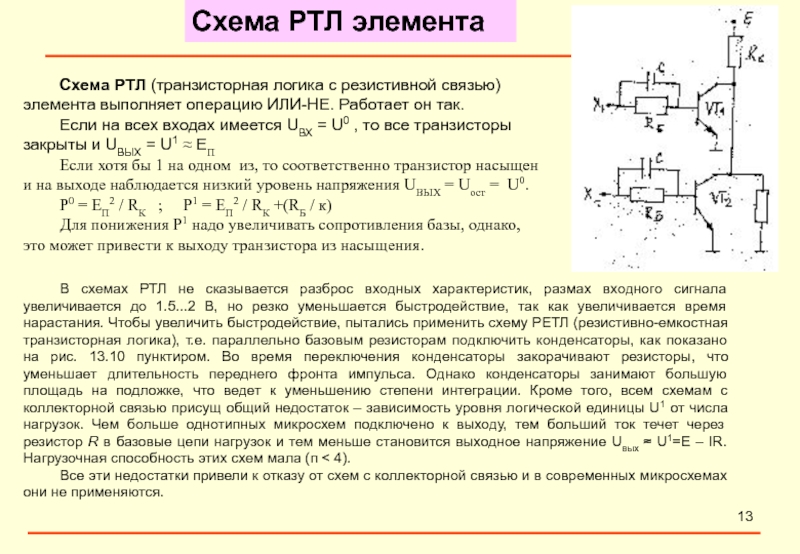

Слайд 13Схема РТЛ (транзисторная логика с резистивной связью) элемента выполняет операцию

ИЛИ-НЕ. Работает он так.

Если на всех входах имеется UВХ

= U0 , то все транзисторы закрыты и UВЫХ = U1 ЕП

Если хотя бы 1 на одном из, то соответственно транзистор насыщен и на выходе наблюдается низкий уровень напряжения UВЫХ = Uост = U0.

P0 = ЕП2 / RК ; P1 = ЕП2 / RК +(RБ / к)

Для понижения P1 надо увеличивать сопротивления базы, однако, это может привести к выходу транзистора из насыщения.

В схемах РТЛ не сказывается разброс входных характеристик, размах входного сигнала увеличивается до 1.5...2 В, но резко уменьшается быстродействие, так как увеличивается время нарастания. Чтобы увеличить быстродействие, пытались применить схему РЕТЛ (резистивно-емкостная транзисторная логика), т.е. параллельно базовым резисторам подключить конденсаторы, как показано на рис. 13.10 пунктиром. Во время переключения конденсаторы закорачивают резисторы, что уменьшает длительность переднего фронта импульса. Однако конденсаторы занимают большую площадь на подложке, что ведет к уменьшению степени интеграции. Кроме того, всем схемам с коллекторной связью присущ общий недостаток – зависимость уровня логической единицы U1 от числа нагрузок. Чем больше однотипных микросхем подключено к выходу, тем больший ток течет через резистор R в базовые цепи нагрузок и тем меньше становится выходное напряжение Uвых ≈ U1=Е – IR. Нагрузочная способность этих схем мала (п < 4).

Все эти недостатки привели к отказу от схем с коллекторной связью и в современных микросхемах они не применяются.

Схема РТЛ элемента

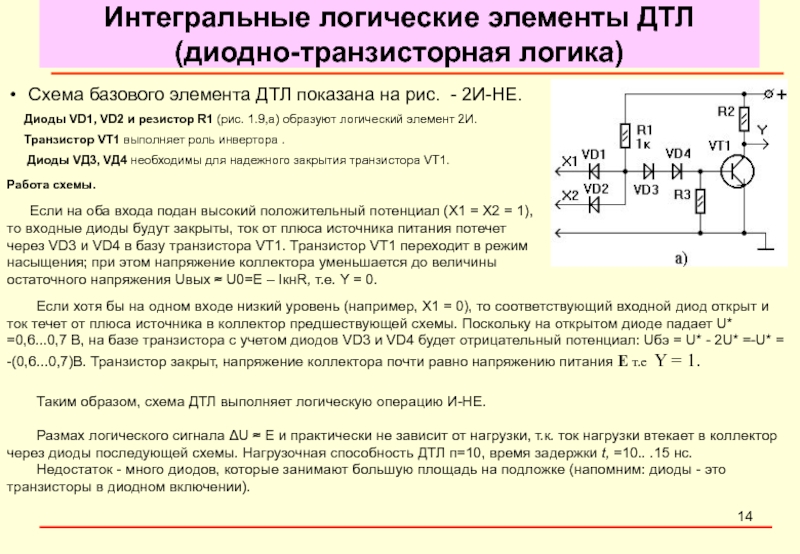

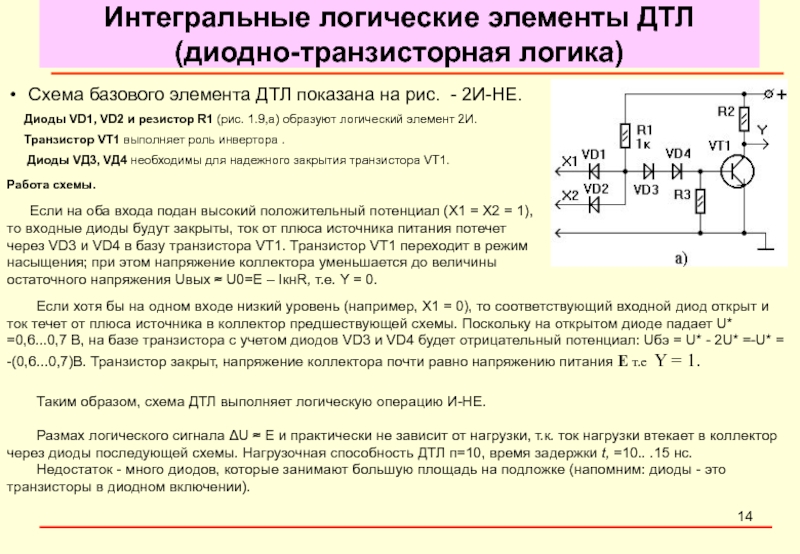

Слайд 14Интегральные логические элементы ДТЛ (диодно-транзисторная логика)

Схема базового элемента ДТЛ показана

на рис. - 2И-НЕ.

Диоды VD1, VD2 и резистор R1 (рис.

1.9,а) образуют логический элемент 2И.

Транзистор VT1 выполняет роль инвертора .

Диоды VД3, VД4 необходимы для надежного закрытия транзистора VТ1.

Работа схемы.

Если на оба входа подан высокий положительный потенциал (X1 = X2 = 1), то входные диоды будут закрыты, ток от плюса источника питания потечет через VD3 и VD4 в базу транзистора VT1. Транзистор VT1 переходит в режим насыщения; при этом напряжение коллектора уменьшается до величины остаточного напряжения Uвых ≈ U0=Е – IкнR, т.е. Y = 0.

Если хотя бы на одном входе низкий уровень (например, X1 = 0), то соответствующий входной диод открыт и ток течет от плюса источника в коллектор предшествующей схемы. Поскольку на открытом диоде падает U* =0,6...0,7 В, на базе транзистора с учетом диодов VD3 и VD4 будет отрицательный потенциал: Uбэ = U* - 2U* =-U* = -(0,6...0,7)В. Транзистор закрыт, напряжение коллектора почти равно напряжению питания Е т.е Y = 1.

Таким образом, схема ДТЛ выполняет логическую операцию И-НЕ.

Размах логического сигнала ΔU ≈ Е и практически не зависит от нагрузки, т.к. ток нагрузки втекает в коллектор через диоды последующей схемы. Нагрузочная способность ДТЛ п=10, время задержки t, =10.. .15 нс.

Недостаток - много диодов, которые занимают большую площадь на подложке (напомним: диоды - это транзисторы в диодном включении).

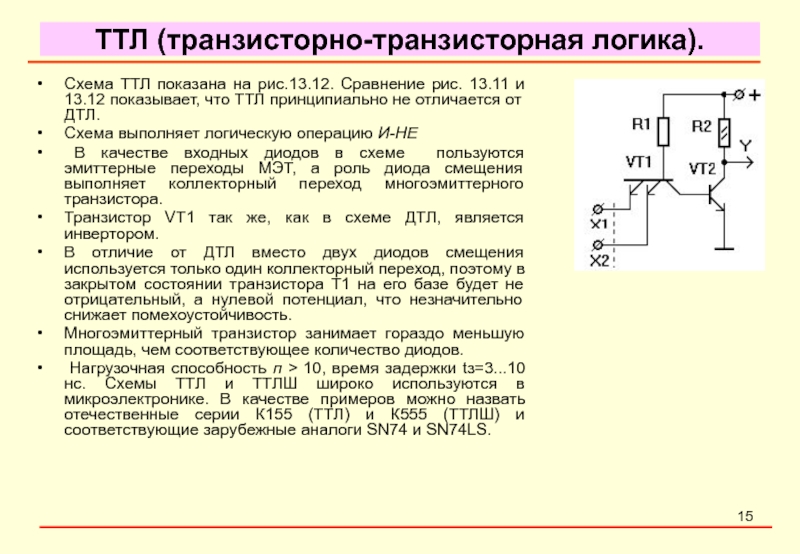

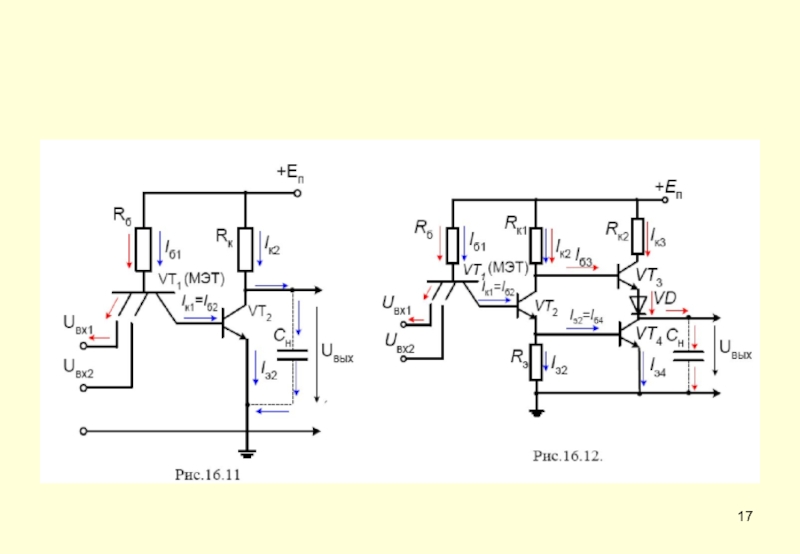

Слайд 15ТТЛ (транзисторно-транзисторная логика).

Схема ТТЛ показана на рис.13.12. Сравнение рис. 13.11

и 13.12 показывает, что ТТЛ принципиально не отличается от ДТЛ.

Схема выполняет логическую операцию И-НЕ

В качестве входных диодов в схеме пользуются эмиттерные переходы МЭТ, а роль диода смещения выполняет коллекторный переход многоэмиттерного транзистора.

Транзистор VT1 так же, как в схеме ДТЛ, является инвертором.

В отличие от ДТЛ вместо двух диодов смещения используется только один коллекторный переход, поэтому в закрытом состоянии транзистора T1 на его базе будет не отрицательный, а нулевой потенциал, что незначительно снижает помехоустойчивость.

Многоэмиттерный транзистор занимает гораздо меньшую площадь, чем соответствующее количество диодов.

Нагрузочная способность п > 10, время задержки tз=3...10 нс. Схемы ТТЛ и ТТЛШ широко используются в микроэлектронике. В качестве примеров можно назвать отечественные серии К155 (ТТЛ) и К555 (ТТЛШ) и соответствующие зарубежные аналоги SN74 и SN74LS.

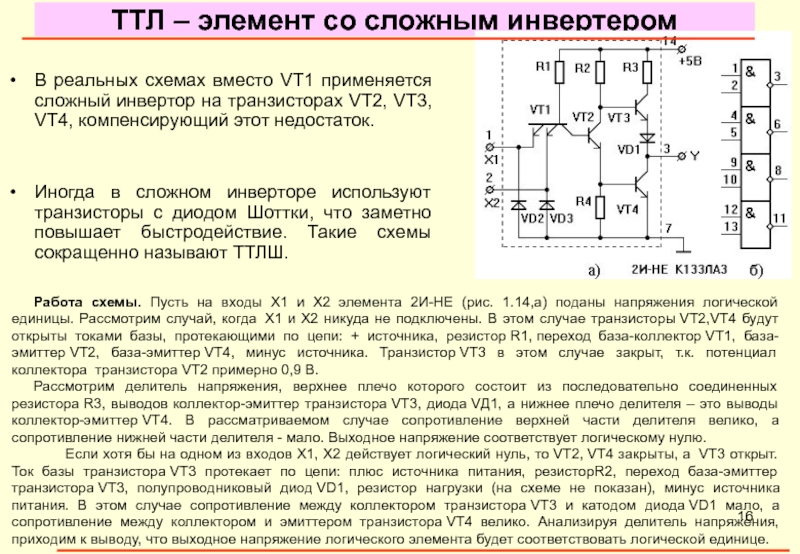

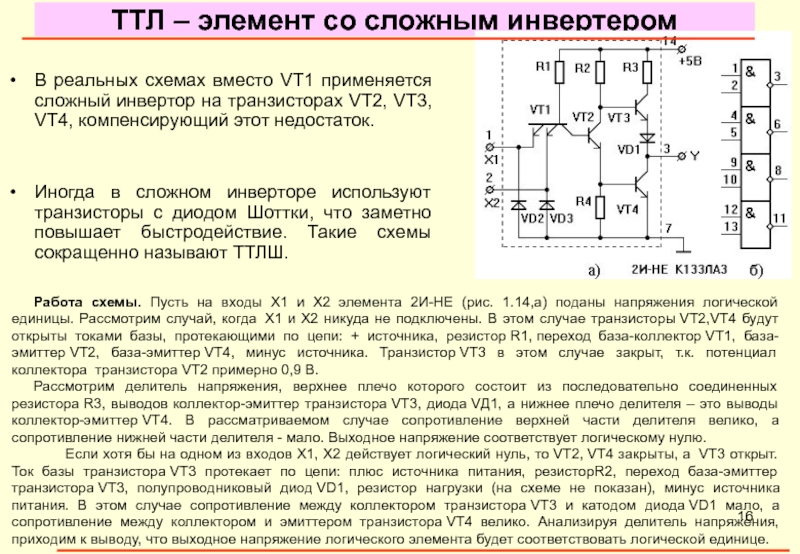

Слайд 16ТТЛ – элемент со сложным инвертером

В реальных схемах вместо VT1

применяется сложный инвертор на транзисторах VT2, VT3, VT4, компенсирующий этот

недостаток.

Иногда в сложном инверторе используют транзисторы с диодом Шоттки, что заметно повышает быстродействие. Такие схемы сокращенно называют ТТЛШ.

Работа схемы. Пусть на входы Х1 и Х2 элемента 2И-НЕ (рис. 1.14,а) поданы напряжения логической единицы. Рассмотрим случай, когда Х1 и Х2 никуда не подключены. В этом случае транзисторы VТ2,VТ4 будут открыты токами базы, протекающими по цепи: + источника, резистор R1, переход база-коллектор VТ1, база-эмиттер VТ2, база-эмиттер VТ4, минус источника. Транзистор VТ3 в этом случае закрыт, т.к. потенциал коллектора транзистора VT2 примерно 0,9 В.

Рассмотрим делитель напряжения, верхнее плечо которого состоит из последовательно соединенных резистора R3, выводов коллектор-эмиттер транзистора VТ3, диода VД1, а нижнее плечо делителя – это выводы коллектор-эмиттер VТ4. В рассматриваемом случае сопротивление верхней части делителя велико, а сопротивление нижней части делителя - мало. Выходное напряжение соответствует логическому нулю.

Если хотя бы на одном из входов Х1, Х2 действует логический нуль, то VТ2, VТ4 закрыты, а VТ3 открыт. Ток базы транзистора VT3 протекает по цепи: плюс источника питания, резисторR2, переход база-эмиттер транзистора VT3, полупроводниковый диод VD1, резистор нагрузки (на схеме не показан), минус источника питания. В этом случае сопротивление между коллектором транзистора VT3 и катодом диода VD1 мало, а сопротивление между коллектором и эмиттером транзистора VT4 велико. Анализируя делитель напряжения, приходим к выводу, что выходное напряжение логического элемента будет соответствовать логической единице.

Слайд 18Логический элемент НЕ (инвертор) с тремя состояниями

В вычислительной технике широко

применяется устройство с тремя состояниями на выходе. Рассмотрим логический элемент

НЕ (инвертор) с тремя состояниями на выходе (рис. 1.16,а). Указанный инвертор легко получается из схемы базового логического элемента 2И-НЕ путем добавления в схему VД2.

Если на вход разрешения V микросхемы подано напряжение логической «1», то диод VД2 оказывается отключенным от схемы, и данный элемент можно рассматривать как логический элемент НЕ. Если на входе Х логическая единица, то транзисторы VT2, VT4 будут открыты, транзистор VT3 закрыт и на выходе элемента будет сигнал логического нуля. Подадим на вход Х сигнал логического нуля. В этом случае транзисторы VT2, VT4 будут закрыты, транзистор VT3 открыт и на выходе элемента будет сигнал логической единицы.

Подадим на вход V напряжение логического «0» , в этом случае окажутся закрытыми VТ2, VТ3, VТ4. Выход Y оказывается отключенным как от плюсового, так и от минусового проводов источника питания. Говорят, что выход элемента находится в третьем высокоимпедансном состоянии (состояние высокого сопротивления, как от клеммы «+», так и от клеммы «-» источника питания). Элементы с тремя состояниями позволяют организовать в компьютерных системах так называемую общую шину.

Элементы с тремя состояниями входят в состав шинных формирователей. Шинные формирователи это устройства, которые обеспечивают передачу сигнала в двух направлениях по одному и тому же проводу. В составе шинного формирователя на каждую линию потребуется 2 элемента с тремя состояниями на выходе.

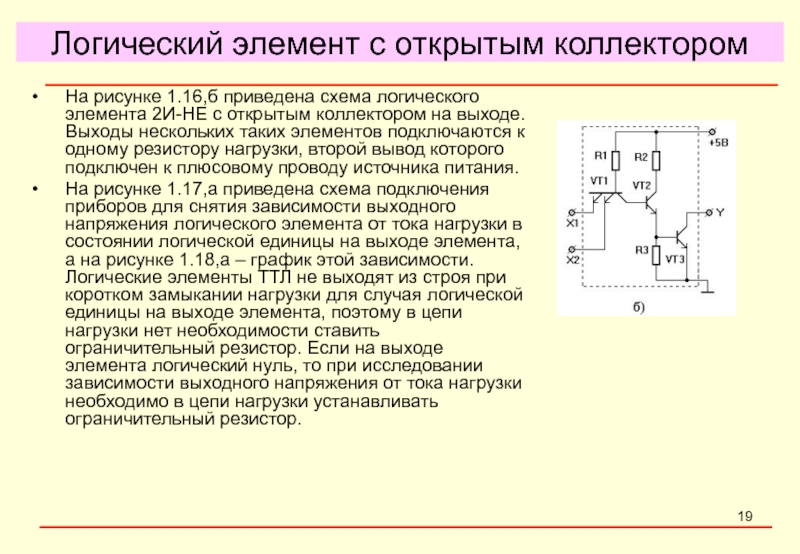

Слайд 19Логический элемент с открытым коллектором

На рисунке 1.16,б приведена схема логического

элемента 2И-НЕ с открытым коллектором на выходе. Выходы нескольких таких

элементов подключаются к одному резистору нагрузки, второй вывод которого подключен к плюсовому проводу источника питания.

На рисунке 1.17,а приведена схема подключения приборов для снятия зависимости выходного напряжения логического элемента от тока нагрузки в состоянии логической единицы на выходе элемента, а на рисунке 1.18,а – график этой зависимости. Логические элементы ТТЛ не выходят из строя при коротком замыкании нагрузки для случая логической единицы на выходе элемента, поэтому в цепи нагрузки нет необходимости ставить ограничительный резистор. Если на выходе элемента логический нуль, то при исследовании зависимости выходного напряжения от тока нагрузки необходимо в цепи нагрузки устанавливать ограничительный резистор.

Слайд 20

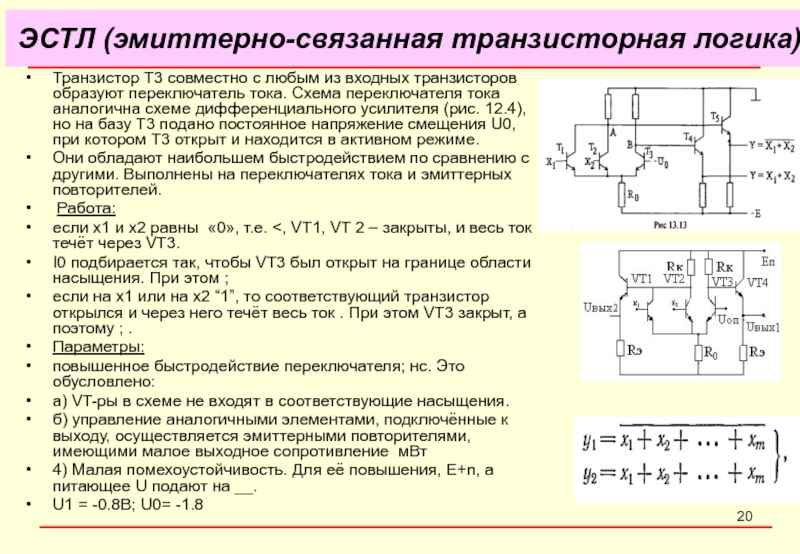

ЭСТЛ (эмиттерно-связанная транзисторная логика)

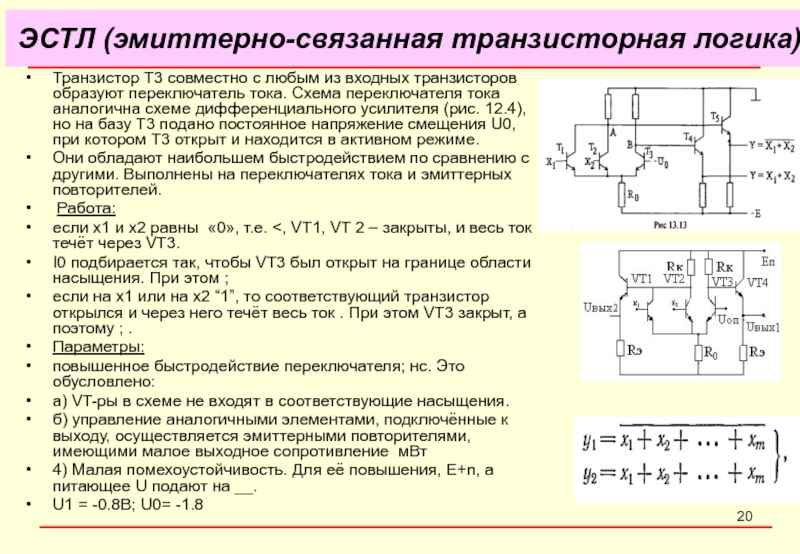

Транзистор Т3 совместно с любым из входных

транзисторов образуют переключатель тока. Схема переключателя тока аналогична схеме дифференциального

усилителя (рис. 12.4), но на базу Т3 подано постоянное напряжение смещения U0, при котором Т3 открыт и находится в активном режиме.

Они обладают наибольшем быстродействием по сравнению с другими. Выполнены на переключателях тока и эмиттерных повторителей.

Работа:

если х1 и х2 равны «0», т.е. <, VT1, VT 2 – закрыты, и весь ток течёт через VT3.

I0 подбирается так, чтобы VT3 был открыт на границе области насыщения. При этом ;

если на х1 или на х2 “1”, то соответствующий транзистор открылся и через него течёт весь ток . При этом VT3 закрыт, а поэтому ; .

Параметры:

повышенное быстродействие переключателя; нс. Это обусловлено:

а) VT-ры в схеме не входят в соответствующие насыщения.

б) управление аналогичными элементами, подключённые к выходу, осуществляется эмиттерными повторителями, имеющими малое выходное сопротивление мВт

4) Малая помехоустойчивость. Для её повышения, E+n, а питающее U подают на __.

U1 = -0.8В; U0= -1.8

Слайд 21

Логические элементы с инжекционным питанием И2Л)

13.7. Транзисторные логические элементы с

инжекционным питанием (ТЛИП) называют также инжекционной интегральной логикой, откуда возникло

общепринятое сокращение И2Л. Элементы ТЛИП в дискретном исполнении неизвестны, и реализуются в больших интегральных схемах (БИС). Принцип работы ТЛИП поясняется рис. 13.14.

Транзисторы Т0 и Т2 - это простейший клапан (инвертор) с инжекционным питанием, a Т1 и Т3 относятся к предыдущей и последующей схемам. Транзистор Т0 с проводимостью р-п-р выполняет роль генератора тока, питающего цепь базы n -р- n -транзистора T2. Ток Iи создается инжекцией дырок из эмиттера р-n-р-транзистора, поэтому называется током инжекции, а сам эмиттер называют инжектором. Питание схемы через инжектор (т.е. без резисторов в цепи питания) позволяет существенно уменьшить напряжение питания. Из рис 13.14 видно, что напряжение питания равно падению напряжения на инжекторном переходе Е = U* = 0,6В. По некоторым причинам в реальных схемах Е = 1...1,5 В.

Пусть на входе (на базе Т2) низкий потенциал (T1 открыт). Тогда ток коллектора транзистора Т0, равный αIи, замыкается через Т1 и не течет в базу Т2. Транзистор Т2 закрыт и на выходе инвертора (на базе Т3) будет высокий потенциал, т.е. выполняется логическая операция НЕ. Обычно параллельно соединяются несколько инверторов, тогда реализуется логическая операция ИЛИ-НЕ.

В схеме рис. 13.14 базы всех р-п-р-транзисторов заземлены, а эмиттеры подключены к шине +Е, поэтому в реальной схеме ТЛИП вместо нескольких р-п-р-транзисторов используют один многоколлекторный р- n -р-транзистор. Для развязки выходов, подключаемых к отдельным нагрузкам, n-р- n -транзисторы тоже делают многоколлекторными. В результате схема приобретает вид рис.13.15. Каждый из коллекторных токов р- n -р-транзистора равен:I*=αIи/n ≈ Iи/n.

Конструктивно-технологическое своеобразие ТЛИП состоит в высокой степени интеграции. Это достигается тем, что примыкающая к подложке п-область выполняет роль и базы р-п-р-транзистора и эмиттеров всех п-р-п-транзисторов; базой п-р-п- и коллекторм р-п-р-транзисторов является общая р-область. Разрез структуры ТЛИП показан на рис. 13.16.

Достоинствами ТЛИП являются: низкое напряжение питания; малая потребляемая мощность; высокая плотность упаковки; не нужны диэлектрические карманы и разделительная диффузия.

Слайд 22

Логические элементы на МДП-транзисторах

Ключ на МДП-транзисторах можно выполнить с резистивной

нагрузкой, подобно ключу на биполярных транзисторах, но технологически целесообразнее применять

так называемую динамическую нагрузку. Схема ключа показана на рис. 13.17. В качестве сопротивления нагрузки используется нагрузочный МДП-транзистор, затвор которого соединяется с истоком, т.е. Uзи2 =Uси2.

Из рис. 13.17 видно, что точки, соответствующие равным напряжениям стока и затвора, образуют линию, которая является вольтамперной характеристикой нагрузочного транзистора. На рис. 13.18 показано, как нанести линию нагрузки на семейство стоковых характеристик активного транзистора Т1.

Нагрузочный транзистор T2 работает на пологом участке стоковой характеристики, поэтому его вольтамперную характеристику запишем в виде:

Iс =0,5b(Ucи2 –U02)2, (13.6)

где b - удельная крутизна транзистора, U02 - напряжение отсечки нагрузочного транзистора. Из рис. 13.17 видно, что Ucи2=E - Ucи1.

Если на входе низкий уровень Uзи1< U01, то нижний транзистор закрыт и ток стока равен нулю. Тогда на выходе ключа будет максимальное напряжение

Uвых мах= Ucи1=E - Ucи2

Если на вход подан высокий уровень напряжения Uзи1>U01 то Т1 открыт, его сопротивление мало и все напряжение питания падает на верхнем транзисторе. Подставляя в (13.6) Ucи2=E найдем ток стока насыщения:

Iси =0,5b(Е –U02)2,

Выходное напряжение при этом будет минимальным (остаточное напряжение). Его можно найти, умножив (13.8) на сопротивление канала. При обычных значениях параметров транзисторов остаточное напряжение составляет 50… 150мВ.

При последовательном соединении нескольких активных транзисторов получим логический элемент И-НЕ (рис.13.19а). Параллельное соединение активных транзисторов позволяет выполнить логическую операцию ИЛИ-НЕ (рис.13.196) Наиболее часто используют логические схемы на МДП-транзисторах с индуцированным n- каналом.

Поскольку входной ток МДП-транзистора практически равен нулщ, логические уровни не зависят от нагрузки. Нагрузочная способность ограничивается только влиянием емкостей затвор-исток, т.е. уменьшением быстродействия.

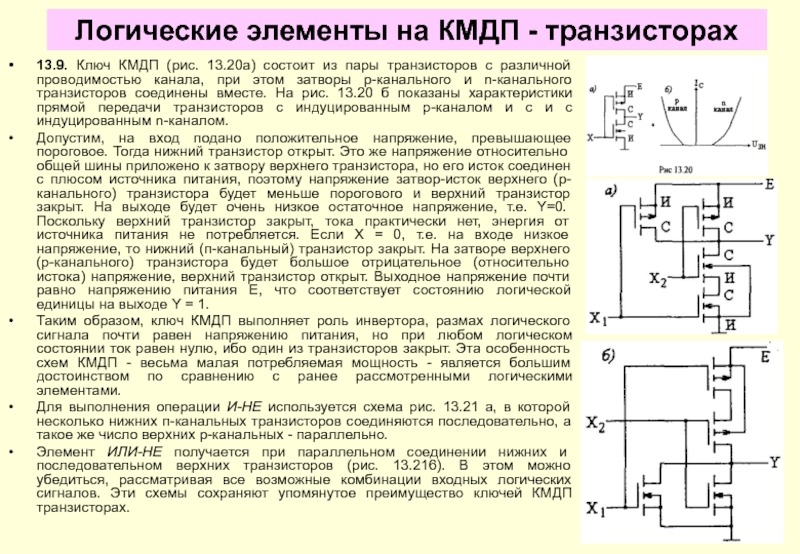

Слайд 23Логические элементы на КМДП - транзисторах

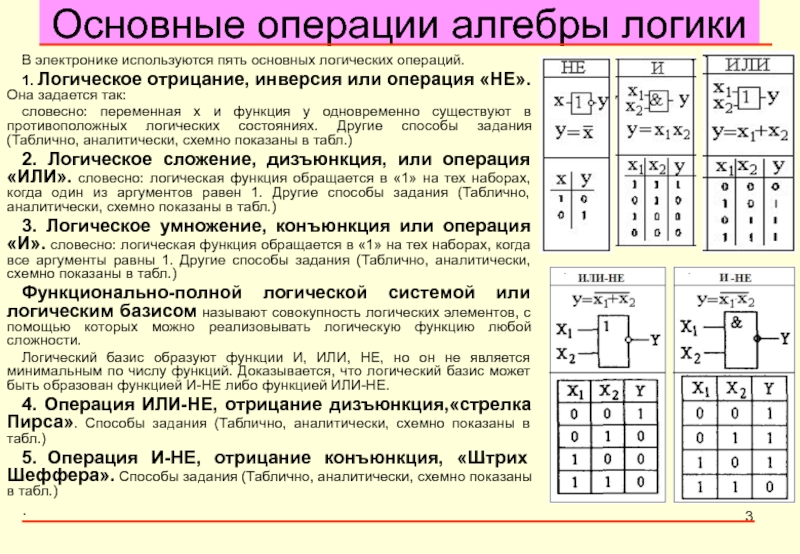

13.9. Ключ КМДП (рис. 13.20а)

состоит из пары транзисторов с различной проводимостью канала, при этом

затворы р-канального и n-канального транзисторов соединены вместе. На рис. 13.20 б показаны характеристики прямой передачи транзисторов с индуцированным р-каналом и с и с индуцированным n-каналом.

Допустим, на вход подано положительное напряжение, превышающее пороговое. Тогда нижний транзистор открыт. Это же напряжение относительно общей шины приложено к затвору верхнего транзистора, но его исток соединен с плюсом источника питания, поэтому напряжение затвор-исток верхнего (р-канального) транзистора будет меньше порогового и верхний транзистор закрыт. На выходе будет очень низкое остаточное напряжение, т.е. Y=0. Поскольку верхний транзистор закрыт, тока практически нет, энергия от источника питания не потребляется. Если Х = 0, т.е. на входе низкое напряжение, то нижний (п-канальный) транзистор закрыт. На затворе верхнего (р-канального) транзистора будет большое отрицательное (относительно истока) напряжение, верхний транзистор открыт. Выходное напряжение почти равно напряжению питания E, что соответствует состоянию логической единицы на выходе Y = 1.

Таким образом, ключ КМДП выполняет роль инвертора, размах логического сигнала почти равен напряжению питания, но при любом логическом состоянии ток равен нулю, ибо один из транзисторов закрыт. Эта особенность схем КМДП - весьма малая потребляемая мощность - является большим достоинством по сравнению с ранее рассмотренными логическими элементами.

Для выполнения операции И-НЕ используется схема рис. 13.21 а, в которой несколько нижних п-канальных транзисторов соединяются последовательно, а такое же число верхних р-канальных - параллельно.

Элемент ИЛИ-НЕ получается при параллельном соединении нижних и последовательном верхних транзисторов (рис. 13.216). В этом можно убедиться, рассматривая все возможные комбинации входных логических сигналов. Эти схемы сохраняют упомянутое преимущество ключей КМДП транзисторах.