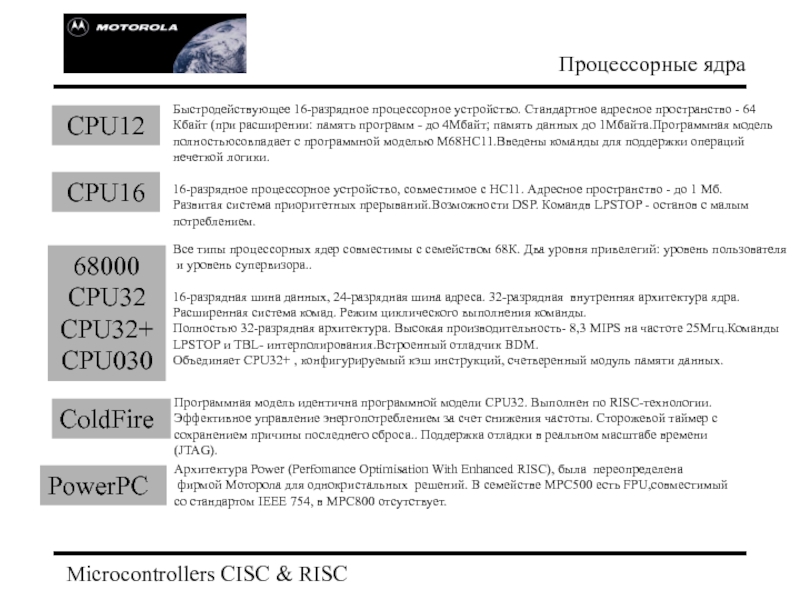

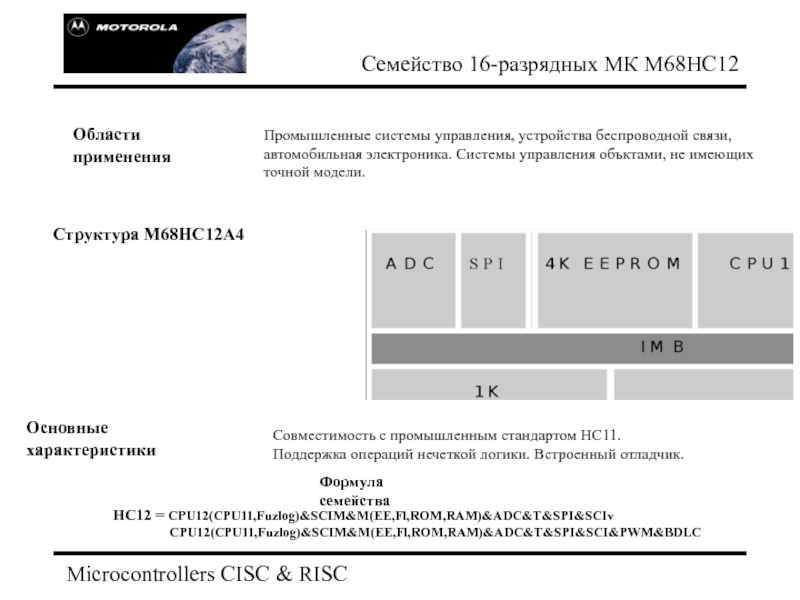

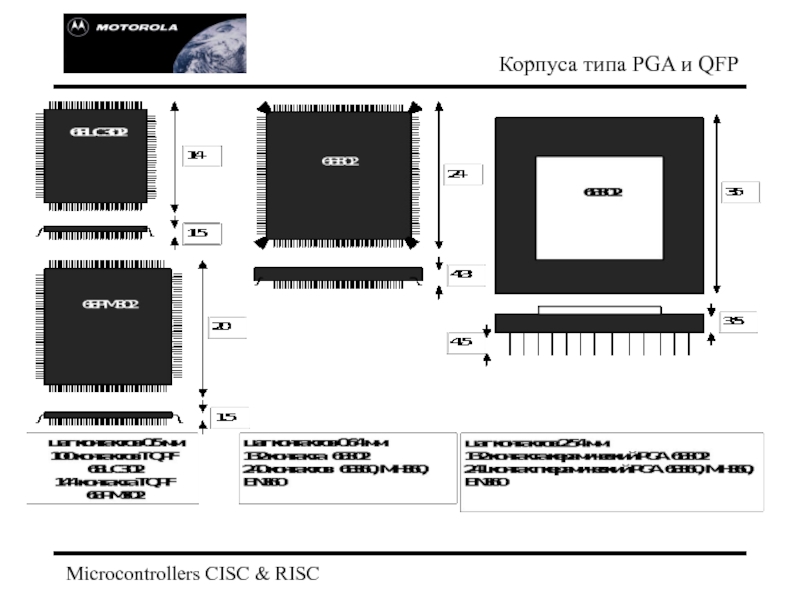

пространство - 64 Кбайт (при расширении: память программ - до

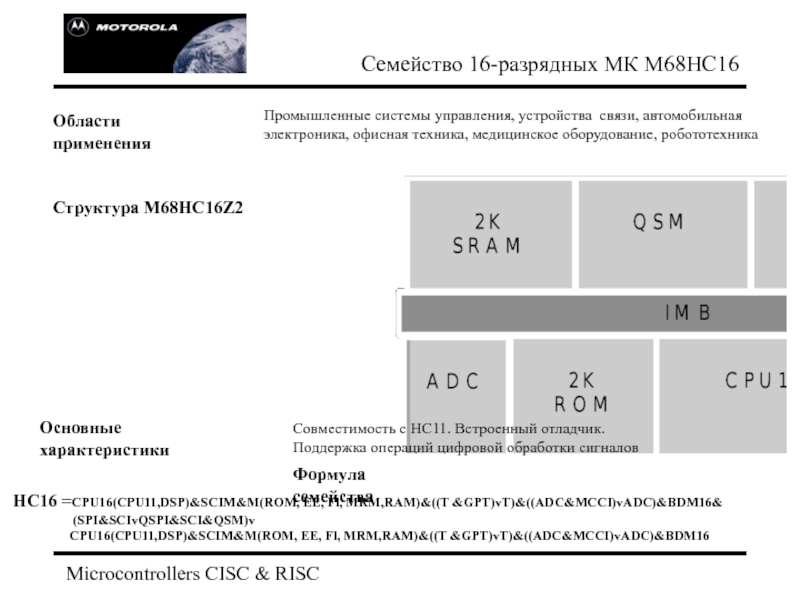

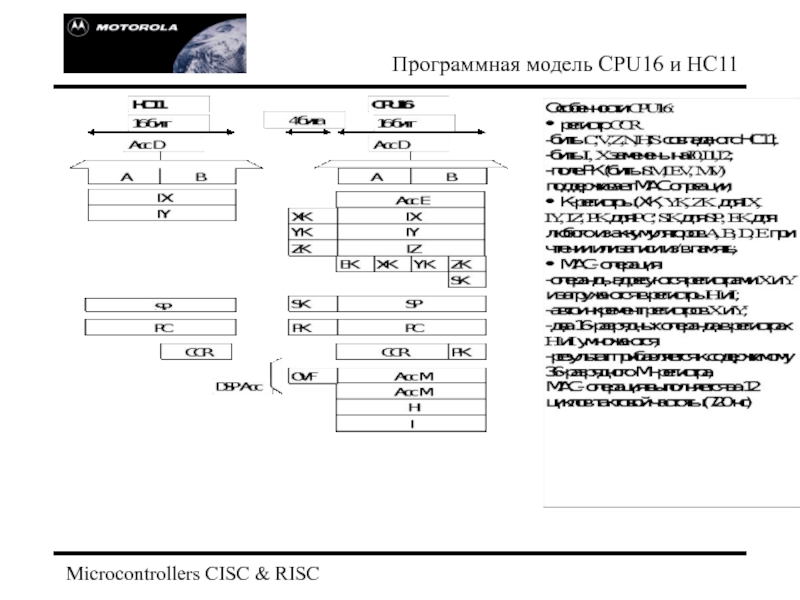

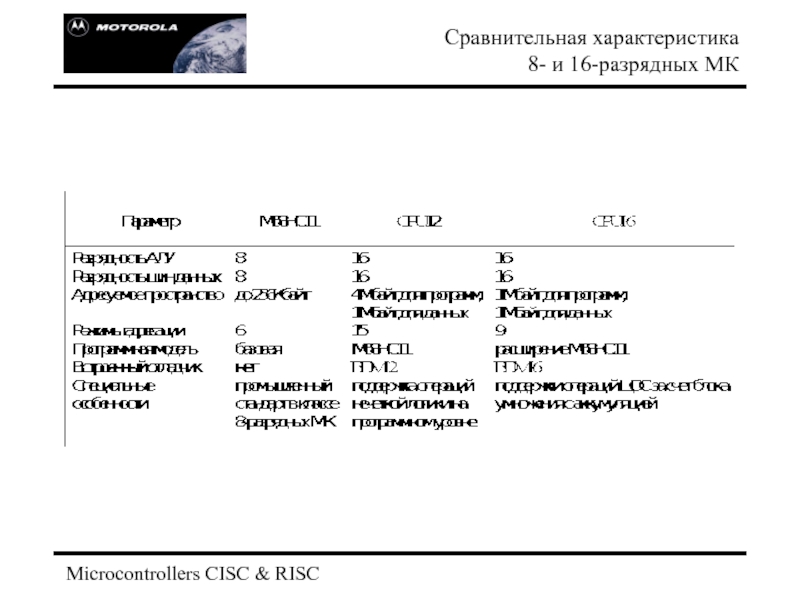

4Мбайт; память данных до 1Мбайта.Программная модель полностьюсовпадает с программной моделью М68НС11.Введены команды для поддержки операций нечеткой логики.16-разрядное процессорное устройство, совместимое с НС11. Адресное пространство - до 1 Мб.

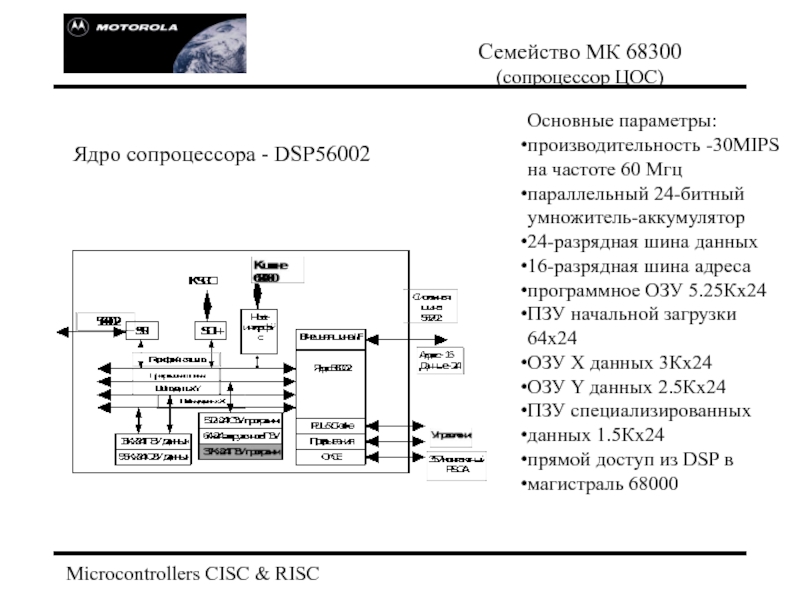

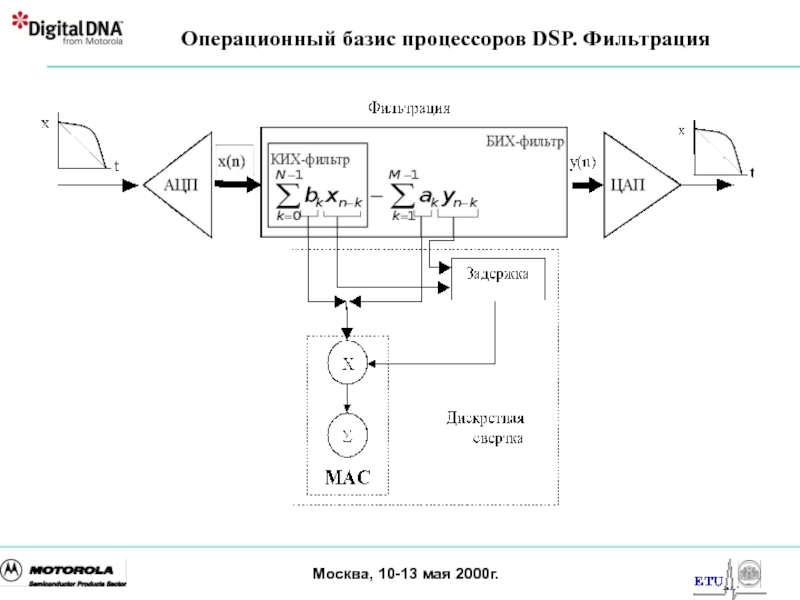

Развитая система приоритетных прерываний.Возможности DSP. Командв LPSTOP - останов с малым

потреблением.

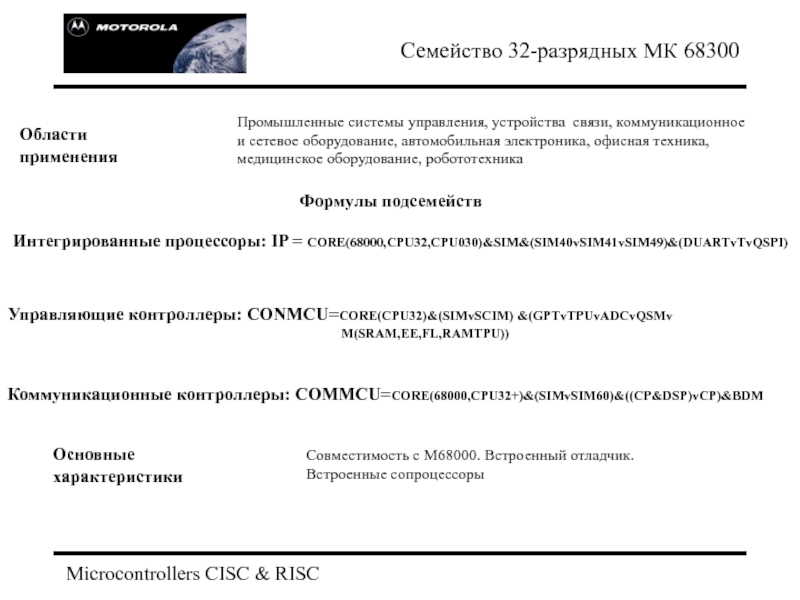

Все типы процессорных ядер совместимы с семейством 68К. Два уровня привелегий: уровень пользователя

и уровень супервизора..

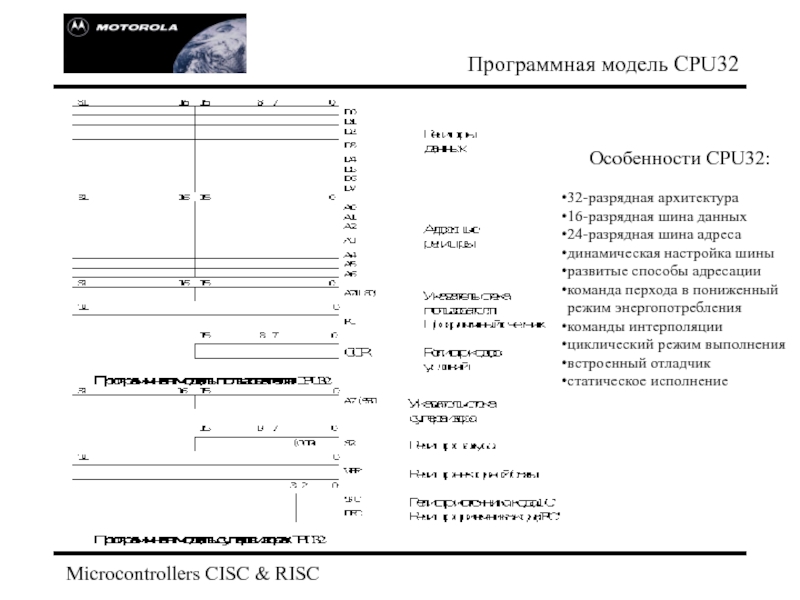

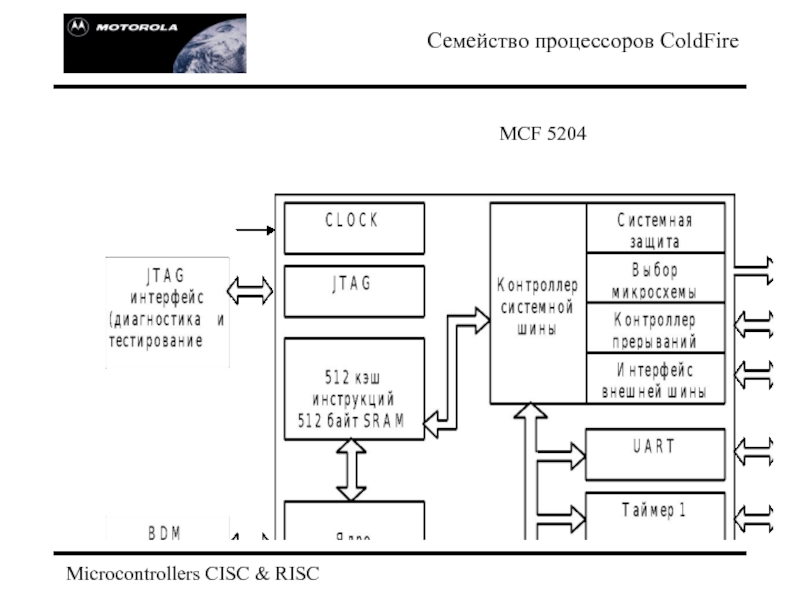

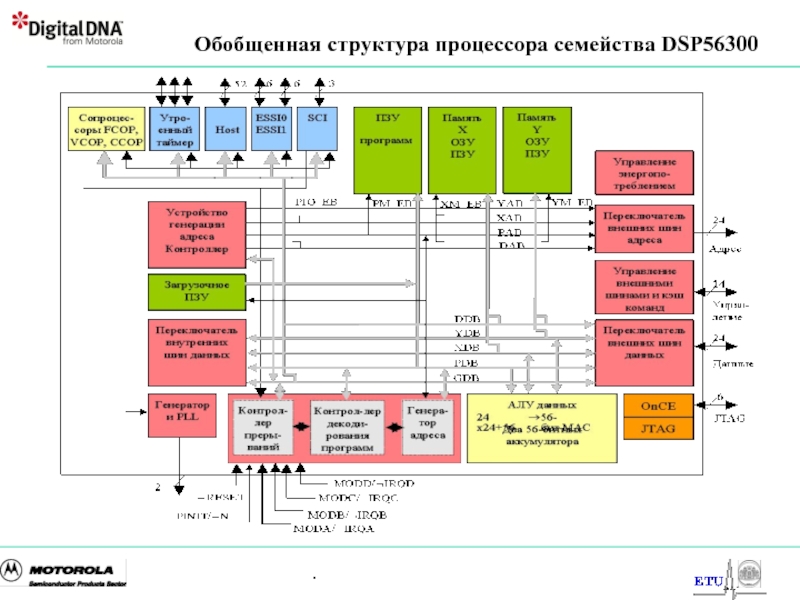

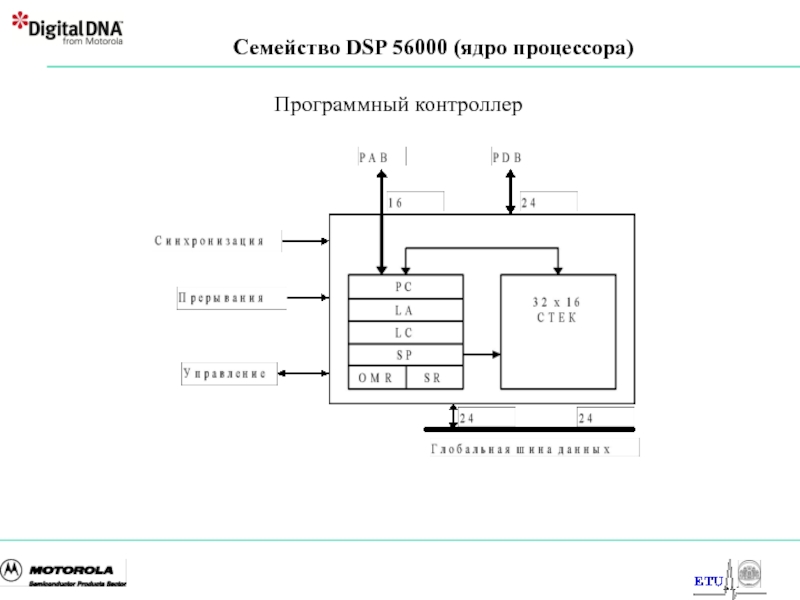

16-разрядная шина данных, 24-разрядная шина адреса. 32-разрядная внутренняя архитектура ядра. Расширенная система комад. Режим циклического выполнения команды.

Полностью 32-разрядная архитектура. Высокая производительность- 8,3 MIPS на частоте 25Мгц.Команды

LPSTOP и TBL- интерполирования.Встроенный отладчик BDM.

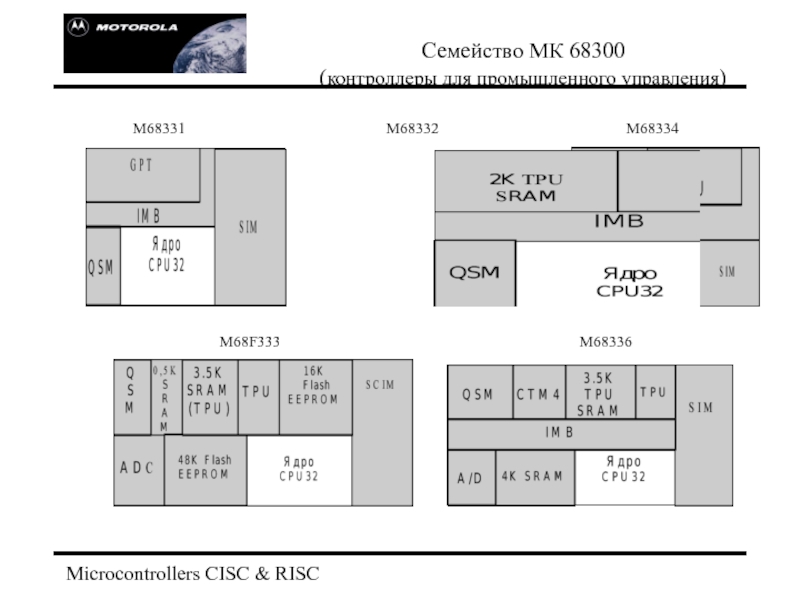

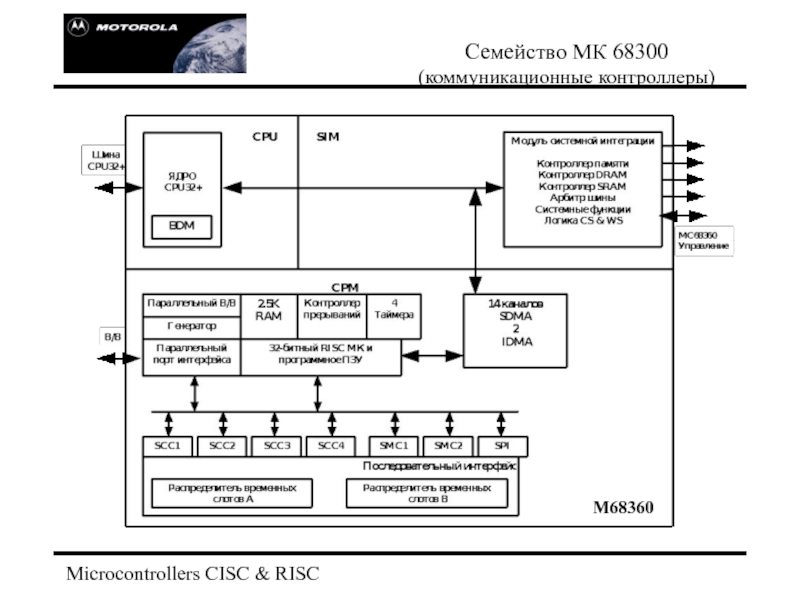

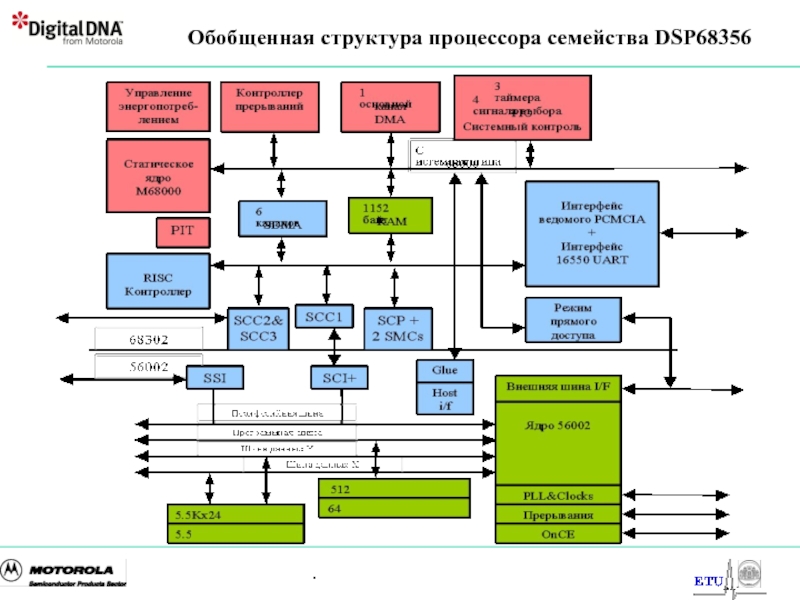

Объединяет CPU32+ , конфигурируемый кэш инструкций, счетверенный модуль памяти данных.

Программная модель идентична программной модели CPU32. Выполнен по RISC-технологии.

Эффективное управление энергопотреблением за счет снижения частоты. Сторожевой таймер с сохранением причины последнего сброса.. Поддержка отладки в реальном масштабе времени (JTAG).

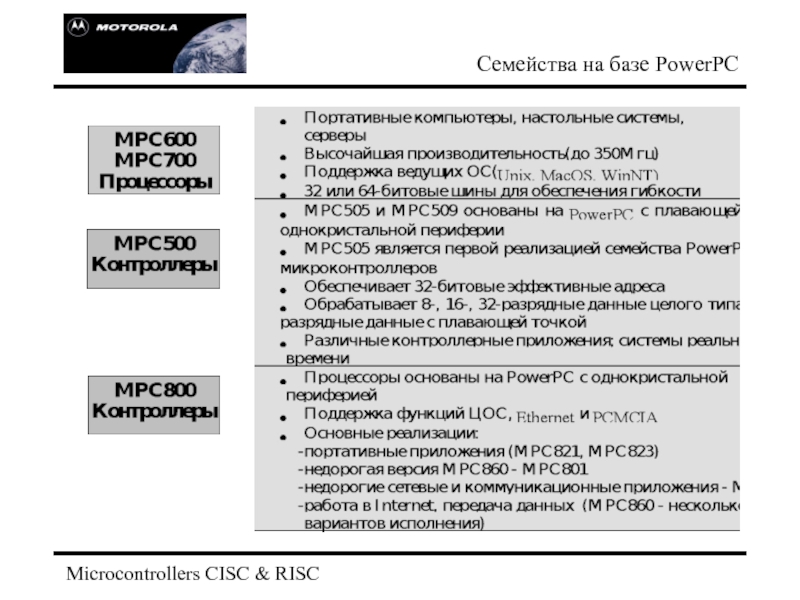

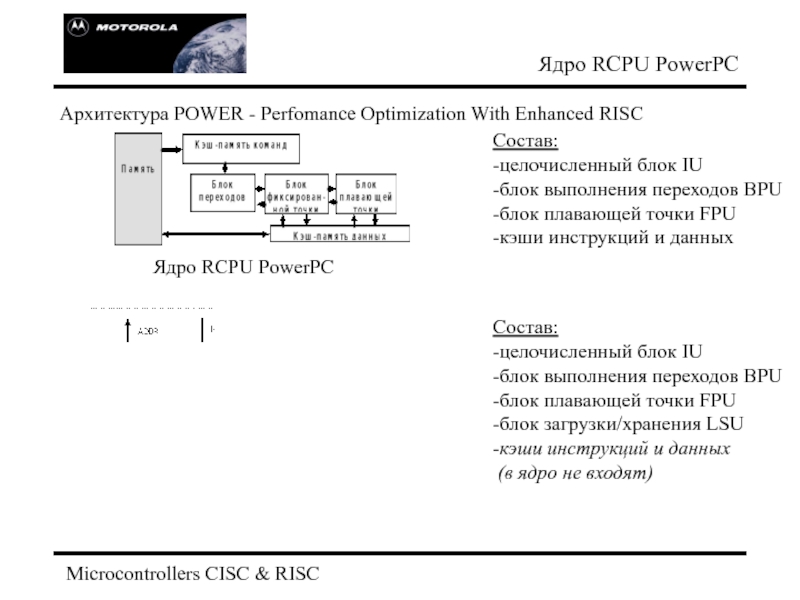

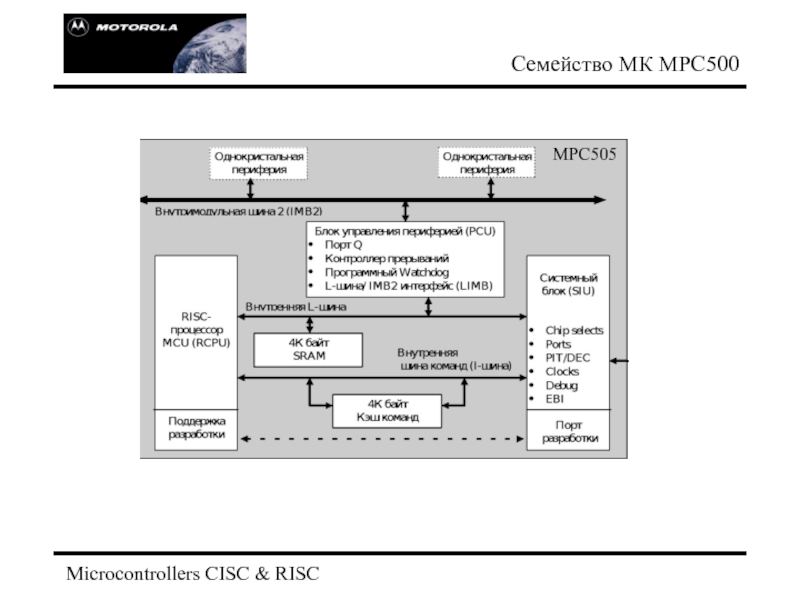

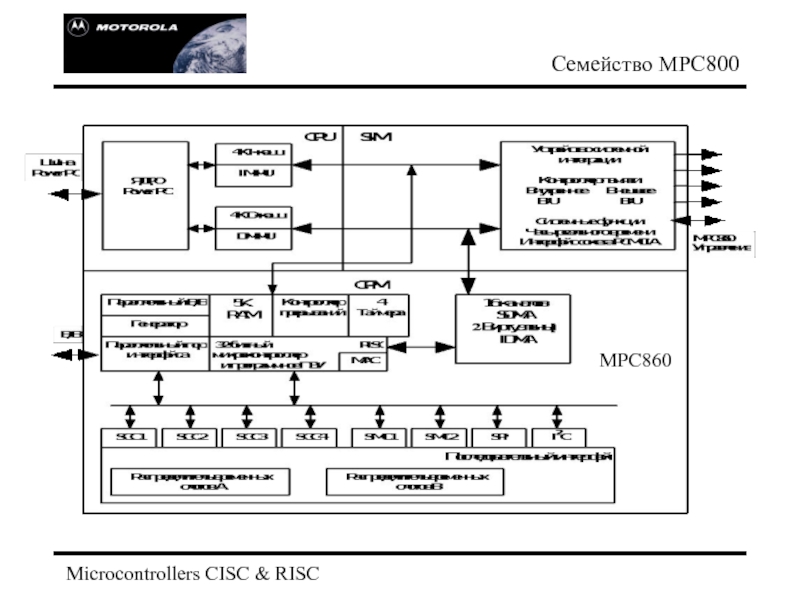

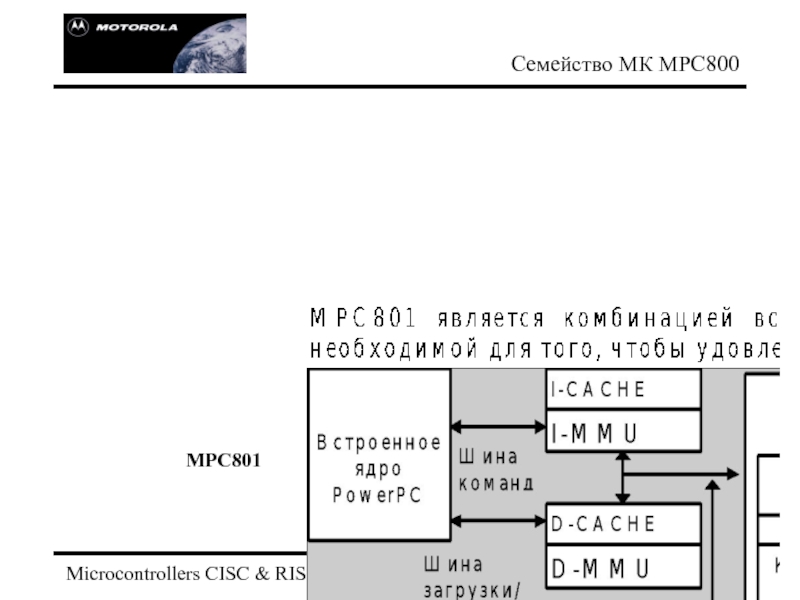

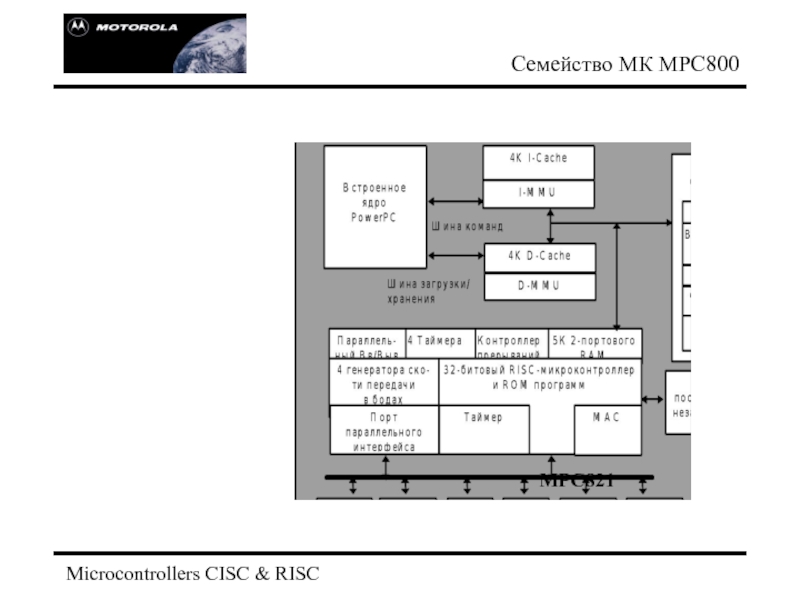

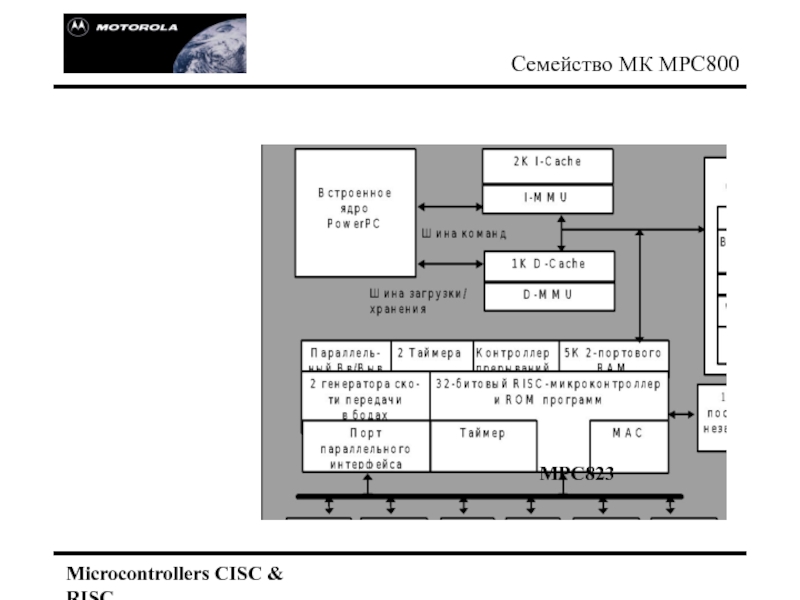

Архитектура Power (Perfomance Optimisation With Enhanced RISC), была переопределена

фирмой Моторола для однокристальных решений. В семействе МРС500 есть FPU,совместимый

со стандартом IEEE 754, в МРС800 отсутствует.